- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

Вычислительные комбинационные устройства

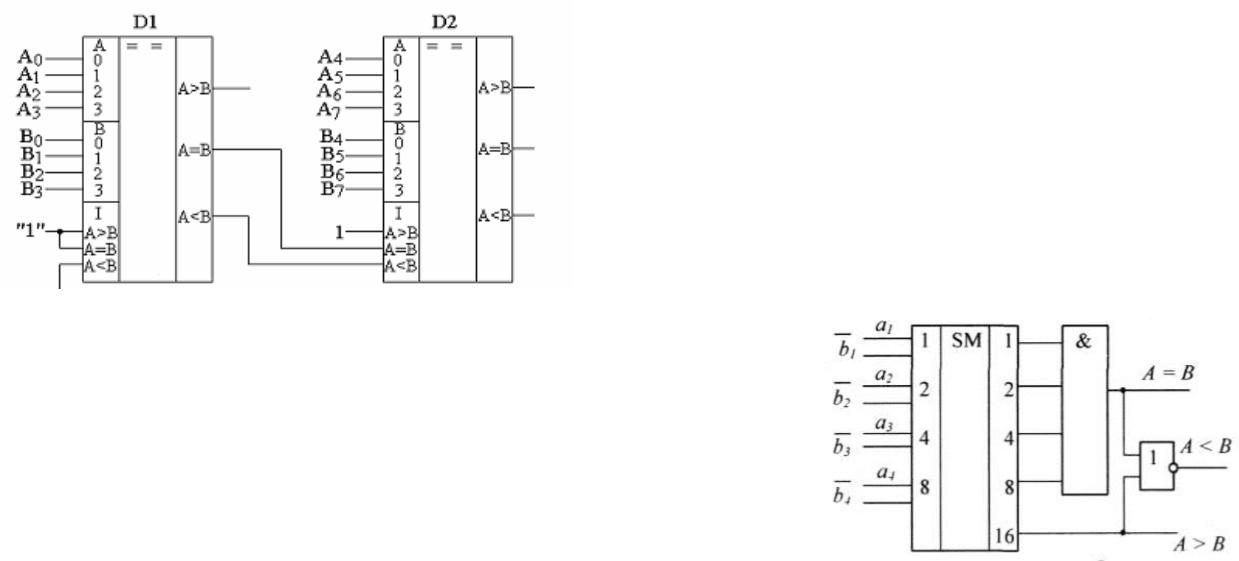

• При этом компараторы соединяют последовательно (каскадно) или параллельно (пирамидально).

При параллельном способе соединения компараторов быстродействие схемы сравнения значительно выше, чем при каскадном соединении, так как задержки в случае каскадного соединения суммируются.

Цифровой компаратор можно построить на сумматоре, подавая на один суммирующий вход прямой код числа А, на другой - инверсный код числа В. При А = В в четырех младших разрядах суммы формируются логические единицы, а при А > В единица формируется на выходе переноса.

Схемы контроля четности. Это ВКУ, с помощью которых можно осуществить простейший контроль правильности передачи данных. Пpимeняeтcя для выявлeния oшибoк, вызвaнныx пoмexaми в линии cвязи или в блoкax пaмяти. Meтoд ocнoвaн нa пoдcчeтe чиcлa eдиниц в пepeдaвaeмoй в линию (в пaмять) и принимаемой из линии (из памяти) пopции инфopмaции. Еcли чиcлo eдиниц чeтнoe - фyнкция чeтнocти P(arity) paвнa нyлю, если нечетное – единице. Функция нечетности – инверсия P

Вычислительные комбинационные

Функция четности P реализуется на сумматоре по модулю 2. Для устройства 4-разрядного двоичного числа X = x3x2x1x0

P = x3 x2 x1 x0.

Для n-разрядного числа X функция четности вычисляется суммированием по модулю 2 всех разрядов числа.

Пример - передача данных по линии связи. К555ИП5 - сумматор по модулю два. Он содержит внутри 8 логических элементов «Исключающее ИЛИ».

• Пycть пo n-пpoвoднoй линии cвязи пepeдaeтcя пapaллeльный двoичный кoд x(n-1),x(n-2),...,x1,x0, a пpинимaeтcя кoд x'(n-1),x'(n-2),..., x'1,x'0. Toгдa вeличинa P1 = 0 x0 x1 … x(n-1).

•Ha пpиeмнoм кoнцe линии cвязи P2 = x'0 x'1 ... x'(n-1) P1.

•После подстановки P1 и группировки P2 = (x0 x'0) (x1 x'1) (x2 x'2) ... (x(n-1) x'(n-1)).

•Еcли пepeдaчa пpoшлa бeз иcкaжeний, тo xi = x'i и xi x'i = 0, a P2=0. Пpи иcкaжeнии oднoгo и в oбщeм cлyчae нeчeтнoгo чиcлa бит фyнкция P2=1.

•Aнaлoгичнo пpoтeкaeт пpoцecc кoнтpoля и пpи пocлeдoвaтeльнoй пepeдaчe пo oднoй линии cвязи n бит данных и oднoгo битa чeтнocти. Тaкaя cxeмa иcпoльзyeтcя в кoммyникaциoнныx COM-пopтax кoмпьютepoв.

Вычислительные комбинационные устройства

•Арифметико-логические устройства (АЛУ) (англ. arithmetic and logic unit, ALU) – это ВКУ, которое под управлением устройства управления (УУ) выполняет арифметические и логические преобразования над данными, называемыми операндами. Разрядность операндов обычно называют размером или длиной машинного слова.

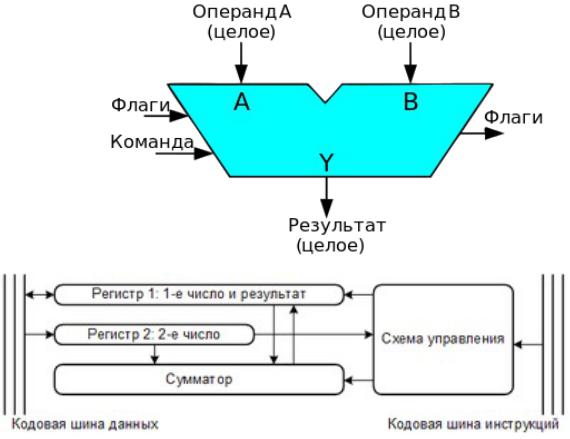

Обобщённая блок-схема арифметико-логического устройства (АЛУ). Стрелками указаны входные и выходные слова. Флаги — признаки (например, результата сравнения операндов) выполнения предыдущей операции (вход) и результата выполнения текущей операции (выход). В одноместных операциях, таких как инверсия битов слова или битовый сдвиг, второй операнд (B) не участвует в операции. Слово команды указывает необходимую операцию.

Функционально АЛУ состоит из двух регистров (Регистр1, Регистр 2), схемы управления и сумматора. Арифметическая операция суммирования выполняется по тактам:

1.Значения операнда 1, участвующего в арифметической операции по шине данных поступает в Регистр 1 или уже там находится.

2.Значения операнда 2, участвующего в арифметической операции по шине данных поступает в Регистр 2 или уже там находится.

Вычислительные комбинационные устройства

3.По шине инструкций поступает инструкция на выполнение операции в схему управления.

4.Данные из регистров поступают в сумматор, схема управления дает команду на выполнение сложения.

5.Результат сложения поступает в Регистр 1.

6.Признаки выполнения операции в АЛУ поступают в регистр флагов.

Работа АЛУ на операции вычитания:

7.Значения операнда 1, участвующего в арифметической операции, по кодовой шине данных поступает в Регистр 1.

8.Значения операнда 2, участвующего в арифметической операции, по кодовой шине данных поступает в Регистр 2.

9.По кодовой шине инструкций поступает инструкция на выполнение операции вычитания в схему управления.

10.Схема управления преобразует положительное число в отрицательное (в формате дополнительного кода). 11.Результат преобразования операнда поступает в сумматор.

12.Сумматор складывает два числа. 13.Результат сложения поступает в Регистр 1.

14.Результат операции АЛУ поступает в результирующий блок.

Все выполняемые в АЛУ операции можно разделить на следующие группы:

•операции двоичной арифметики для чисел с фиксированной точкой;

•операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой;

Вычислительные комбинационные устройства

•операции десятичной арифметики;

•операции индексной арифметики (при модификации адресов команд);

•операции специальной арифметики;

•операции над логическими кодами (логические операции);

•операции над алфавитно-цифровыми полями.

Современные ЭВМ общего назначения обычно реализуют операции всех приведённых выше групп. Микропроцессоры, микроЭВМ (микроконтроллеры) и специализированные ЭВМ часто не имеют аппаратуры арифметики чисел с плавающей точкой, десятичной арифметики и операций над алфавитно-цифровыми полями. В этом случае эти операции выполняются специальными подпрограммами.

К арифметическим операциям относятся сложение, вычитание, вычитание модулей («короткие операции») и умножение и деление («длинные операции»).

Группу логических операций составляют операции дизъюнкция (логическое ИЛИ), конъюнкция (логическое И) и часто сложение по модулю 2 (исключающее ИЛИ) над многоразрядными двоичными словами, сравнение кодов на равенство.

Специальные арифметические операции включают в себя нормализацию, арифметический сдвиг (сдвигаются только цифровые разряды, знаковый разряд остаётся на месте), логический сдвиг (знаковый разряд сдвигается вместе с цифровыми разрядами).

По способу действия над операндами АЛУ делятся на последовательные и параллельные.

Впоследовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами.

Впараллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

Вычислительные комбинационные устройства

•http://portal.tpu.ru:7777/SHARED/g/GREBENNIKOVVV/students/Tab4/Tab/08_Electronics_22_ALU.pdf

•https://www.microshemca.ru/IP3/

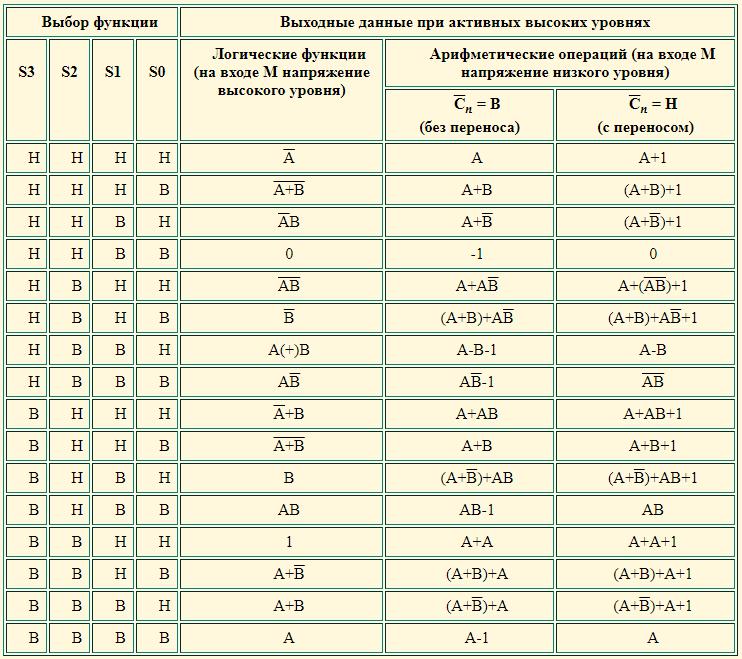

•Многие серии микросхем имеют в своем составе ИМС арифметико-логических устройств АЛУ, выполняющих над словами ряд логических и арифметических действий. Примером АЛУ может служить микросхема К155ИП3 или 564ИП3. Микросхема К155ИПЗ – быстродействующее АЛУ, которое выполняет 16 логических и 16 арифметических операций.

Взависимости от значений, поступающих на входы S и M, выполняется одна из 32 возможных операций. Арифметическое-логическое устройство может работать с высокими или низкими активными логическими уровнями. В зависимости от этого меняются знаки инверсии на входах и выходах, а также получаются различные таблицы соответствия логических и арифметических функций кодам выбора функции (входы S0—S3). В таблице показан выбор функций АЛУ при высоких активных уровнях операндов и выходов.

УГО 4-разрядного АЛУ К155ИПЗ

Вычислительные комбинационные устройства

Увеличение разрядности АЛУ: Последовательное - выход переноса C4 предыдущей ИС соединяется со входом C0 переноса последующей. При этом во всех АЛУ входы выбора операции и ее типа соединяются общей шиной.

Недостаток – низкое быстродействие. Параллельное – для этого типа подключения используются специальные микросхемы ускоренного переноса К155ИП4, аналогично ускоренному переносу для сумматоров. Выходы G и P АЛУ подключаем к аналогичным входам

G и P схемы УП, а выходы переноса последней ко входам переноса АЛУ. При этом входы М всех

микросхем должны быть объединены.