- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

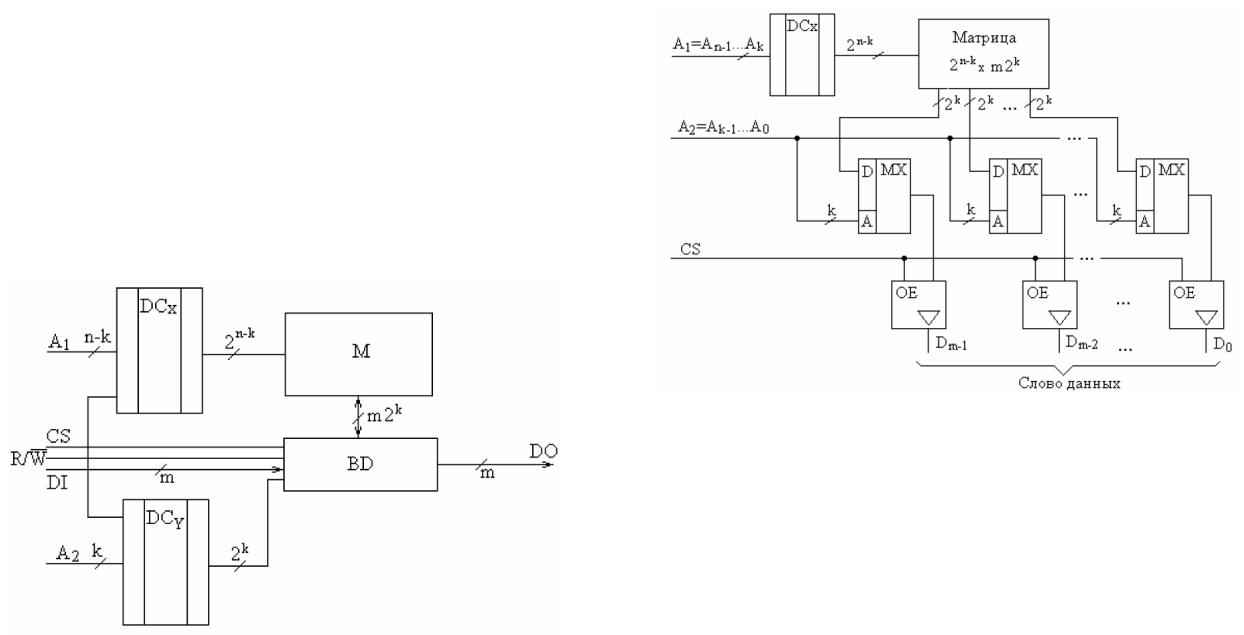

- ••Структура 3D позволяет резко упростить дешифраторы Схемотехника запоминающих устройств адреса с помощью двухкоординатной

- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

Схемотехника запоминающих устройств

•Запоминающим устройством (ЗУ) называют отдельное устройство ЭВМ, вычислительного комплекса или процессора, реализующее функцию памяти. Оно служит для записи, хранения и выдачи цифровой информации в процессе её обработки. В основе работы запоминающего устройства может лежать любой физический эффект, обеспечивающий приведение системы к двум или более устойчивым состояниям. Ниже рассматриваются только полупроводниковые ЗУ, реализуемые в интегральном исполнении.

Основные параметры ЗУ

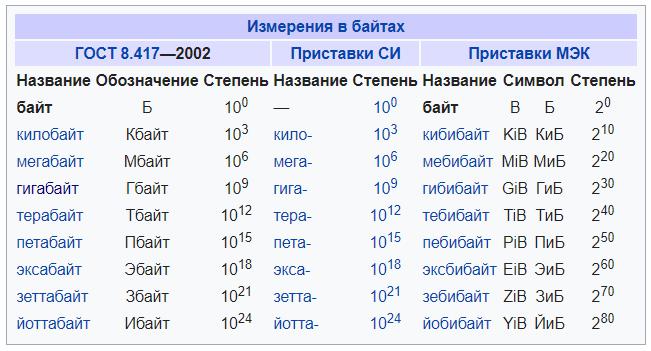

Информационная емкость — максимально возможный объем хранимой информации. Выражается в битах (бит), байтах (Б) или словах. Бит xpaнится в запоминающем элементе (ЗЭ), а слово—в запоминающей ячейке (ЗЯ), т.е. в группе ЗЭ, к которым возможно лишь одновременное обращение.

Байт равен 8 битам. Более крупными единицами хранения являются слова – 16, 32, 64, 128, 256 бит. Информационная емкость может выражаться в производных единицах.

Использование прописной буквы «Б» для обозначения байта соответствует требованиям ГОСТ и позволяет избежать путаницы между сокращениями от байт и бит.

В ГОСТ 8.417, кроме «бит», для бита нет однобуквенного обозначения, поэтому использование записи вроде «Мб» как синонима для «Мбит» не соответствует этому стандарту.

Схемотехника запоминающих устройств

•Бит xpaнится запоминающим элементом (ЗЭ), а слово—запоминающей ячейкой (ЗЯ), т.е. группой ЗЭ, к которым возможно лишь одновременное обращение. За одно обращение к ЗУ производится считывание или запись некоторой единицы данных (слова), различной для устройств разного типа.

•Организация ЗУ— произведение числа хранимых слов на их разрядность. Это произведение определяет информационную емкость ЗУ, однако при одной и той же информационной емкости организация ЗУ может быть различной. Например, память объемом 1 Мбайт может быть организована как 1М слов по 1 байту (1М*8), или 512К слов по 2 байта каждое (512К*16), или 256К слов по 4 байта (256К*32) и т.д.

•Быстродействие ЗУ оценивается временами считывания (чтения), записи и длительностью цикла чтения/записи.

•Время считывания — интервал между моментами подачи сигнала чтения и появления цифровой информации, соответствующей заданному адресу, на выходе ЗУ.

•Время записи — интервал после подачи сигнала записи, достаточный для установления ЗЭ (ЗЯ) в состояние, задаваемое входной цифровой информацией.

•Минимально допустимый интервал между последовательными чтениями или записями образует соответствующий цикл.

•Длительность цикла может превышать суммарное время чтения и записи, т. к. после этих операций может потребоваться время для восстановления необходимого начального состояния ЗУ.

•Удельная стоимость запоминающего устройства определяется отношением его стоимости к информационной емкости, т.е. определяется стоимостью бита хранимой информации.

•Потребляемая энергия (или рассеиваемая мощность) приводится для двух режимов работы кристалла: режима пассивного хранения информации и активного режима, когда операции записи и считывания выполняются с номинальным быстродействием. Кристаллы динамической МОП-памяти в резервном режиме потребляют примерно в десять раз меньше энергии, чем в активном режиме.

Схемотехника запоминающих устройств

•Классификация полупроводниковых ЗУ.

•ЗУ могут быть классифицированы по функциональному назначению, способу хранения информации, технологическому исполнению, способу обращения к массиву элементов памяти и другим признакам.

•По принципу действия различают полупроводниковые, магнитные и оптические ЗУ. Рассмотрим только полупроводниковые.

•По способу доступа к информации устройства памяти разделяют на адресные ЗУ, ЗУ с последовательным доступом и ассоциативные.

•В адресных ЗУ доступ к ячейке памяти обеспечивается с помощью адресного кода (т. е. доступ по коду номера ячейки).

•В ЗУ с последовательным доступом осуществляется последовательный просмотр всех ячеек памяти, располагающихся в последовательном порядке (образуя очередь), до тех пор, пока не произойдёт обращение к заданной ячейке.

•В ассоциативных ЗУ поиск и извлечение информации производятся по некоторому признаку самой информации, содержащемуся в хранимом слове, т. е. по содержанию (например, по выделенному тэгу (полю) слов). Основная область применения ассоциативного доступа к данным — сверхоперативная кэш- память.

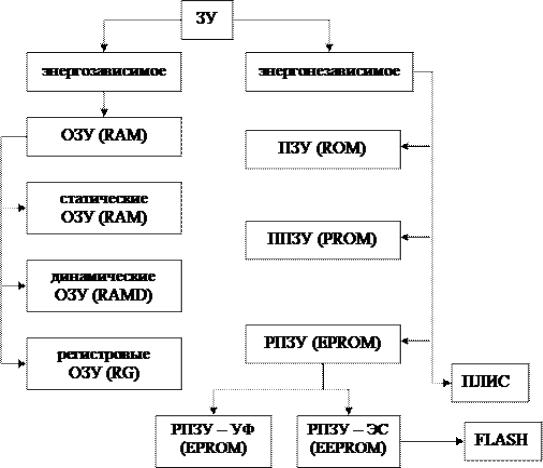

•По энергопотреблению ЗУ можно разделить на две группы:

энергозависимые – мощность от источника питания потребляется во всех режимах работы ЗУ;

энергонезависимые – записанная информация сохраняется и при отключенном источнике питания.

Схемотехника запоминающих устройств

•По функциональному назначению можно выделить следующие группы:

•1. Оперативные запоминающие устройства (ОЗУ, или RAM – Random-Access Memory). Обеспечивают запись, хранение, считывание информации во время ее обработки.

•2. Постоянные запоминающие устройства (ПЗУ, или ROM – Read-Only Memory). Предназначены для воспроизведения неизменной информации, записанной при изготовлении ЗУ.

•3. Программируемые постоянные запоминающие устройства (ППЗУ, или PROM – Programmable Read-Only Memory). Имеют возможность однократно быть запрограммированы электрическим путем по заданной программе с использованием специальных устройств – программаторов, при изготовлении или пользователем.

•4. Репрограммируемые постоянные запоминающие устройства (РПЗУ, или EPROM – Erasable Programmable Read Only Memory) с возможностью многократного электрического программирования.

РПЗУ бывают двух типов:

·РПЗУ-УФ или EPROM – с ультрафиолетовым стиранием и электрической записью;

·РПЗУ-ЭС или EEPROM – Electrically Erasable Programmable Read-Only Memory – с электрическим стиранием и записью. К последним относится и флэш-память.

Схемотехника запоминающих устройств

•5. Запоминающее устройство может быть реализовано на программируемой логической интегральной схеме (ПЛИС).

•ОЗУ делятся на статические (SRAM - Static RAM) и динамические (DRAM - Dynamic RAM).

•В статических ОЗУ запоминающими элементами являются триггеры, сохраняющие свое состояние, пока на ИМС подано питание и нет записи новых данных. Их достоинство – высокое быстродействие, но имеют меньшую емкость, чем динамические ОЗУ. Применяются в кэш-памяти.

•В динамических ОЗУ данные хранятся в виде зарядов конденсаторов, образуемых элементами МОП-структур. Они требуют периодической регенерации информации. Динамические ОЗУ характеризуются наибольшей информационной емкостью и невысокой стоимостью, поэтому именно они используются как основная оперативная память ЭВМ.

•Структуры адресных ЗУ

•Адресные ЗУ представлены в классификации постоянными и оперативными запоминающими устройствами. Многочисленные варианты этих ЗУ имеют много общего с точки зрения структурных схем. Общность структур особенно проявляется для статических ОЗУ и памяти типа ПЗУ. Для них наиболее характерны структуры 2D, 3D и 2DM.

•В структуре 2D запоминающие элементы ЗЭ организованы в прямоугольную матрицу размерностью

М= k * m,

•где М — информационная емкость памяти в битах;

•k — число хранимых слов;

•m — их разрядность.

Схемотехника запоминающих устройств

•Дешифратор адресного кода DC при наличии разрешающего сигнала CS активизирует одну из выходных линий, разрешая одновременный доступ ко всем элементам выбранной строки. Строка хранит слово, адрес которого соответствует номеру строки. Элементы одного столбца соединены вертикальной линией — внутренней линией данных (разрядной линией, линией записи/считывания).

•Элементы столбца хранят одноименные биты всех слов. Направление обмена определяется усилителями чтения/записи под воздействием сигнала R/W (Read — чтение, Write — запись).

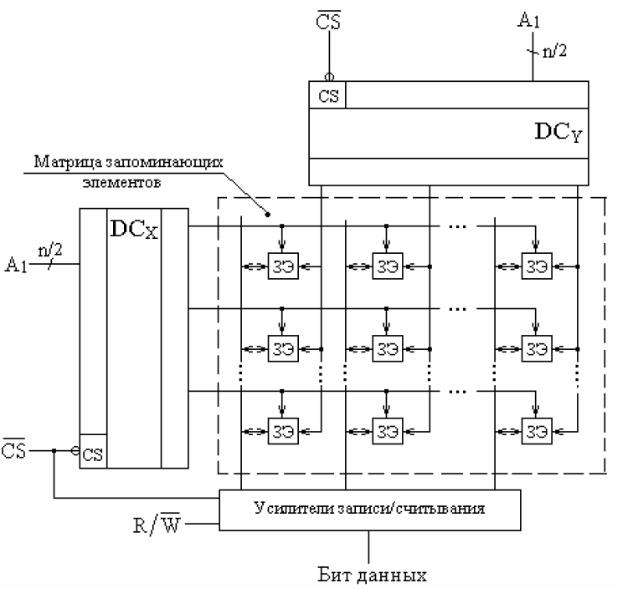

•Структура 3D позволяет резко упростить дешифраторы Схемотехника запоминающих устройств адреса с помощью двухкоординатной выборки запоминающих элементов. Принцип двухкоординатной выборки поясняется на примере ЗУ одноразрядной организации.

•Здесь код адреса разрядностью n делится на две половины, каждая из которых декодируется отдельно. Выбирается запоминающий элемент, находящийся на пересечении активных линий выходов обоих дешифраторов.

•Таких пересечений будет

2n/2 * 2n/2 = 2n.

•Суммарное число выходов обоих дешифраторов составляет

2n/2 + 2n/2 =2 * 2n/2 =2(n/2)+1,

•что гораздо меньше, чем 2n при реальных значениях n.

•Уже для ЗУ небольшой емкости видна эта существенная разница: для структуры 2D при хранении 1К ЗЭ потребовался бы дешифратор с 210 = 1024 выходами, тогда как для структуры типа 3D нужны два дешифратора с 25 = 32 выходами каждый. Недостатком структуры 3D в первую очередь является усложнение элементов памяти, имеющих двухкоординатную выборку.

Схемотехника запоминающих устройств

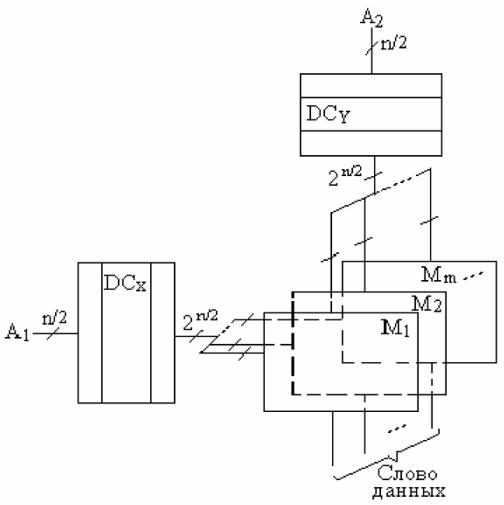

•Структура типа 3D, показанная на рисунке для ЗУ с одноразрядной организацией, может применяться и в ЗУ с многоразрядной организацией, приобретая при этом "трехмерный" характер.

•В этом случае несколько матриц управляются от двух дешифраторов, относительно которых они включены параллельно. Каждая матрица выдает один бит адресованного слова, а число матриц равно разрядности хранимых слов.

•В структурах типа 2DM (2D модифицированная) сочетаются достоинства обеих рассмотренных структур — упрощается дешифрация адреса и не требуются запоминающие элементы с двухкоординатной выборкой.

•Запоминающие устройства типа ПЗУ структуры 2DM для матрицы запоминающих элементов с адресацией от дешифратора DCx имеет как бы характер структуры 2D: возбужденный выход дешифраторавыбирает целую строку. Однако в отличие от структуры 2D, длина строкине равна разрядности хранимых слов, а многократно ее превышает. При этом число строк матрицы уменьшается и, соответственно, уменьшается число выходов дешифратора. Для выбора одной из строк служат не все разряды адресного кода, а их часть An-i... Ak. Остальные разряды адреса (от Аk-1 до Ао) используются, чтобы выбрать необходимое слово из того множества слов, которое содержится в строке. Это выполняется с помощью мультиплексоров, на адресные входы которых подаются коды Аk-1...Ао.

Схемотехника запоминающих устройств

Длина строки равна m2k, где m — разрядность хранимых слов. Из каждого "отрезка" строки длиной 2k мультиплексор выбирает один бит. На выходах мультиплексоров формируется выходное слово. По разрешению сигнала CS, поступающего на входы ОЕ управляемых буферов с тремя состояниями, выходное слово передается на внешнюю шину.

На нижнем рисунке в более общем виде структура 2DM показана для ЗУ типа ОЗУ с операциями чтения и записи. Из матрицы М по-прежнему считывается "длинная" строка.

Данные в нужный отрезок этой строки записываются (или считываются из нее) управляемыми буферами данных BD, воспринимающими выходные сигналы второго дешифратора DCy, и выполняющими не только

функции мультиплексирования, но и функции изменения направления передачи данных под воздействием сигнала R/W .

Постоянные запоминающие устройства

•ПЗУ (ROM) предназначены для постоянного, энергонезависимого хранения информации.

По способу записи ПЗУ классифицируют следующим образом:

однократно программируемые маской на предприятии-изготовителе;

однократно программируемые пользователем с помощью специальных устройств, называемых программаторами – ППЗУ (PROM) ;

перепрограммируемые, или репрограммируемые ПЗУ – РПЗУ (EPROM, EEPROM).

•Масочные ПЗУ

•Программирование масочных ПЗУ происходит в процессе изготовления БИС. Обычно на кристалле полупроводника вначале создаются все запоминающие элементы (ЗЭ), а затем на заключительных технологических операциях с помощью фотошаблона слоя коммутации реализуются связи между линиями адреса, данных и собственно запоминающим элементом. Этот шаблон (маска) выполняется в соответствии с пожеланиями заказчика по картам заказа. Такие ПЗУ изготавливаются на основе матриц диодов, биполярных или МОП-транзисторов.

Масочные ПЗУ на основе диодной матрицы:

Здесь горизонтальные линии – адресные, а вертикальные – это линии данных, с них в данном случае снимаются 8-разрядные двоичные числа. В данной схеме ЗЭ – это условное пересечение линии адреса и линии данных.