- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

- ••Структура 3D позволяет резко упростить дешифраторы Схемотехника запоминающих устройств адреса с помощью двухкоординатной

- •Схемотехника запоминающих устройств

- •Схемотехника запоминающих устройств

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Постоянные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

- •Оперативные запоминающие устройства

Оперативные запоминающие устройства

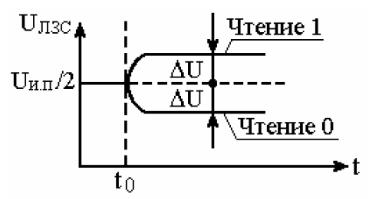

•При считывании нуля к ЛЗС подключается емкость Сз, имевшая нулевой заряд. Часть заряда емкости Сл перетекает в емкость Сз, и напряжения на них уравниваются. Потенциал ЛЗС снижается на величину ΔU, которая и является сигналом, поступающим на усилитель считывания.

•При считывании единицы, напротив, напряжение на Сз составляло вначале величину Uи.п. и превышало напряжение на ЛЗС. При подключении Сз к ЛЗС часть заряда стекает с запоминающей емкости в Сл и напряжение на ЛЗС увеличивается на ΔU. Графики сигналов при считывании нуля и единицы показаны на рисунке.

Всилу неравенства Сз << Сл сигнал ΔU оказывается слабым. Кроме того, считывание является разрушающим — подключение запоминающей емкости к ЛЗС изменяет ее заряд.

Для преодоления указанных недостатков принимают следующие меры:

• для восстановления заряда элемента памяти вводят циклы регенерации;

• увеличивают емкость Сэ элемента памяти, например, путем использования диэлектрика с бо́льшим значением диэлектрической проницаемости;

• уменьшают емкость Cл разрядной шины в два раза путем разделения ее на две подшины;

• для считывания используют высокочувствительные дифференциальные усилители с положительной обратной связью – усилители-регенераторы.

Мультиплексирование шины адреса.

Особенностью динамических ЗУ является мультиплексирование шины адреса. Адрес делится на два полуадреса, один из которых представляет собою адрес строки, а другой — адрес столбца матрицы ЗЭ. Полуадреса подаются на одни и те же выводы корпуса ИС поочередно. Подача адреса строки сопровождается соответствующим стробом RAS (Row Address Strobe), а адреса столбца — стробом CAS (Column Address Strobe).

Оперативные запоминающие устройства

• Причиной мультиплексирования адресов служит стремление уменьшить число выводов корпуса ИС и тем самым удешевить ее, а также то обстоятельство, что полуадреса и сигналы RAS и CAS в некоторых режимах и схемах используются различно (например, в режимах регенерации адрес столбца вообще не нужен). Сокращение числа внешних выводов корпуса для динамических ЗУ особенно актуально, т. к. они имеют максимальную емкость и, следовательно, большую разрядность адресов.

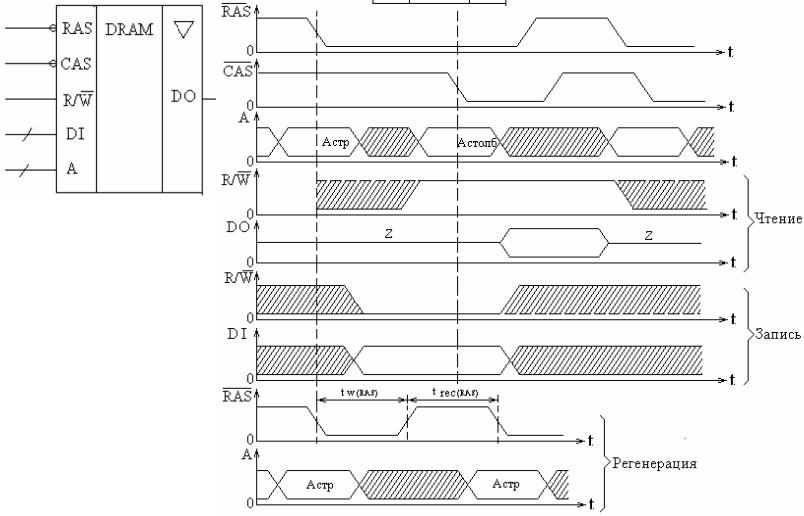

Внешняя организация, временные диаграммы и функциональная схема динамических ОЗУ

Циклы обращения к ОЗУ начинаются сигналом RAS и запаздываю-

щим относительно него сигналом CAS .

Отрицательным фронтам этих сигналов соответствуют области подачи на адресные линии ОЗУ полуадресов, адресующих строки и столбцы матрицы соответственно. Согласно выполняемой операции (сигналу R/W ) либо вырабатываются выходные данные DO, либо принимаются входные данные DI.

В циклах регенерации подаются только импульсные сигналы RAS и адреса строк. Области безразличных значений сигналов на рисунке заштрихованы.

Оперативные запоминающие устройства

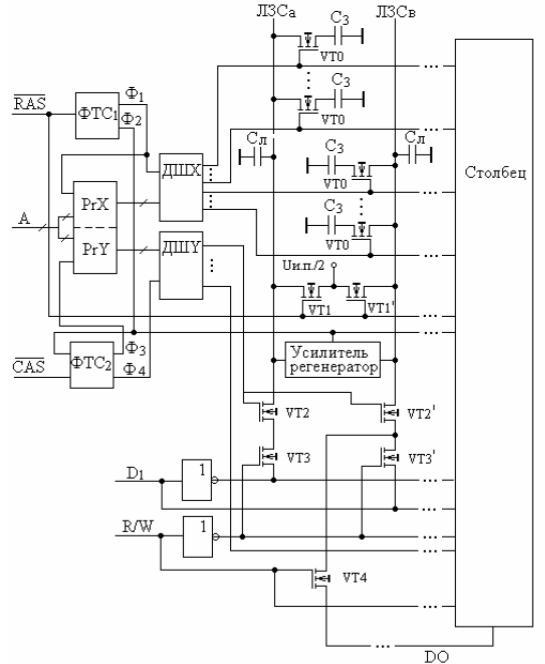

В схеме динамического ОЗУ один из столбцов матрицы раскрыт полностью, другие столбцы аналогичны ему. В схеме блок ФТС — формирователь тактирующих сигналов.

В исходном состоянии (до обращения к ОЗУ) сигнал RAS пассивен, т е. имеет высокий уровень, который замыкает ключи на транзисторах

VT1и VT1' и подает напряжение Uи.п./2 на полушины записи-считывания ЛЗСа и ЛЗСв для их предзаряда.

При обращении к ЗУ активизируется сигнал RAS одновременно с подачей по шине адреса А первого полуадреса (адреса строки). При этом ключи на транзисторах VT1и VT1' размыкаются и линии записи- считывания изолируются от источника напряжения Uи.п./2, а формирователь ФТС1 вырабатывает пару последовательных сигналов Ф1 и Ф2. Тактирующий сигнал Ф1 разрешает загрузку регистра РгХ и работу дешифратора ДШХ, одна из выходных линий которого возбуждается и выбирает все ЗЭ строки, адрес которой содержится в регистре РгХ.

Оперативные запоминающие устройства

•В разрыв между секциями ЛЗСa и ЛЗСв включен усилитель-регенератор, для которого подключение ЗЭ, хранящего единицу или ноль, создает дисбаланс входных сигналов.

•Второй тактирующий сигнал Ф2 снимает сигнал "Подготовка" с усилителей-регенераторов, и они срабатывают, формируя в своих точках входов-выходов полные уровни сигналов, что восстанавливает состояния ЗЭ выбранной строки.

•Для последующих операций чтения или записи требуется наличие сигнала CAS, разрешающего формирователю ФТС2 формирование второй пары тактирующих сигналов ФЗ и Ф4. Сигнал ФЗ загружает в PгY адрес столбца, а Ф4 активизирует дешифратор ДШУ, вследствие чего открываются ключи на транзисторах VT2 и VT2' выбранного столбца.

•В зависимости от сигнала R/W , линии ЛЗС подключаются либо к выходной шине данных (через ключ на транзисторе VT4 при R/W = 1), либо к линии входных данных (через ключи на транзисторах VT3 и VT3' при R/W=0).

•Для операции регенерации, целиком проходящей внутри ОЗУ, связь с внешними выводами не требуется, так как она не сопровождается выдачей данных на выходные буферы. Поэтому для нее достаточно подачи только сигнала RAS (совместно с адресами регенерируемых строк) и выработки тактирующих сигналов Ф1 и Ф2.

•При подаче на вход управления нагрузкой усилителя сигнала Ф2 = 1 во всех элементах памяти, подключенных к выбранной строке, происходит восстановление (регенерация) заряда. Поэтому в динамическом ОЗУ используется способ строчной регенерации зарядов элементов памяти. При этом реализуются циклы чтения всех строк без выдачи данных. На входы ЗУ подаются только адреса строк и стробы RAS.

•Для проведения регенерации используются контроллеры динамического ОЗУ.

Оперативные запоминающие устройства

•Модули памяти ОЗУ большой информационной емкости

•Требования к информационной емкости ОЗУ, как правило значительно превосходят возможности одной ИМС памяти как в отношении разрядности слов, так и их числа. Поэтому при построении ЗУ ИМС объединяют в модули, которые вместе с регистрами, дешифраторамии устройствами управления образуют функционально-законченный блок (модуль) ОЗУ.

•Для наращивания разрядности слов в ИМС памяти объединяют одноименные адресные и управляющие входы. Образованную таким соединением часть модуля ЗУ называют субмодулем (СМ).

Записывают слова в субмодуль по входам DIn-1 … DI0, считывают с выходов DOn-1 … DO0 всеми разрядами одновременно, при условии, что на

входе CS присутствует сигнал логического нуля. В том случае, если на входе CS сигнал логической единицы, СМ находится в режиме хранения и не реагирует на адресные и управляющие сигналы.

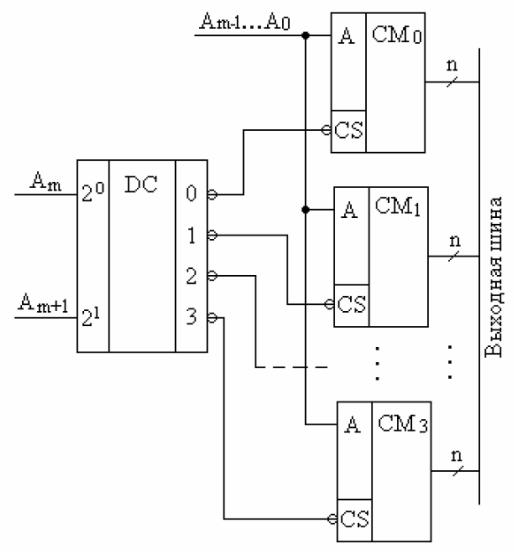

Для наращивания числа хранимых слов СМ объединяют в модуль путем соединения одноименных выводов СМ, за исключением выводов

CS, которые подключают к выходам дешифратора кода адреса. На входы дешифратора подают дополнительные (старшие) разряды кода адреса.

Оперативные запоминающие устройства

•Пример объединения в модуль четырех субмодулей, что обеспечивает в четыре раза большую информационную емкость по сравнению с информационной емкостью СМ.

•Для этого модуля код адреса имеет m+1 разрядов. Два старших разряда m+1 и m определяют тот субмодуль, к которому происходит обращение при записи информации

или ее считывания. Так при Аm+1Аm=00 дешифратор формирует сигнал 0 на нулевом выходе. При этом

открывается доступ к субмодулю СМ0. При Аm+1Аm=01 открывается доступ к СМ1 и т.д. ОЗУ с такой адресацией называют ОЗУ страничного типа.

•В свою очередь страницы ОЗУ могут быть объединены в банки ОЗУ путем дополнительной дешифрации еще более старших адресов памяти.