Министерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР) Кафедра безопасности информационных систем (БИС)

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Отчет по лабораторной работе №1 по дисциплине «Электроника и схемотехника 2»

Вариант №9

Студент гр. 731-2

____________

05.05.2023

Руководитель Доцент каф. КИБЭВС, к.т.н., доцент

_________ _____________ А.Н. Мальчуков

05.05.2023

Томск 2023

|

СОДЕРЖАНИЕ |

|

Введение................................................................................................................... |

3 |

|

1 |

УСТРОЙСТВО 2И ............................................................................................... |

4 |

2 |

УСТРОЙСТВО 2ИЛИ.......................................................................................... |

6 |

3 |

УСТРОЙСТВО 2искл.ИЛИ................................................................................. |

8 |

4 |

УСТРОЙСТВО 2И-НЕ....................................................................................... |

10 |

5 |

УСТРОЙСТВО 2ИЛИ-НЕ ................................................................................. |

12 |

6 |

УСТРОЙСТВО 2искл.ИЛИ-НЕ ........................................................................ |

14 |

7 |

УСТРОЙСТВО СОГЛАСНО ВАРИАНТУ 9 .................................................. |

16 |

Заключение ............................................................................................................ |

19 |

|

2

Введение

Цель работы: изучить основные инструменты САПР QuartusII и

научиться моделировать в ней работу схем на основе простых логических

элементов.

Постановка задачи:

1.собрать на холсте или разных холстах .bdf и промоделировать работу схем 2И, 2ИЛИ, 2искл.ИЛИ, 2И-НЕ, 2ИЛИ-НЕ и 2искл ИЛИ-НЕ в двух режимах.

2.описать логические элементы из п.1 на HDL и промоделировать эти

схемы.

3.собрать схему на отдельном холсте .bdf для выражения из таблицы согласно варианту.

4.промоделировать её работу в двух режимах. Сделать предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему.

5.выполнить пункты 3-4 с помощью HDL согласно варианту 9.

6.составить таблицу истинности для выражения из таблицы согласно варианту. Сверить результаты моделирования с составленной таблицей истинности.

7.написать выводы о проделанной работе.

3

1 УСТРОЙСТВО 2И

Для логического элемента 2И была собрана функциональная схема,

представленная на рисунке 1.1.

Рисунок 1.1 – Функциональная схема логического элемента 2И

Была составлена таблица истинности для логического элемента 2И

представленная в таблице 1.1.

Таблица 1.1 - Таблица истинности для логического элемента 2И

|

Вход |

Выход |

|

A |

|

B |

C |

0 |

|

0 |

0 |

1 |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

Формула схемы имеет следующий вид: C = A ∙ B.

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional». Результат представлен на рисунках 1.2 - 1.3

соответственно.

Рисунок 1.2 – Моделирование логического элемента 2И в режиме «Timing»

4

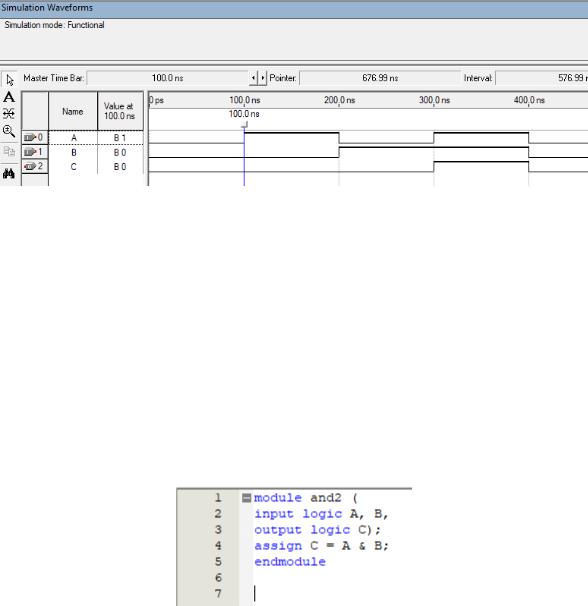

Рисунок 1.3 – Моделирование логического элемента 2И в режиме

«Functional»

Из-за того, что в режиме работе «Timing» учитывает задержка на логических элементах, происходят выходы за границы интервала.

Также был написан код на языке описания аппаратуры SystemVerilog,

представленный на рисунке 1.4. Во второй строчке обозначены точки входа A

и B. В третьей строчке обозначена точка выхода C. Логический элемент 2И

описывается четвертой строчкой после оператора «assign».

Рисунок 1.4 – Код на языке описания аппаратуры SystemVerilog логического элемента 2И

5

2 УСТРОЙСТВО 2ИЛИ

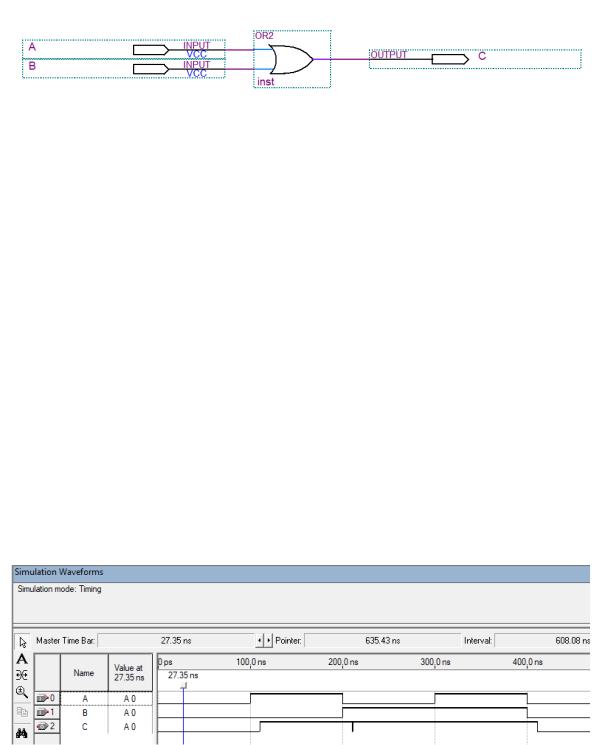

Для логического элемента 2ИЛИ была собрана функциональная схема,

представленная на рисунке 2.1.

Рисунок 2.1 – Функциональная схема логического элемента 2ИЛИ Была составлена таблица истинности для логического элемента 2ИЛИ

представленная в таблице 2.1.

Таблица 2.1 - Таблица истинности для логического элемента 2ИЛИ

|

Вход |

Выход |

|

A |

|

B |

C |

0 |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

1 |

Формула схемы имеет следующий вид: C = A B.

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional». Результат представлен на рисунках 2.2-2.3

соответственно.

Рисунок 2.2 – Моделирование логического элемента 2ИЛИ в режиме

«Timing» 6

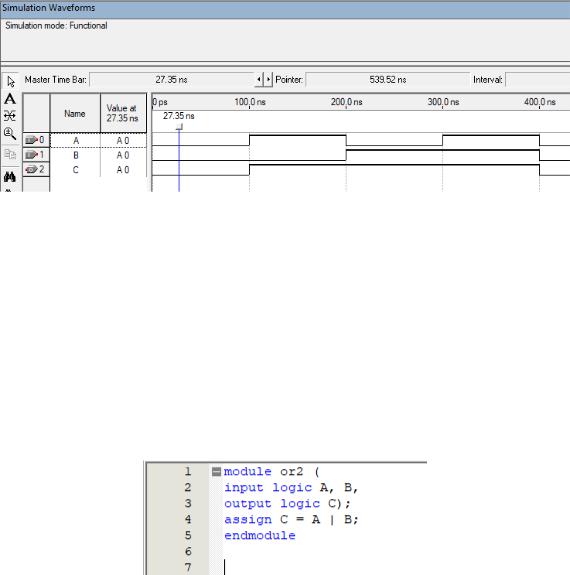

Рисунок 2.3 – Моделирование логического элемента 2ИЛИ в режиме

«Functional»

Из-за того, что в режиме работе «Timing» учитывает задержка на логических элементах, происходят выходы за границы интервала.

Также был написан код на языке описания аппаратуры SystemVerilog,

представленный на рисунке 2.4. Во второй строчке обозначены точки входа A

и B. В третьей строчке обозначена точка выхода C. Логический элемент 2ИЛИ описывается четвертой строчкой после оператора «assign».

Рисунок 2.4 – Код на языке описания аппаратуры SystemVerilog логического элемента 2ИЛИ

7

3 УСТРОЙСТВО 2искл.ИЛИ

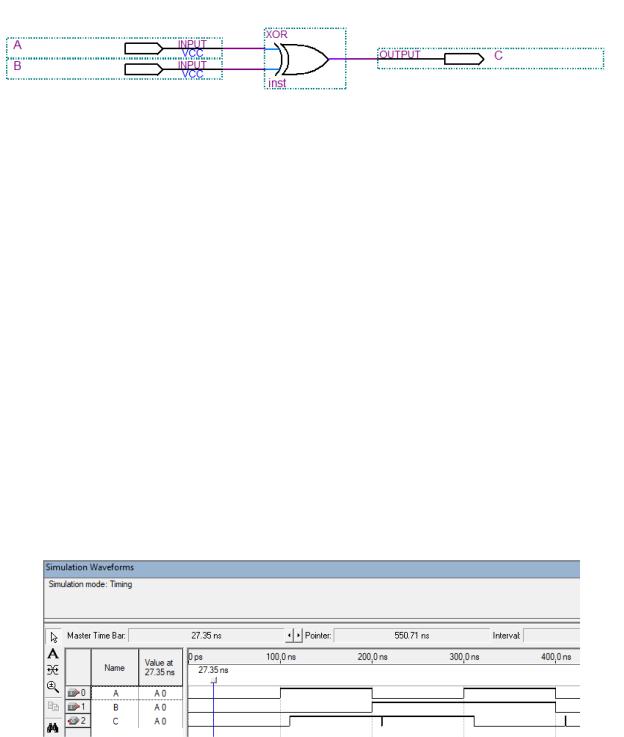

Для логического элемента 2искл.ИЛИ была собрана функциональная схема, представленная на рисунке 3.1.

Рисунок 3.1 – Функциональная схема логического элемента 2искл.ИЛИ Была составлена таблица истинности для логического элемента

2искл.ИЛИ, представленная в таблице 3.1.

Таблица 3.1 - Таблица истинности для логического элемента 2искл.ИЛИ

|

Вход |

Выход |

|

A |

|

B |

C |

0 |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

0 |

Формула схемы имеет следующий вид: C = A B.

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional». Результат представлен на рисунках 3.2-3.3

соответственно.

Рисунок 3.2 – Моделирование логического элемента 2искл.ИЛИ в режиме

«Timing»

8

Рисунок 3.3 – Моделирование логического элемента 2искл.ИЛИ в режиме

«Functional»

Из-за того, что в режиме работе «Timing» учитывает задержка на логических элементах, происходят выходы за границы интервала.

Также был написан код на языке описания аппаратуры SystemVerilog,

представленный на рисунке 3.4. Во второй строчке обозначены точки входа A

и B. В третьей строчке обозначена точка выхода C. Логический элемент 2искл ИЛИ описывается четвертой строчкой после оператора «assign».

Рисунок 3.4 – Код на языке описания аппаратуры SystemVerilog логического элемента 2искл.ИЛИ

9

4 УСТРОЙСТВО 2И-НЕ

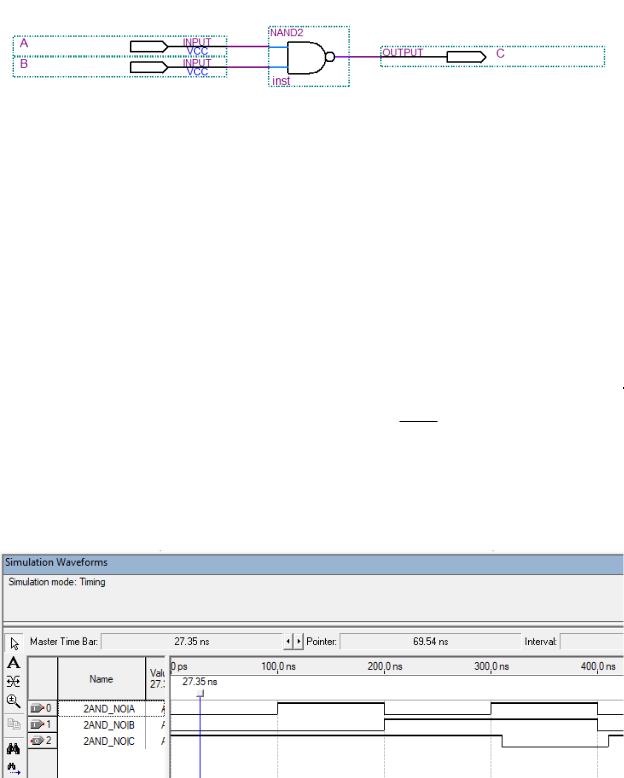

Для логического элемента 2И-НЕ была собрана функциональная схема,

представленная на рисунке 4.1.

Рисунок 4.1 – Функциональная схема логического элемента 2И-НЕ Была составлена таблица истинности для логического элемента 2И-НЕ,

представленная в таблице 4.1.

Таблица 4.1 - Таблица истинности для логического элемента 2И-НЕ

|

Вход |

Выход |

|

A |

|

B |

C |

0 |

|

0 |

1 |

1 |

|

0 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

0 |

Формула схемы имеет следующий вид: C = A ∙ B.

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional». Результат представлен на рисунках 4.2-4.3

соответственно.

Рисунок 4.2 – Моделирование логического элемента 2И-НЕ в режиме

10