Министерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР) Кафедра безопасности информационных систем (БИС)

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

Отчет по лабораторной работе №3

по дисциплине «Электроника и схемотехника 2» Вариант №9

Студент гр. 731-2

_____________

21.05.2023

Руководитель Доцент каф. КИБЭВС, к.т.н., доцент

_________ _____________ А.Н. Мальчуков

21.05.2023

Томск 2023

|

ОГЛАВЛЕНИЕ |

|

Введение................................................................................................................... |

3 |

|

1 РЕАЛИЗАЦИЯ ВЕДОМОГО ПАРАЛЛЕЛЬНОЙ ШИНЫ .............................. |

5 |

|

1.1 |

Таблица истинности для реализации ведомого параллельной шины ...... |

5 |

1.2 |

Функциональная схема.................................................................................. |

6 |

1.3 |

Моделирование функциональной схемы..................................................... |

6 |

1.4 |

Описание функциональных схем на HDL ................................................... |

7 |

2 РЕАЛИЗАЦИЯ ВЕДУЩЕГО ПОСЛЕДОВАТЕЛЬНОЙ ПЕРЕДАЧИ |

|

|

ДАННЫХ МЛАДШИМИ РАЗЯРДАМИ ВПЕРЕД НА ОСНОВЕ |

|

|

СДВИГАЮЩЕГО РЕГИСТРА С АСИНХРОННЫМ СБРОСОМ .................. |

10 |

|

2.1 |

Таблица истинности для ведущего последовательной передачи данных |

|

младшими разрядами вперед на основе сдвигающего регистра с |

|

|

асинхронным сбросом. ...................................................................................... |

10 |

|

2.2 |

Функциональная схема................................................................................ |

11 |

2.3 |

Моделирование функциональной схемы................................................... |

12 |

2.4 |

Описание функциональной схемы на HDL............................................... |

14 |

Заключение ............................................................................................................ |

19 |

|

2

Введение

Цель работы: научиться применять триггеры, регистры и счётчики. Постановка задачи:

1. используя таблицу истинности согласно вариантам определить каким образом, будет реализовано преобразование входных данных согласно задаче из варианта. Для данной работы используется таблица истинности из задачи

9-го варианта. Также необходимо определить каким способом будет реализовано преобразование входных данных: по формулам СДНФ/СКНФ, с помощью мультиплексора или дешифратора.

2.собрать схему на холсте .bdf, согласно варианту №9, а именно для ведомого параллельной шины с синхронным сбросом. Промоделировать работу схемы в двух режимах. При моделировании работы схемы необходимо подать на неё минимум 4-ре различные входные комбинации согласно таблице истинности задачи №9. Сделать предположение почему возникает разница в результатах моделирования разных режимов, а также сверить результаты моделирования с таблицей истинности.

3.повторить пункт 2 используя HDL согласно варианту №9, а именно на

System Verilog v2.

4.собрать схему на холсте .bdf, согласно варианту №9, а именно для ведущего последовательной передачи данных младшими разрядами вперед на основе сдвигающего регистра с асинхронным сбросом. Промоделировать работу схемы в двух режимах. При моделировании работы схемы необходимо подать на неё минимум 4-ре различные входные комбинации согласно таблице истинности задачи №9. Сделать предположение почему возникает разница в результатах моделирования разных режимов, а также сверить результаты моделирования с таблицей истинности.

5.повторить пункт 4, только для описания устройств вместо схем, используя HDL согласно варианту №9, а именно на VHDL.

3

6. написать выводы о проделанной работе.

4

1 РЕАЛИЗАЦИЯ ВЕДОМОГО ПАРАЛЛЕЛЬНОЙ ШИНЫ

1.1 Таблица истинности для реализации ведомого параллельной шины

Для реализации ведомого параллельной шины была взята таблица истинности, представленная в таблице 1.1, задачи согласно варианту, а именно

варианту №9.

Таблица 1.1 –Таблица истинности для ведомого параллельной шины

|

|

Входы |

|

|

|

|

Выходы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x4 |

x3 |

x2 |

x1 |

x0 |

ST2 |

ST1 |

SP2 |

|

SP1 |

FB |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

5

1.2 Функциональная схема

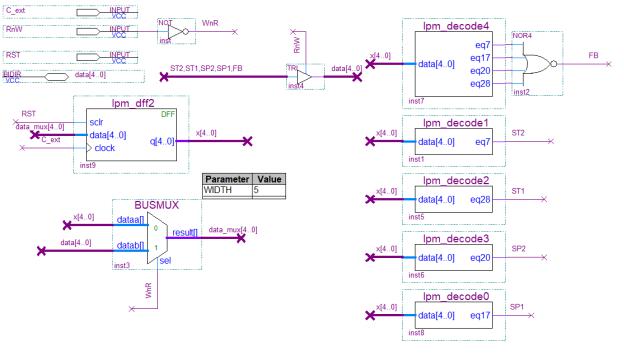

Функциональная схема реализации ведомого параллельной шины согласно варианту №9, а именно присутствует синхронный сброс. Данная схема реализована с помощью дешифраторов. Дешифраторы с выходами ST2, ST1, SP2, SP1 выполнены «по единицам», дешифратор с выходом FB

выполнен «по нулям». Функциональная схема построенных устройств представлена на рисунке 1.1.

Рисунок 1.1 – Функциональная схема

1.3 Моделирование функциональной схемы

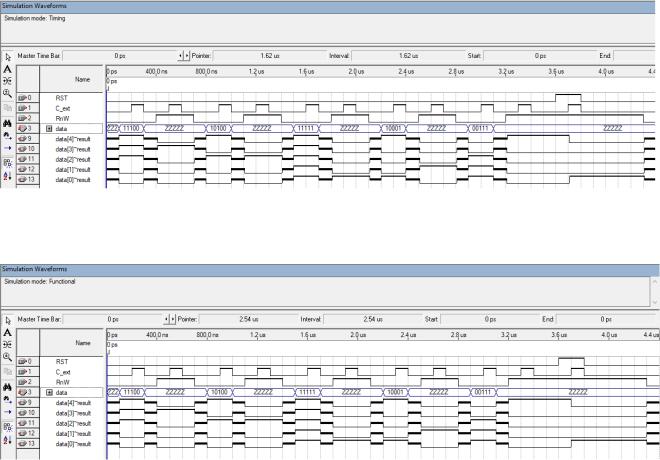

Далее было проведено моделирование построенной схемы в режимах «Timing» и «Functional». Комбинация входных значений x4, x3, x2, x1, x0 для моделирования были выбраны следующие: (1,1,1,0,0), (1,0,1,0,0), (1,1,1,1,1), (1,0,0,0,1), (0,0,1,1,1).

6

Рисунок 1.2 – Моделирование функциональной схемы в режиме «Timing»

Рисунок 1.3 – Моделирование функциональной схемы в режиме «Functional»

Из-за того, что в режиме работе «Timing» учитывается задержка на элементах, происходят выходы за границы интервала. Результат моделирования совпал с таблицей истинности.

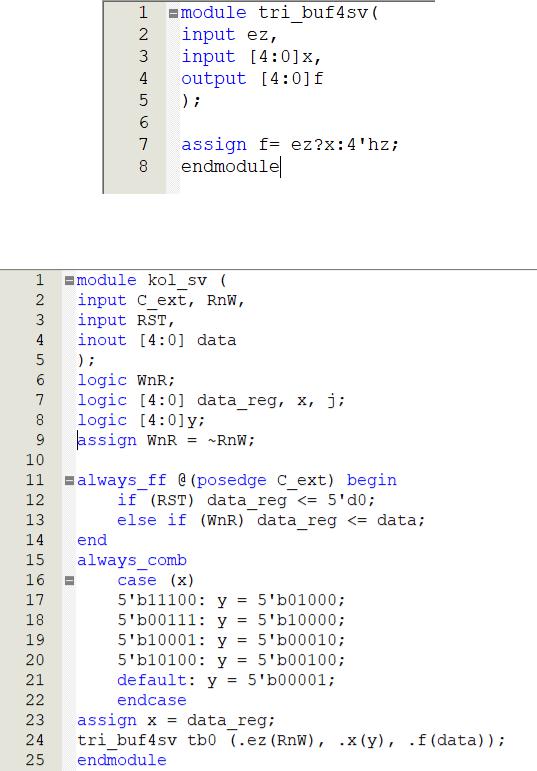

1.4 Описание функциональных схем на HDL

Далее был составлен код описания схемы на HDL согласно варианту №9,

а именно на языке описания аппаратуры System Verilog v2, представленный на рисунках 1.4 – 1.5.

7

Рисунок 1.4 – Описание модуля tri_buf на языке описания аппаратуры System Verilog

Рисунок 1.5 – Код на языке описания аппаратуры SystemVerilog v2

На рисунке 1.5 входы и выходы описаны в строчках 2 – 4. В строчках 5

– 11 объявляются логические сигналы. В строчках 11 – 14 описывается D -

триггер. В строчках 15 – 22 описываются дешифраторы. В строчке 24

8

описывается вывод выходного сигнала с помощью модуля tri_buf.

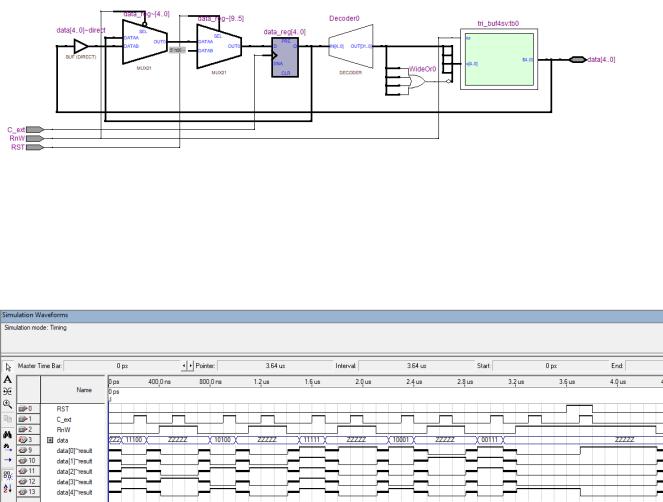

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 1.6.

Рисунок 1.6 – Cформирована схема при помощи RTL Viewer

Также было произведено моделирование устройства, описанного при помощи System Verilog v2 в режиме «Timing», представленное на рисунке 1.7.

Рисунок 1.7 – Моделирование устройства, описанного при помощи System Verilog v2 в режиме «Timing»

Результат совпал с предыдущим моделированием, а также с таблицей истинности.

9

2 РЕАЛИЗАЦИЯ ВЕДУЩЕГО ПОСЛЕДОВАТЕЛЬНОЙ ПЕРЕДАЧИ ДАННЫХ МЛАДШИМИ РАЗЯРДАМИ ВПЕРЕД НА ОСНОВЕ СДВИГАЮЩЕГО РЕГИСТРА С АСИНХРОННЫМ СБРОСОМ

2.1 Таблица истинности для ведущего последовательной передачи данных младшими разрядами вперед на основе сдвигающего регистра с асинхронным сбросом.

Для реализации была взята всё та же таблица истинности задачи согласно варианту, а именно варианту №9. Таблица истинности повторно представлена в таблице 2.1.

Таблица 2.1 – Повторная таблица истинности

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x4 |

x3 |

x2 |

x1 |

x0 |

|

ST2 |

ST1 |

SP2 |

|

SP1 |

FB |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

0 |

|

0 |

1 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

0 |

|

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

0 |

|

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|