Министерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР) Кафедра безопасности информационных систем (БИС)

ПРИМИНЕНИЕ РЕГИСТРОВ И СЧЁТЧИКОВ

Отчет по лабораторной работе №4

по дисциплине «Электроника и схемотехника 2» Вариант №9

Студент гр. 731-2

_____________

28.05.2023

Руководитель Доцент каф. КИБЭВС, к.т.н., доцент

_________ _____________ А.Н. Мальчуков

28.05.2023

Томск 2023

|

Оглавление |

|

Введение................................................................................................................... |

3 |

|

1 ВЫПОЛНЕНИЕ ОПЕРАЦИЙ НАД ПОЛУБАЙТОМ...................................... |

4 |

|

1.1 |

Таблица истинности....................................................................................... |

4 |

1.2 |

Функциональная схема.................................................................................. |

4 |

1.3 |

Моделирование функциональной схемы..................................................... |

6 |

1.4 |

Описание функциональной схемы на HDL................................................. |

7 |

Заключение ............................................................................................................ |

12 |

|

2

Введение

Цель работы: научиться совместно применять регистры и счётчики. Постановка задачи:

1. построить совмещенную таблицу истинности, взяв из таблицы вариантов лабораторной работы №1 4 функции, а именно собственный вариант №9, вариант на единицу больше и еще два варианта на единицу и две

меньше своего варианта. Вариант на единицу больше – F10 = x y ̅̅̅̅̅̅̅̅̅̅

z w,

собственный вариант – F9 = x ̅̅̅̅̅̅̅̅̅ w, вариант на одну единицу меньше

y z

– F8 = x y z w, вариант на две единицы меньше – F7 = ̅̅̅̅̅̅̅ z w.

(x y)

2. для выполнения 4-х параллельных операций над полубайтом организовать приём данных согласно варианту №9, а именно параллельным кодом, с синхронным сбросом и синхронизацией данных по нарастающему фронту. Организовать выдачу данных также согласно варианту №9, а именно последовательным кодом младшими разрядами вперед с синхронизацией по заднему фронту и активным уровнем сигнала «read» в

0.

3. собрать необходимую схему на холсте .bdf, используя встроенные блоки регистров (lpm_dff или lpm_shiftreg) согласно варианту №9, а именно lpm_dff.

4.промоделировать работу схемы в двух режимах. Провести анализ результатов моделирования разных режимов. Сверить результаты моделирования с составленной таблицей истинности.

5.повторить пункты 2-4, только для описания устройств вместо схем используя заданный вариантом язык описания HDL, а именно System Verilog.

6.написать выводы о проделанной работе.

3

|

|

1 ВЫПОЛНЕНИЕ ОПЕРАЦИЙ НАД ПОЛУБАЙТОМ |

|

||||||||

|

|

|

|

|

1.1 Таблица истинности |

|

|

|

|||

|

Таблица истинности для всех четырех функций согласно варианту №9, |

||||||||||

а именно для F10 = x y |

̅̅̅̅̅̅̅̅̅̅ |

̅̅̅̅̅̅̅̅̅ |

|

|

|

||||||

z w, F9 = x y z w, F8 = x y z w |

|||||||||||

|

̅̅̅̅̅̅̅ |

|

|

|

|

|

|

|

|

|

|

и F7 = (x y) z w представлена в таблице 1.1. |

|

|

|

||||||||

Таблица 1.1 – Совмещенная таблица истинности |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

|

Выходы |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

w |

|

x |

|

y |

|

z |

F10 |

|

F9 |

F8 |

F7 |

0 |

|

0 |

|

0 |

|

0 |

1 |

|

0 |

0 |

0 |

0 |

|

0 |

|

0 |

|

1 |

0 |

|

0 |

1 |

1 |

0 |

|

0 |

|

1 |

|

0 |

1 |

|

0 |

0 |

0 |

0 |

|

0 |

|

1 |

|

1 |

0 |

|

0 |

1 |

0 |

0 |

|

1 |

|

0 |

|

0 |

1 |

|

1 |

0 |

0 |

0 |

|

1 |

|

0 |

|

1 |

0 |

|

0 |

1 |

0 |

0 |

|

1 |

|

1 |

|

0 |

0 |

|

0 |

1 |

0 |

0 |

|

1 |

|

1 |

|

1 |

1 |

|

1 |

0 |

1 |

1 |

|

0 |

|

0 |

|

0 |

0 |

|

1 |

1 |

1 |

1 |

|

0 |

|

0 |

|

1 |

1 |

|

1 |

0 |

1 |

1 |

|

0 |

|

1 |

|

0 |

0 |

|

1 |

1 |

1 |

1 |

|

0 |

|

1 |

|

1 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

|

0 |

|

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

|

0 |

|

1 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

|

1 |

|

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

|

1 |

|

1 |

0 |

|

0 |

1 |

1 |

1.2 Функциональная схема

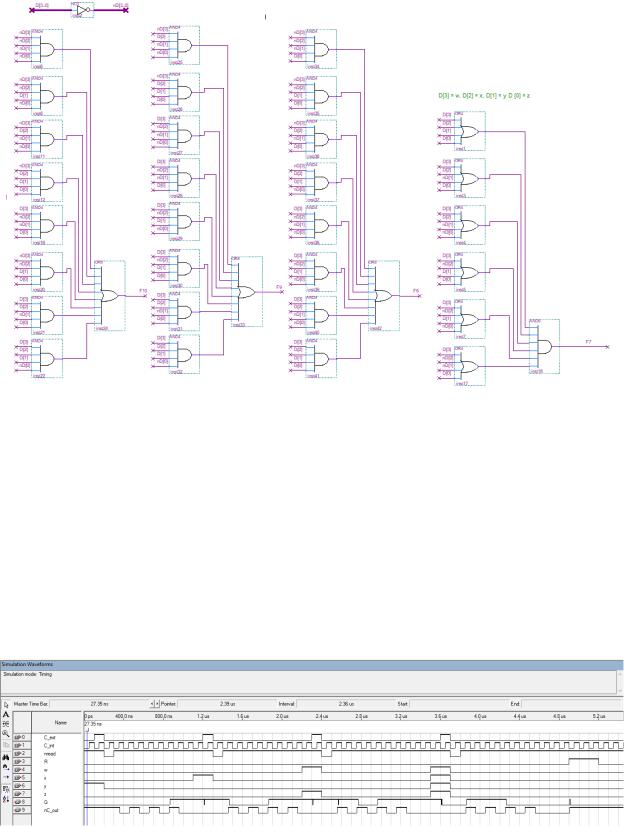

Функциональная схема согласно варианту №9, а именно с приёмом данных параллельным кодом, с синхронным сбросом и синхронизацией данных по нарастающему фронту, а также выдачей данных последовательным кодом младшими разрядами вперед с синхронизацией по заднему фронту и активным уровнем сигнала «read» в 0, представлена на рисунках 1.2 – 1.3.

4

Функции F10, F9, F8 и F7 были построены с помощью формул СДНФ/СКНФ.

Формула СДНФ для выхода F10 имеет вид: (̅ ̅ ̅ ̅) (̅ ̅y̅)

(̅x̅ ̅) (̅x y z) (w̅ ̅z) (w̅y z) (w x̅z) (w x y̅).

Формула СДНФ для выхода F9 имеет вид:

(̅x̅ ̅) (̅x y z) (w̅ ̅ ̅) (w̅ ̅z) (w̅y̅) (w̅y z) (w

x̅z) (w x y̅).

Формула |

СДНФ |

для |

выхода |

F8 |

имеет |

вид: |

(̅ ̅ ̅z) (̅ ̅y z) (̅x̅z) (̅x y̅) (w̅ ̅ ̅) (w̅y̅)

(w x̅ ̅) (w x y z).

Формула СКНФ для выхода F7 имеет вид: (w x y z) (w x̅z) (w x̅ ̅) (w̅y z) (w̅y̅) (w̅ ̅z).

Рисунок 1.2 – Первая часть функциональной схемы

5

Рисунок 1.3 – Вторая часть функциональной схемы

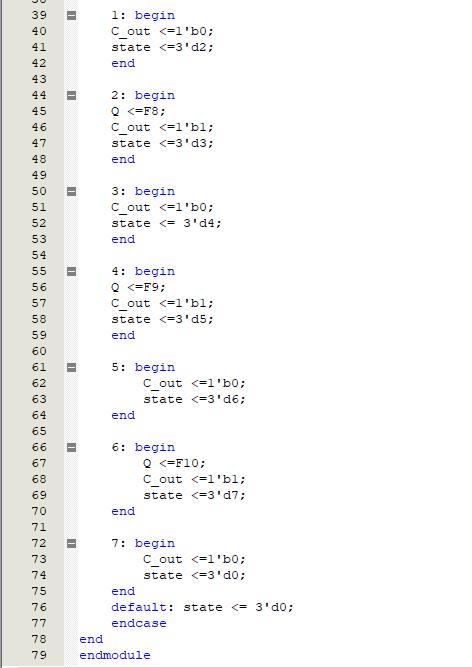

1.3 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional», представленное на рисунках 1.4 – 1.5 соответственно.

Комбинация входных значений w, x, y, z для моделирования были выбраны следующие: (0,0,1,0), (0,1,0,0), (1,0,0,1), (1,1,1,1).

Рисунок 1.4 – Моделирование функциональной схемы в режиме «Timing»

6

Рисунок 1.5 – Моделирование функциональной схемы в режиме «Functional»

Так как моделирование в режиме «Timing» приближено к реальности и отображает задержки переключения, результат немного искажается от идеального в режиме «Functional».

На отрезках моделирования 0 – 200 нс., 1.1 – 1.3 нс., 2.2 – 2.4 нс. и 3.5 –

3.7 нс. происходит чтение входных значений w, x, y, z передним фронтом импульса С_ext. Подача активного сигнала записи выходных значений nread = 0 и выдача значений F10, F9, F8, F7 в строчку nC_out происходит младшими разрядами вперед на отрезках 200 – 1.0 нс., 1.3 – 2.2 нс., 2.4 – 3.3 нс. и 3.7 – 4.6

нс. Все операции сопровождаются тактирующим импульсом C_int.

Значения моделирования совпали со значениями из таблицы истинности.

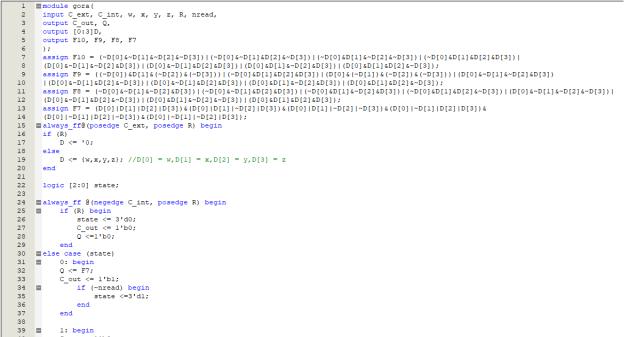

1.4 Описание функциональной схемы на HDL

Далее был составлен код описания схемы на HDL согласно варианту №9,

а именно на языке описания аппаратуры System Verilog, представленный на рисунках 1.6 – 1.7.

7

Рисунок 1.6 – Первая часть описания функциональной схемы на языке описания аппаратуры System Verilog

8

Рисунок 1.7 – Первая часть описания функциональной схемы на языке описания аппаратуры System Verilog

На рисунках 1.6 – 1.7 входы и выходы описаны в строчках 2 – 5. В

строчках 7 – 14 описываются формулы СДНФ/СКНФ для функций F10, F9, F8, F7. В строчках 15 – 20 присваивание значений w, x, y, z для вычислений с помощью формул СДНФ/СКНФ. В строчках 30 – 77 описывается работа конечного автомата.

9

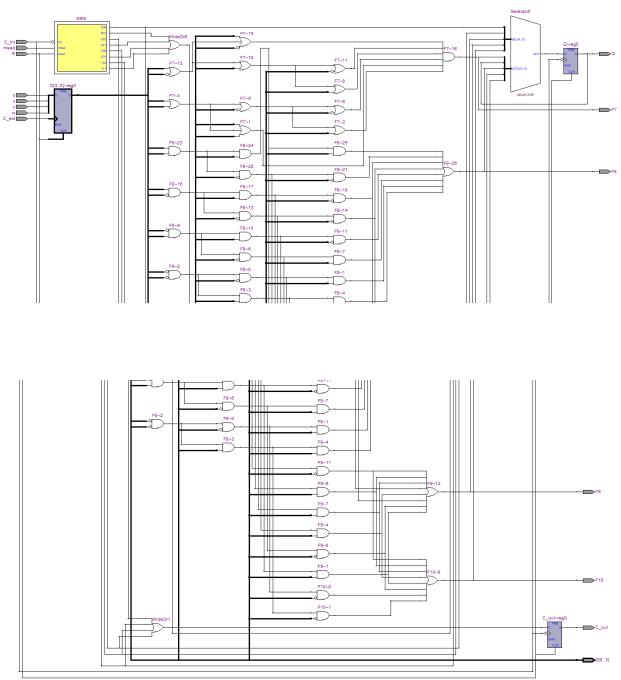

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунках 1.8 – 1.9.

Рисунок 1.8 – Первая часть сформированной схемы при помощи RTL Viewer

Рисунок 1.9 – Вторая часть сформированной схемы при помощи RTL Viewer

Также было произведено моделирование устройства, описанного при помощи System Verilog в режиме «Timing», представленное на рисунке 1.10.

10