4 Семестр / Доп лаба 1 / ЭИС2 доп1лаб вер2

.pdf

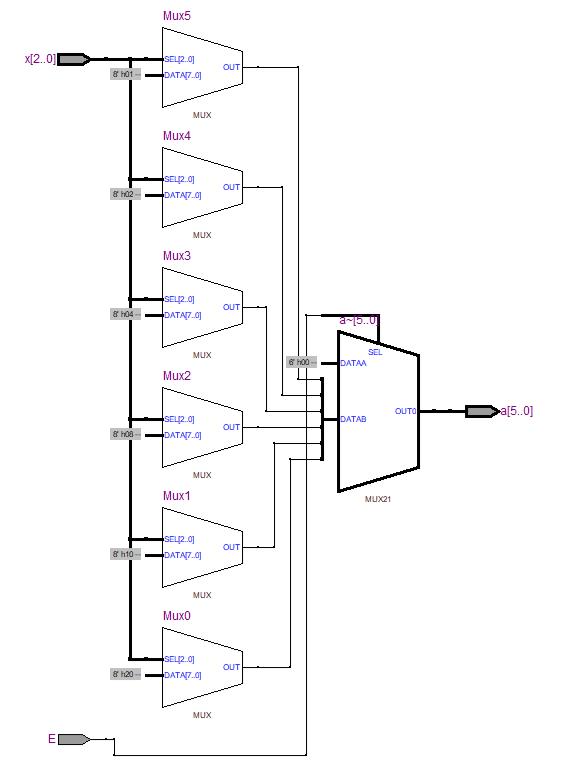

1.7 Моделирование устройства, описанного кодом HDL

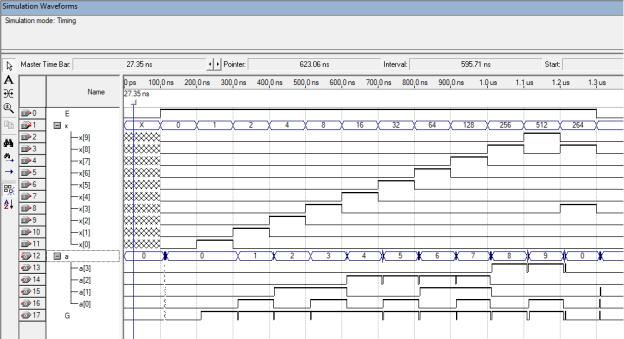

Было произведено моделирование устройства, описанного при помощи

VHDL в режиме «Timing», представленное на рисунке 1.6.

Рисунок 1.6 – Моделирование устройства, описанного при помощи VHDL в

режиме «Timing»

Результат совпал с предыдущим моделированием, а также с таблицей истинности.

11

2 ДЕШИФРАТОР 3-6

2.1 Таблица истинности

Таблица истинности для дешифратора согласно варианту №9, а именно для дешифратора 3-6, представлена в таблице 2.1.

Таблица 2.1 – Таблица истинности для дешифратора

|

|

Входы |

|

|

|

Выходы |

|

|

|||

E |

|

|

x |

|

|

|

|

a |

|

|

|

|

2 |

|

1 |

0 |

5 |

4 |

3 |

|

2 |

1 |

0 |

0 |

x |

|

x |

x |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

0 |

|

0 |

0 |

0 |

2.2 Формулы

Далее были составлены формулы СКНФ/СДНФ для выходов. На базисе И-НЕ были составлены следующие формулы для выходов:

a0 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅ ,

(E x2 x1 x0)

a1 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ,

(E x2 x1 x0)

a2 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ,

(E x2 x1 x0)

a3 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅,

(E x2 x1 x0)

a4 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅ ,

(E x2 x1 x0)

a5 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

(E x2 x1 x0).

12

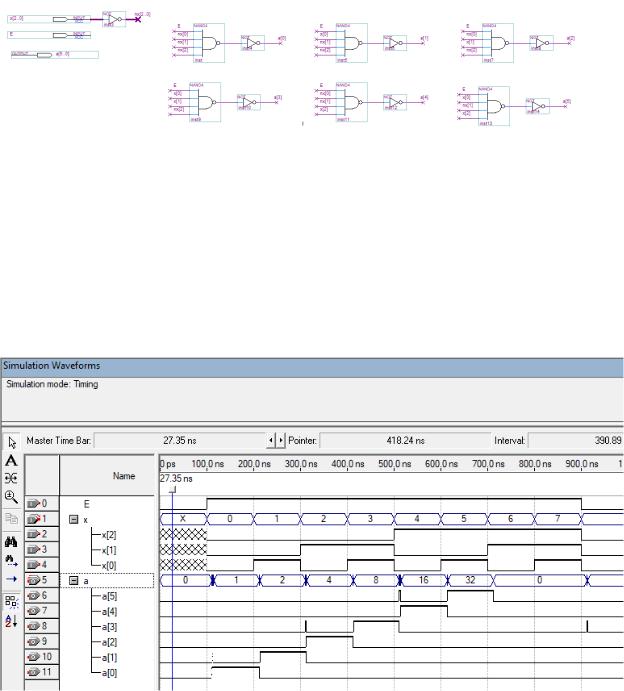

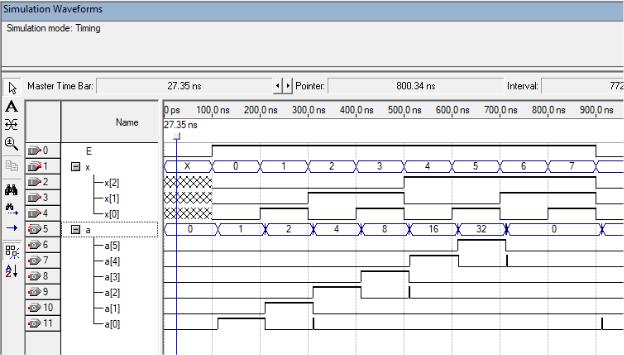

2.3 Функциональная схема

Фунциональная схема для дешифратора 3-6 на базисе И-НЕ,

представлена на рисунке 2.1

Рисунок 2.1 – Функциональная схема дешифратора 3-6

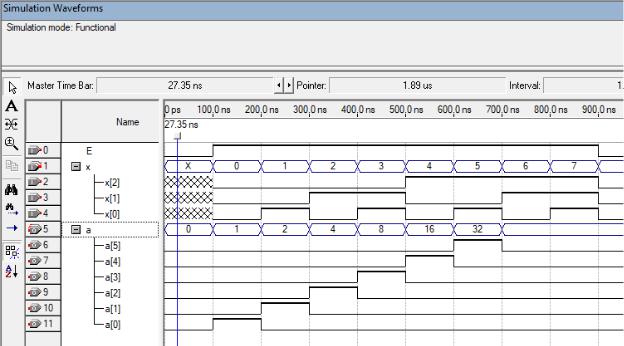

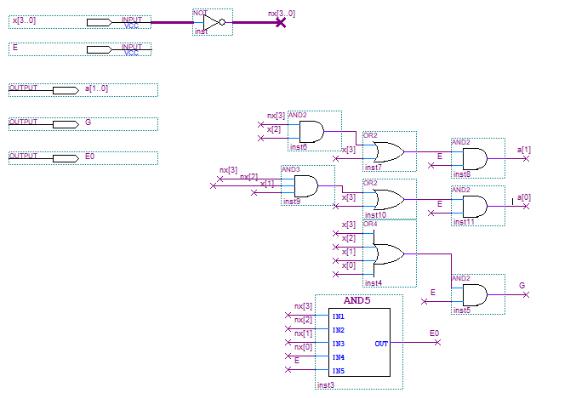

2.4 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional», представленное на рисунках 2.2 – 2.3 соответственно.

Рисунок 2.2 – Моделирование функциональной схемы в режиме «Timing»

13

Рисунок 2.3 – Моделирование функциональной схемы в режиме «Functional»

Так как моделирование в режиме «Timing» приближено к реальности и отображает задержки переключения, результат немного искажается от идеального в режиме «Functional».

Значения моделирования совпали со значениями из таблицы истинности.

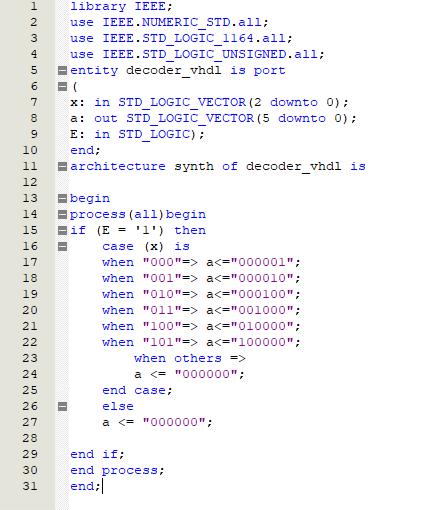

2.5 Описание функциональной схемы на HDL

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры VHDL, представленный на рисунке

2.4.

14

Рисунок 2.4 – Описание функциональной схемы на языке описания аппаратуры VHDL

Входы и выходы описаны в строчках 6 – 9. В строчках 13 – 30

описывается дешифратор 6-3, путем проверки входных значений и при конкретных значениях на входе происходит выдача определенных значений на выход.

2.6 Схема из RTL Viewer для кода HDL

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 2.5.

15

Рисунок 2.5 – Сформированная схема при помощи RTL Viewer

2.7 Моделирование устройства, описанного кодом HDL

Было произведено моделирование устройства, описанного при помощи

16

VHDL в режиме «Timing», представленное на рисунке 2.6.

Рисунок 2.6 – Моделирование устройства, описанного при помощи VHDL в

режиме «Timing»

Результат совпал с предыдущим моделированием, а также с таблицей истинности.

17

3 ПРИОРИТЕТНЫЙ ШИФРАТОР 4-2

3.1 Таблица истинности

Таблица истинности для приоритетного шифратора согласно варианту №9, а именно для приоритетного шифратора 4-2, представлена в таблице 3.1. Таблица 3.1 – Таблица истинности для дешифратора

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

E |

|

|

x |

|

|

a |

G |

E0 |

||

|

3 |

2 |

|

1 |

0 |

1 |

|

0 |

|

|

0 |

x |

x |

|

x |

x |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

1 |

x |

0 |

|

1 |

1 |

0 |

1 |

0 |

1 |

|

x |

x |

1 |

|

0 |

1 |

0 |

1 |

1 |

x |

|

x |

x |

1 |

|

1 |

1 |

0 |

3.2 Формулы

Далее были составлены формулы для выходов. На базисе И, ИЛИ, НЕ были составлены следующие формулы для выходов:

a1 = (x3 |

̅̅̅ |

x2) E, |

|

x3 |

|||

a0 = (x3 |

̅̅̅ |

̅̅̅ |

x1) E, |

x3 |

x2 |

||

G = (x3 x2 x1 x0) E,

̅̅̅ |

̅̅̅ |

̅̅̅ |

̅̅̅ |

E0 = E x3 |

x2 |

x1 |

x0. |

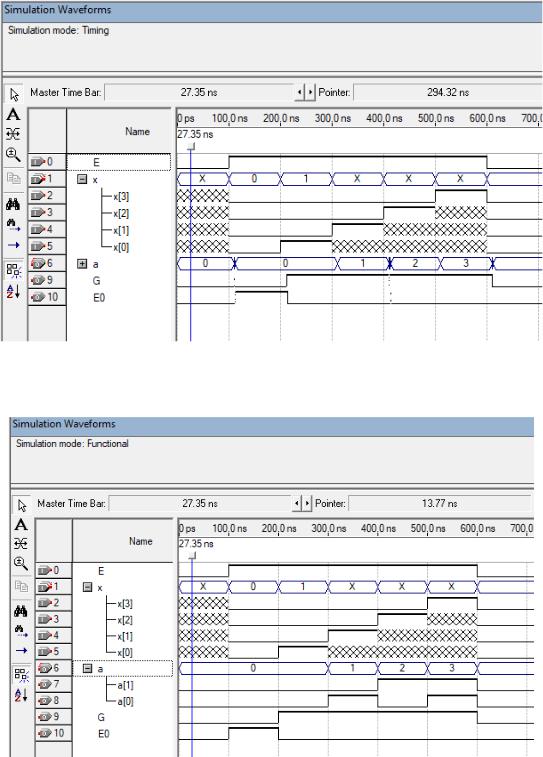

3.3 Функциональная схема

Фунциональная схема для приоритетного шифратора 4-2 на базисе И, ИЛИ, НЕ, представлена на рисунке 3.1

18

Рисунок 3.1 – Функциональная схема приоритетного шифратора 4-2

3.4 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional», представленное на рисунках 3.2 – 3.3 соответственно.

19

Рисунок 3.2 – Моделирование функциональной схемы в режиме «Timing»

Рисунок 3.3 – Моделирование функциональной схемы в режиме «Functional»

Так как моделирование в режиме «Timing» приближено к реальности и отображает задержки переключения, результат немного искажается от идеального в режиме «Functional».

20