4 Семестр / Доп лаба 1 / ЭИС2 доп1лаб вер2

.pdf

Значения моделирования совпали со значениями из таблицы истинности.

3.5 Описание функциональной схемы на HDL

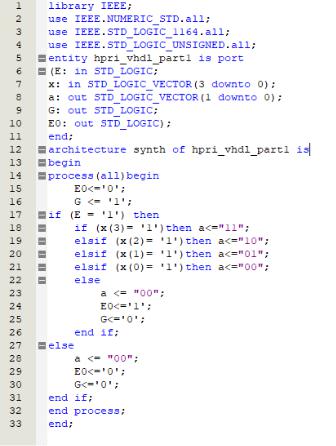

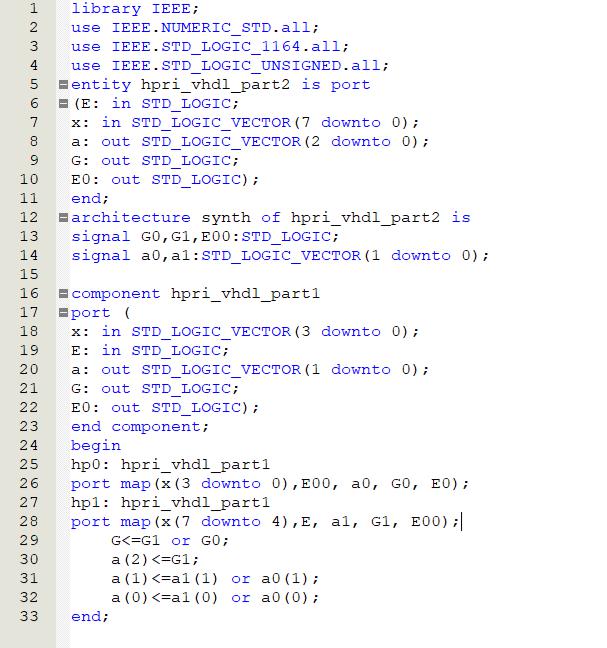

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры VHDL, представленный на рисунке

3.4.

Рисунок 3.4 – Описание функциональной схемы на языке описания аппаратуры VHDL

Входы и выходы описаны в строчках 6 – 10. В строчках 14 – 32

описывается приоритетный шифратор 4-2, реализованный путем проверки каждого из входов на старшую единицу и последующей выдачей номера этого входа в виде двоичного кода.

21

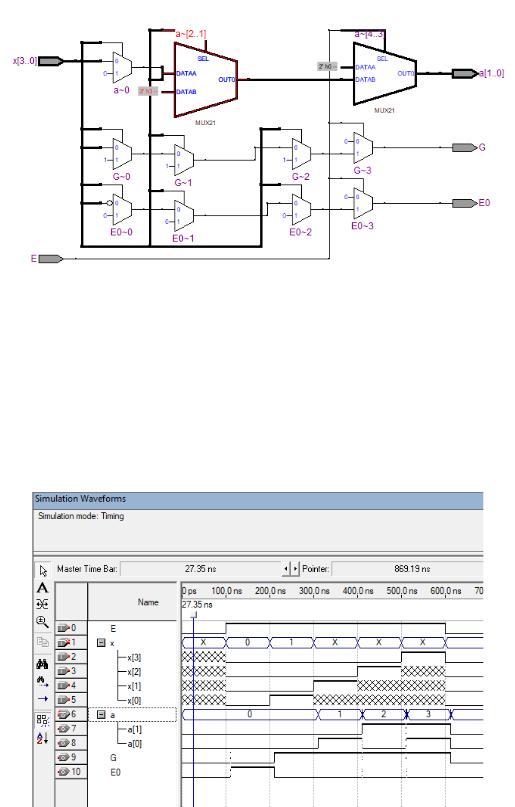

3.6 Схема из RTL Viewer для кода HDL

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 3.5.

Рисунок 3.5 – Сформированная схема при помощи RTL Viewer

3.7 Моделирование устройства, описанного кодом HDL

Было произведено моделирование устройства, описанного при помощи

VHDL в режиме «Timing», представленное на рисунке 3.6.

22

Рисунок 3.6 – Моделирование устройства, описанного при помощи VHDL в

режиме «Timing»

Результат совпал с предыдущим моделированием, а также с таблицей истинности.

3.8 Таблица истинности масштабируемого устройства

Таблица истинности для масштабируемого приоритетного шифратора согласно варианту №9, а именно для масштабируемого приоритетного шифратора 8-3, представлена в таблице 3.2.

Таблица 3.2 – Таблица истинности для масштабируемого приоритетного шифратора

|

|

|

|

Входы |

|

|

|

|

|

|

Выходы |

|

|

||||

E |

|

|

|

|

x |

|

|

|

|

|

a |

|

|

|

G |

E0 |

|

|

7 |

6 |

5 |

|

4 |

|

3 |

2 |

1 |

0 |

2 |

1 |

|

0 |

|

|

|

0 |

x |

x |

x |

|

x |

|

x |

x |

x |

x |

0 |

0 |

|

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

1 |

x |

0 |

0 |

|

1 |

|

1 |

0 |

1 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

x |

x |

0 |

1 |

|

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

|

0 |

|

1 |

x |

x |

x |

0 |

1 |

|

1 |

|

1 |

0 |

1 |

0 |

0 |

0 |

|

1 |

|

x |

x |

x |

x |

1 |

0 |

|

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

|

x |

|

x |

x |

x |

x |

1 |

0 |

|

1 |

|

1 |

0 |

1 |

0 |

1 |

x |

|

x |

|

x |

x |

x |

x |

1 |

1 |

|

0 |

|

1 |

0 |

1 |

x |

x |

x |

|

x |

|

x |

x |

x |

x |

1 |

1 |

|

1 |

|

1 |

0 |

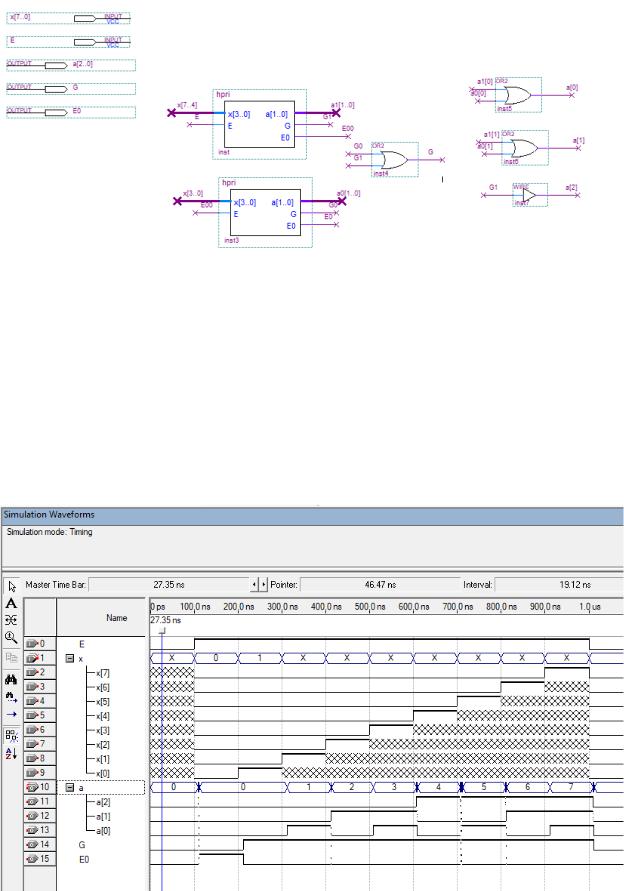

3.9 Функциональная схема масштабируемого устройства

Фунциональная схема для масштабируемого приоритетного шифратора

8-3, представлена на рисунке 3.7.

23

Рисунок 3.7 – Функциональная схема приоритетного шифратора 4-2

3.10 Моделирование масштабируемого устройства

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional», представленное на рисунках 3.8 – 3.9 соответственно.

Рисунок 3.8 – Моделирование функциональной схемы в режиме «Timing» 24

Рисунок 3.9 – Моделирование функциональной схемы в режиме «Functional»

Так как моделирование в режиме «Timing» приближено к реальности и отображает задержки переключения, результат немного искажается от идеального в режиме «Functional».

Значения моделирования совпали со значениями из таблицы истинности.

3.11 Описание функциональной схемы на HDL масштабируемого

устройства

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры VHDL, представленный на рисунке

3.10.

25

Рисунок 3.10 – Описание масштабируемого устройства на языке описания аппаратуры VHDL

Входы и выходы описаны в строчках 6 – 10. В строчках 13 - 14

описываются использующиеся сигналы. В строчках 16 – 23 объявляется ранее составленный приоритетный шифратор 4-2. В строчках 25-28 происходит работа масштабируемого приоритетного шифратора 8-3 благодаря двойному использованию приоритетного шифратора 4-2 с разным набором входных значений. В строчках 29 – 32 происходит объединение выходных значений с

двух приоритетных шифраторов 4-2.

26

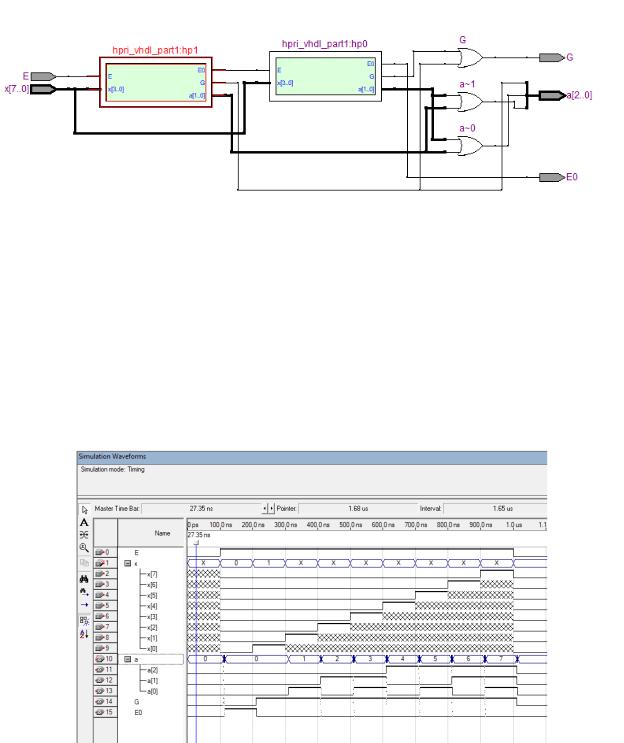

3.12 Схема из RTL Viewer для кода HDL масштабируемого устройства

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 3.11.

Рисунок 3.11 – Сформированная схема при помощи RTL Viewer

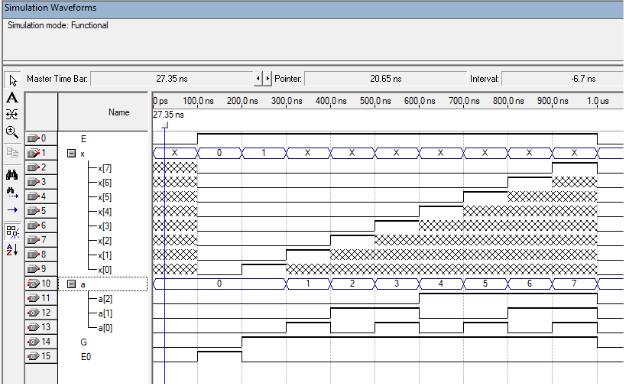

3.13 Моделирование масштабируемого устройства, описанного кодом

HDL

Было произведено моделирование устройства, описанного при помощи

VHDL в режиме «Timing», представленное на рисунке 3.12.

Рисунок 3.12 – Моделирование устройства, описанного при помощи VHDL в

режиме «Timing» 27

Результат совпал с предыдущим моделированием, а также с таблицей

истинности.

28

Заключение

В результате лабораторной работы были изучены двоичные счётчики, их принципы построения и работы.

Все задания выполнялись согласно варианту №9.

Были составлены таблицы истинности для схем согласно варианту №9, а именно для шифратора с количеством входов = 10, для дешифратора с количеством выходов = 6, для приоритетного шифратора с количеством входов = 4. Были составлены формулы СКНФ/СДНФ для всех выходов используя заданный вариантом базис, а именно для шифратора базис ИЛИ-

НЕ, для дешифратора базис И-НЕ, для приоритетного шифратора базис И,ИЛИ,НЕ.

Были собраны необходимые схемы на холстах .bdf для составленных формул для шифратора, дешифратора и приоритетного шифратора согласно варианту №9. Произведено наращивание приоритетного шифратора до 8-3 с использованием символа приоритетного шифратора 4-2.

Далее была промоделирована работа схем в двух режимах, а также был проведен анализ и описаны результаты моделирования. Результаты моделирований совпали с таблицами истинности.

Далее были описаны функциональные схемы, используя заданный вариантом №9 HDL, а именно VHDL. Для написанных кодов были составлены схемы при помощи RTL Viewer. Также была промоделирована работа кодов. Результат моделирований совпал с таблицами истинности.

29