4 Семестр / Доп лаба 2 / ЭИС2 доп2лаб

.pdf

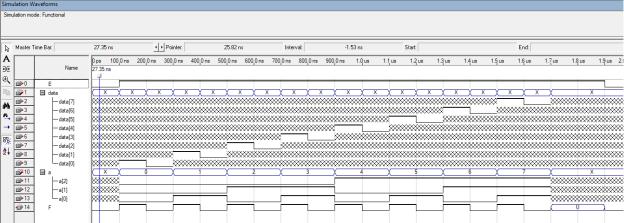

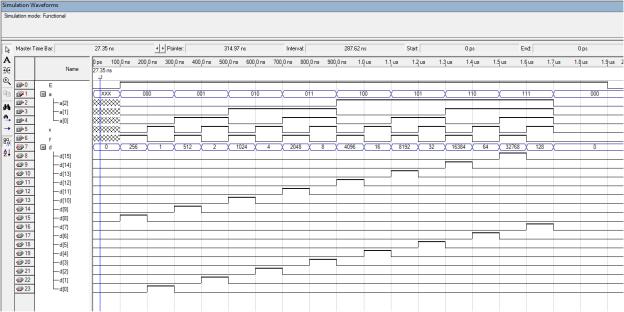

Рисунок 1.9 – Моделирование функциональной схемы в режиме «Functional»

Так как моделирование в режиме «Timing» приближено к реальности и отображает задержки переключения, результат немного искажается от идеального в режиме «Functional».

Значения моделирования совпали со значениями из таблицы истинности.

1.11 Описание функциональной схемы на HDL масштабируемого

устройства

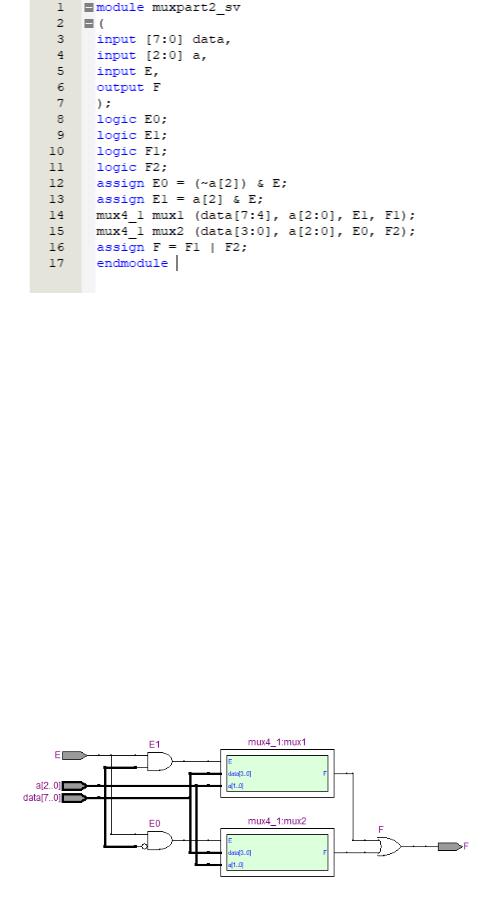

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры System Verilog, представленный на рисунке 1.10.

11

Рисунок 1.10 – Описание масштабируемого устройства на языке описания аппаратуры System Verilog

Входы и выходы описаны в строчках 3 – 6. В строчках 8 - 11

описываются использующиеся сигналы. В строчках 12 – 13 вычисляются сигналы для дальнейшего использования. В строчках 14-15 объявляются и используются ранее составленные мультиплексоры 8-1. В строчке 16

происходит объединение выходных значений с двух мультиплексоров 8-1.

1.12 Схема из RTL Viewer для кода HDL масштабируемого устройства

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 1.11.

Рисунок 1.11 – Сформированная схема при помощи RTL Viewer 12

1.13 Моделирование масштабируемого устройства, описанного кодом

HDL

Было произведено моделирование устройства, описанного при помощи

System Verilog в режиме «Timing», представленное на рисунке 1.12.

Рисунок 1.12 – Моделирование устройства, описанного при помощи System Verilog в режиме «Timing»

Результат совпал с предыдущим моделированием, а также с таблицей истинности.

13

2 ДЕМУЛЬТИПЛЕКСОР 1-8

2.1 Таблица истинности

Таблица истинности для демультиплексора согласно варианту №9, а именно для демультиплексора 1-8 представлена в таблице 2.1.

Таблица 2.1 –Таблица истинности демультиплексора 1-8

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

|

||

E |

a2 |

a1 |

|

a0 |

x |

d7 |

d6 |

d5 |

d4 |

d3 |

d2 |

d1 |

d0 |

0 |

x |

x |

|

x |

x |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

b0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b0 |

1 |

0 |

0 |

|

1 |

b1 |

0 |

0 |

0 |

0 |

0 |

0 |

b1 |

0 |

1 |

0 |

1 |

|

0 |

b2 |

0 |

0 |

0 |

0 |

0 |

b2 |

0 |

0 |

1 |

0 |

1 |

|

1 |

b3 |

0 |

0 |

0 |

0 |

b3 |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

b4 |

0 |

0 |

0 |

b4 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

1 |

b5 |

0 |

0 |

b5 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

0 |

b6 |

0 |

b6 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

b7 |

b7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

2.2 Формулы

Далее с помощью таблицы истинности была составлены формулы для выходов d0-d7 в базисе И-НЕ:

d0= ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅,

(E x 2 1 0)

d1= ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅ ̅̅̅̅̅̅̅̅̅̅,

(E x 2 1 a0)

d2= ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅ ̅̅,

(E x 2 a1 0)

d3= ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ,

(E x 2 a1 a0)

d4= ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅ ̅̅,

(E x a2 1 0)

d5= ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅,

(E x a2 1 a0)

d6= ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅,

(E x a2 a1 0)

d7= ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅.

(E x a2 a1 a0)

14

2.3 Функциональная схема

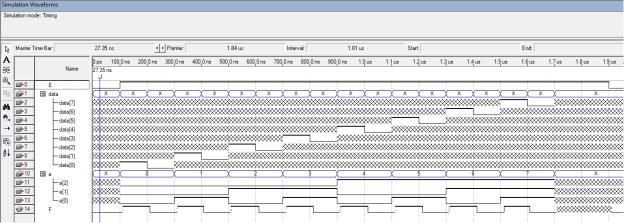

Функциональная схема для демультиплексора 1-8 представлена на рисунке 2.1.

Рисунок 2.1 – Функциональная схема

2.4 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional», представленное на рисунках 2.2 – 2.3 соответственно.

Рисунок 2.2 – Моделирование функциональной схемы в режиме «Timing»

15

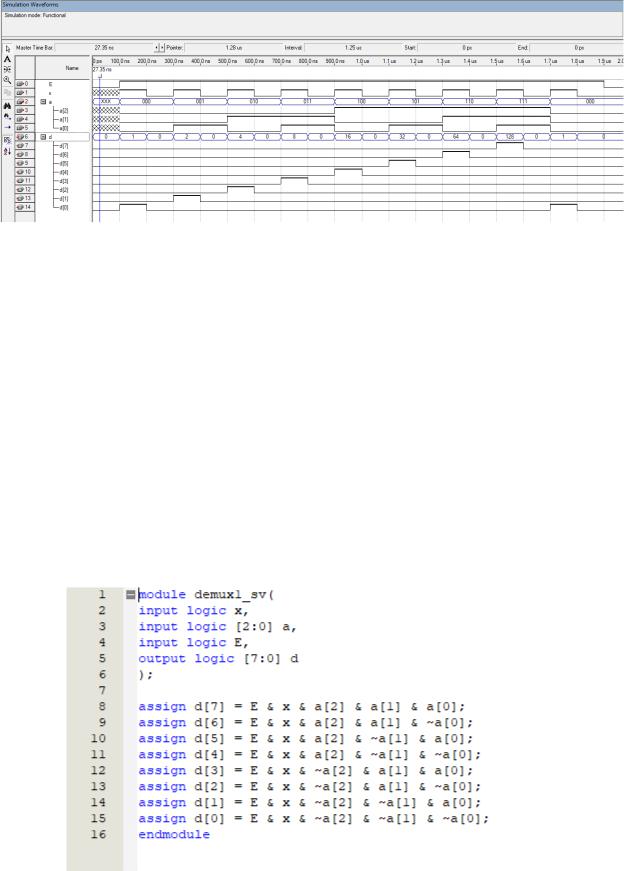

Рисунок 2.3 – Моделирование функциональной схемы в режиме «Functional»

Из-за того, что в режиме работе «Timing» учитывается задержка на элементах, происходят выходы за границы интервала. Результат моделирования совпал с таблицей истинности.

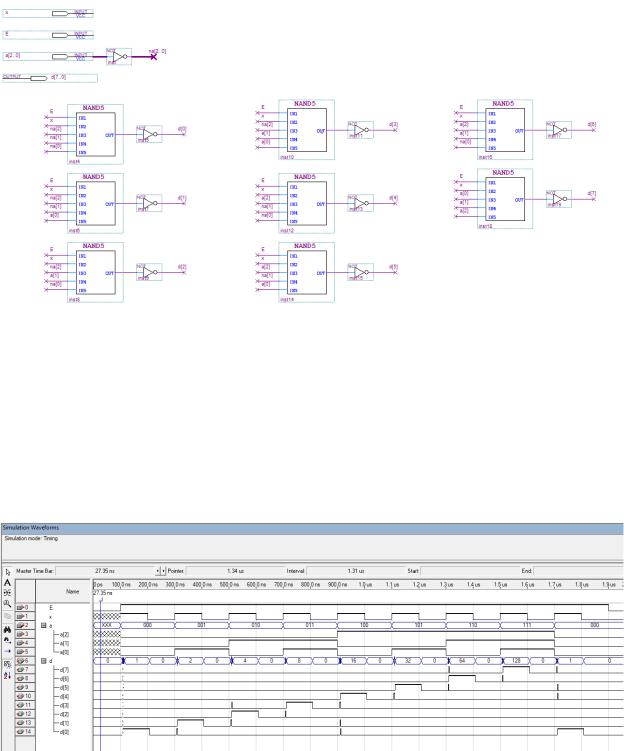

2.5 Описание функциональных схем на HDL

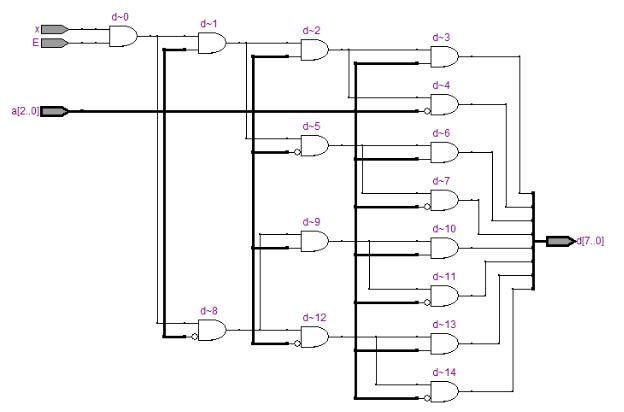

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры System Verilog, представленный на рисунке 2.4.

Рисунок 2.4 – Код на языке описания аппаратуры SystemVerilog

16

Входы и выходы описаны в строчках 2 – 5. В строчках 8-15 описывается демультиплексор с помощью составленных формул в базисе И-НЕ.

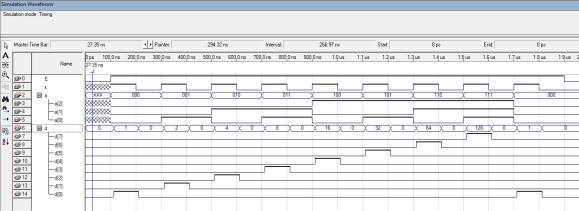

2.6 Схема из RTL Viewer для кода HDL

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 2.5.

Рисунок 2.5 – Сформированная схема при помощи RTL Viewer

2.7 Моделирование устройства, описанного кодом HDL

Было произведено моделирование устройства, описанного при помощи

System Verilog в режиме «Timing», представленное на рисунке 2.6.

17

Рисунок 2.6 – Моделирование устройства, описанного при помощи System Verilog в режиме «Timing»

Результат совпал с предыдущим моделированием, а также с таблицей истинности.

2.8 Таблица истинности масштабируемого устройства

Таблица истинности для масштабируемого демультиплексора согласно варианту №9, а именно для масштабируемого демультиплексора 2-16,

представлена в таблице 2.2.

Таблица 2.2 – Таблица истинности для масштабируемого мультиплексора

|

|

Входы |

|

|

|

|

|

|

|

|

|

Выходы |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

a2 |

a1 |

a0 |

y |

x |

d15 |

d14 |

d13 |

d12 |

d11 |

d10 |

d9 |

|

d8 |

d7 |

d6 |

d5 |

d4 |

d3 |

d2 |

d1 |

d0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

x |

x |

x |

x |

x |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

c0 |

b0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

c0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

c1 |

b1 |

0 |

0 |

0 |

0 |

0 |

0 |

c1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

c2 |

b2 |

0 |

0 |

0 |

0 |

0 |

c2 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

b2 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

c3 |

b3 |

0 |

0 |

0 |

0 |

c3 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

b3 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

c4 |

b4 |

0 |

0 |

0 |

c4 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

b4 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

c5 |

b5 |

0 |

0 |

c5 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

b5 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

c6 |

b6 |

0 |

c6 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

b6 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

c7 |

b7 |

c7 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

b7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

18

2.9 Функциональная схема масштабируемого устройства

Фунциональная схема для масштабируемого демультиплексора 2-16,

представлена на рисунке 2.7.

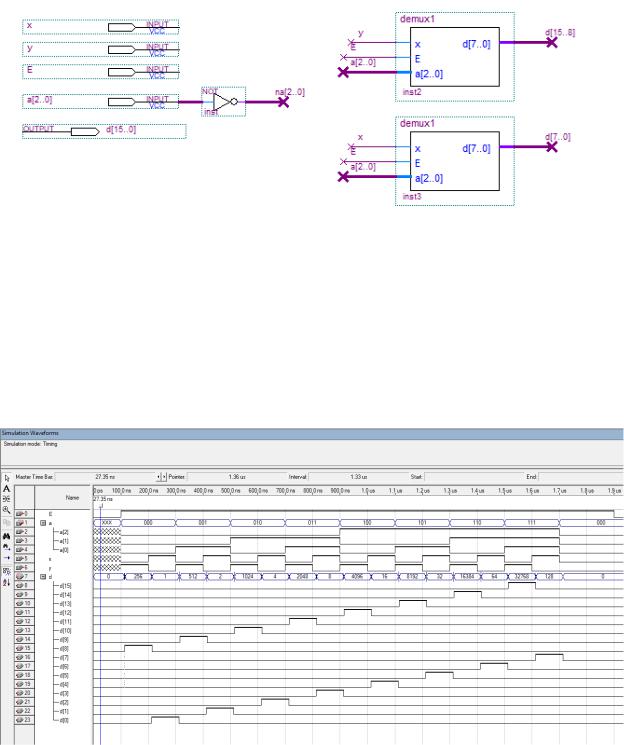

Рисунок 2.7 – Функциональная схема демультиплексора 2-16

2.10 Моделирование масштабируемого устройства

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional», представленное на рисунках 2.8 – 2.9 соответственно.

Рисунок 2.8 – Моделирование функциональной схемы в режиме «Timing»

19

Рисунок 2.9 – Моделирование функциональной схемы в режиме «Functional»

Так как моделирование в режиме «Timing» приближено к реальности и отображает задержки переключения, результат немного искажается от идеального в режиме «Functional».

Значения моделирования совпали со значениями из таблицы истинности.

2.11 Описание функциональной схемы на HDL масштабируемого

устройства

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры System Verilog, представленный на рисунке 2.10.

20