4 Семестр / Доп лаба 2 / ЭИС2 доп2лаб

.pdf

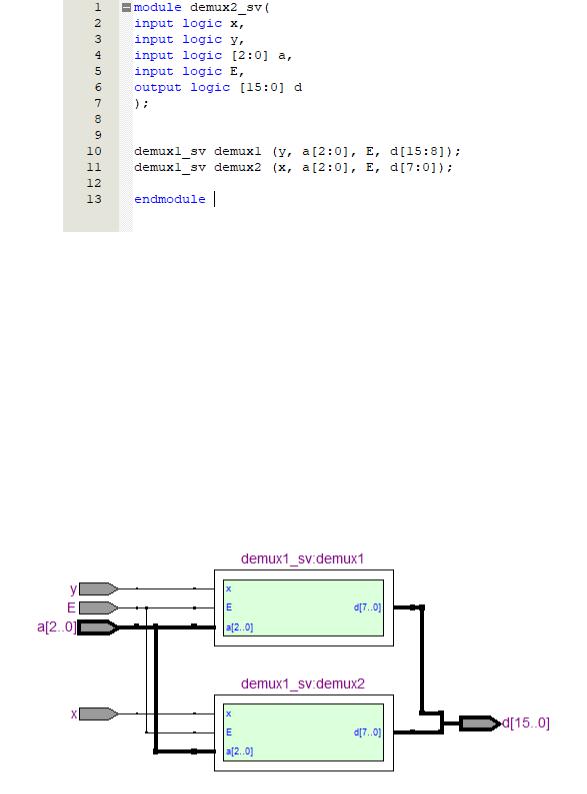

Рисунок 2.10 – Описание масштабируемого устройства на языке описания аппаратуры System Verilog

Входы и выходы описаны в строчках 2 – 6. В строчках 10-11

объявляются и используются ранее составленные демультиплексоры 1-8.

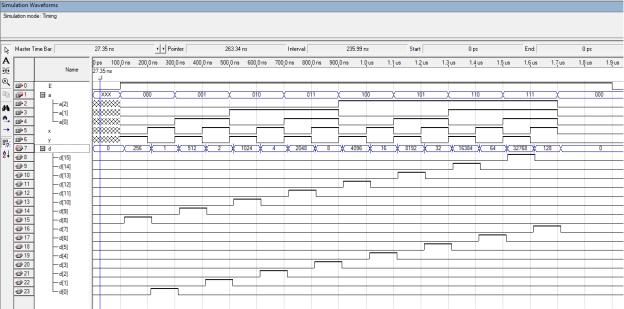

2.12 Схема из RTL Viewer для кода HDL масштабируемого устройства

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 2.11.

Рисунок 2.11 – Сформированная схема при помощи RTL Viewer

21

2.13 Моделирование масштабируемого устройства, описанного кодом

HDL

Было произведено моделирование устройства, описанного при помощи

System Verilog в режиме «Timing», представленное на рисунке 2.12.

Рисунок 2.12 – Моделирование устройства, описанного при помощи System Verilog в режиме «Timing»

Результат совпал с предыдущим моделированием, а также с таблицей истинности.

22

3 РЕАЛИЗАЦИЯ ФУНКЦИИ НА ОСНОВЕ МУЛЬТИПЛЕКСОРА

3.1 Таблица истинности

Далее была реализована функция согласно варианту №9 из первой

|

|

|

̅̅̅̅̅̅̅̅̅ |

|

|

лабораторной работы, а именно F9 = x y z w. Таблица истинности для |

|||||

функции F9 представлена в таблице 3.1. |

|

|

|||

Таблица 3.1 – Таблица истинности функции |

|

|

|||

|

|

|

|

|

|

|

|

Входы |

|

Выход |

|

w |

x |

|

y |

z |

F9 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

1 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

1 |

1 |

3.2 Функциональная схема

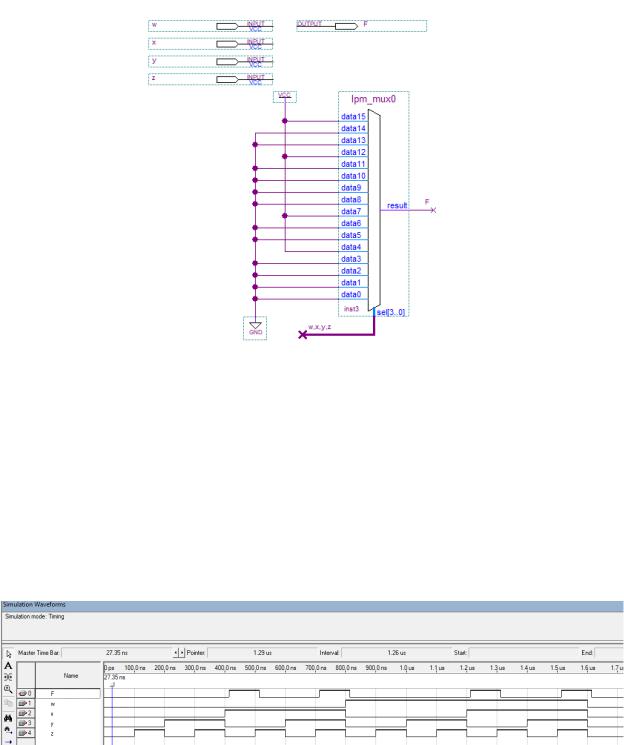

Далее была собрана функциональная схема на основе мультиплексора,

представленная на рисунке 3.1.

23

Рисунок 3.1 – Функциональная схема реализации функции на основе мультиплексора

3.3 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional», представленное на рисунках 3.2 – 3.3 соответственно.

Рисунок 3.2 – Моделирование функциональной схемы реализации формулы при помощи мультиплексора в режиме «Timing»

24

Рисунок 3.3 – Моделирование функциональной схемы реализации формулы при помощи мультиплексора в режиме «Functional»

25

4 РЕАЛИЗАЦИЯ ФУНКЦИИ НА ОСНОВЕ ДЕМУЛЬТИПЛЕКСОРА

4.1 Таблица истинности

Также была реализована функция согласно варианту №9 из первой

лабораторной работы, а именно F9 = x |

|

̅̅̅̅̅̅̅̅̅ |

w на основе |

||||

y z |

|||||||

демультиплексора. Таблица истинности для функции F9 повторно |

|||||||

представлена в таблице 4.1. |

|

|

|

|

|

|

|

Таблица 4.1 – Таблица истинности функции |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

Выход |

|

w |

x |

|

y |

|

z |

|

F9 |

0 |

0 |

|

0 |

|

0 |

|

0 |

0 |

0 |

|

0 |

|

1 |

|

0 |

0 |

0 |

|

1 |

|

0 |

|

0 |

0 |

0 |

|

1 |

|

1 |

|

0 |

0 |

1 |

|

0 |

|

0 |

|

1 |

0 |

1 |

|

0 |

|

1 |

|

0 |

0 |

1 |

|

1 |

|

0 |

|

0 |

0 |

1 |

|

1 |

|

1 |

|

1 |

1 |

0 |

|

0 |

|

0 |

|

0 |

1 |

0 |

|

0 |

|

1 |

|

0 |

1 |

0 |

|

1 |

|

0 |

|

0 |

1 |

0 |

|

1 |

|

1 |

|

0 |

1 |

1 |

|

0 |

|

0 |

|

1 |

1 |

1 |

|

0 |

|

1 |

|

0 |

1 |

1 |

|

1 |

|

0 |

|

0 |

1 |

1 |

|

1 |

|

1 |

|

1 |

4.2 Функциональная схема

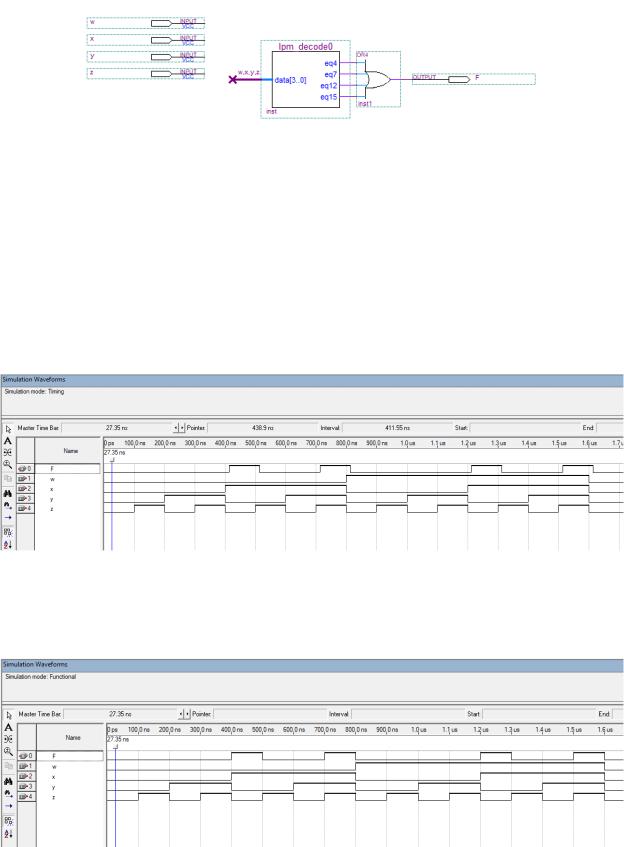

Далее была собрана функциональная схема на основе демультиплексора, представленная на рисунке 4.1.

26

Рисунок 4.1 – Функциональная схема реализации функции на основе демультиплексора

4.3 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional», представленное на рисунках 4.2 – 4.3 соответственно.

Рисунок 4.2 – Моделирование функциональной схемы реализации формулы при помощи демультиплексора в режиме «Timing»

Рисунок 4.2 – Моделирование функциональной схемы реализации формулы при помощи демультиплексора в режиме «Functional»

27

Заключение

В результате лабораторной работы были приобретены навыки создавать мультиплексоры и мультиплексоры на разных базисах, а также реализовывать функцию на мультиплексоре и дешифраторе.

Все задания выполнялись согласно варианту №9.

Были составлены таблицы истинности для схем согласно варианту №9, а именно для мультиплексора 4-1 и наращенной его версии до 8-1, а также для демультиплексора 1-8 и его наращенной версии до 2-16. Были написаны формулы для всех выходов в виде СКНФ или СДНФ. Были приведены формулы к базису согласно варианту №9, а именно для мультиплексора в базис ИЛИ-НЕ, для демультиплексора в базис И-НЕ.

Были собраны схемы на холстах .bdf, согласно полученным формулам. Также были собраны схемы для блоков большей размерности используя полученные блоки ранее. Были созданы две схемы, которые реализуют функцию по формуле из варианта №9 лабораторной работы №1, а именно F9

= x ̅̅̅̅̅̅̅̅̅ w.y z

Была промоделирована работа схем в двух режимах. Проведен анализ результатов моделирования, а также сравнены результаты моделирования с составленными таблицами истинности. Результаты совпали

Также были описаны схемы на языке HDL, а именно на SystemVerilog.

Также были смоделированы работы данных описаний. Результаты совпали с предыдущими моделированиями, а также с таблицей истинности.

При моделировании работы схем если запускать моделирование в режиме «Timing», то некоторые сигналы будут выходить из временного интервала. Из этого был сделан вывод, что в режиме «Timing» учитываются задержки элементов схемы.

28