4 Семестр / Доп лаба 4 / ЭИС2 доп4лаб

.pdfМинистерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР) Кафедра безопасности информационных систем (БИС)

ИЗУЧЕНИЕ РАБОТЫ СЧЕТЧИКОВ

Отчет по дополнительной лабораторной работе №4

по дисциплине «Электроника и схемотехника 2» Вариант №9

Студент гр. 731-2

_____________

09.06.2023

Руководитель Доцент каф. КИБЭВС, к.т.н., доцент

_________ _____________ А.Н. Мальчуков

09.06.2023

Томск 2023

|

Оглавление |

|

Введение................................................................................................................... |

4 |

|

1 АСИНХРОННЫЙ СЧЕТЧИК ............................................................................. |

5 |

|

1.1 |

Таблица истинности....................................................................................... |

5 |

1.2 |

Функциональная схема.................................................................................. |

6 |

1.3 |

Моделирование функциональной схемы..................................................... |

6 |

1.4 |

Описание функциональной схемы на HDL................................................. |

7 |

1.5 |

Схема из RTL Viewer для кода HDL............................................................ |

8 |

1.6 |

Моделирование устройства, описанного кодом HDL................................ |

9 |

2 СИНХРОННЫЙ СЧЕТЧИК .............................................................................. |

10 |

|

2.1 |

Таблица истинности..................................................................................... |

10 |

2.2 |

Функциональная схема................................................................................ |

11 |

2.3 |

Моделирование функциональной схемы................................................... |

11 |

2.4 |

Описание функциональной схемы на HDL............................................... |

12 |

2.5 |

Схема из RTL Viewer для кода HDL.......................................................... |

13 |

2.6 |

Моделирование устройства, описанного кодом HDL.............................. |

14 |

3 ДЕЛИТЕЛЬ ЧАСТОТЫ..................................................................................... |

15 |

|

3.1 |

Расчеты для построения схемы .................................................................. |

15 |

3.2 |

Функциональная схема................................................................................ |

15 |

3.3 |

Моделирование функциональной схемы................................................... |

16 |

3.4 |

Описание функциональной схемы на HDL............................................... |

16 |

3.5 |

Схема из RTL Viewer для кода HDL.......................................................... |

17 |

3.6 |

Моделирование устройства, описанного кодом HDL.............................. |

18 |

4 ФОРМИРОВАНИЕ ЗАДЕРЖКИ...................................................................... |

19 |

|

4.1 |

Расчеты для построения схемы .................................................................. |

19 |

4.2 |

Функциональная схема................................................................................ |

19 |

4.3 |

Моделирование функциональной схемы................................................... |

20 |

4.4 |

Описание функциональной схемы на HDL............................................... |

20 |

4.5 |

Схема из RTL Viewer для кода HDL.......................................................... |

21 |

4.6 |

Моделирование устройства, описанного кодом HDL.............................. |

22 |

|

2 |

|

Заключение ............................................................................................................ |

23 |

3

Введение

Цель работы: изучить двоичные счётчики, их принципы построения и

работы.

Постановка задачи:

1.составить таблицы функционирования для схем согласно варианту №9, а именно для асинхронного вычитающего счетчика с модулем счета 25, построенного на D-триггерах, а также для синхронного суммирующего счетчика с асинхронным сбросом, с модулем счета 31, управляемого передним фронтом. Далее провести расчеты для задачи деления частоты и организации задержки используя данные из варианта №9, а именно для задачи деления частоты выходная частота должна равняться 208333 Гц., в то время как для задачи организации задержки длительность задержки между импульсами должна равняться 0,58 мкс.

2.собрать необходимые схемы на холстах .bdf для заданных счетчиков, делителя частоты и задержки согласно варианту №9.

3.промоделировать работу схем в двух режимах. Провести анализ результатов моделирования разных режимов. Сверить результаты моделирования с составленными таблицами истинности и расчетами.

5.повторить пункты 2-3, только для описания устройств вместо схем на холстах .bdf используя заданный вариантом язык описания HDL, а именно

System Verilog.

6. написать выводы о проделанной работе.

4

1 АСИНХРОННЫЙ СЧЕТЧИК

1.1 Таблица истинности

Таблица истинности для асинхронного счетчика согласно варианту №9, а именно для асинхронного вычитающего счетчика с модулем счета 25, построенного на D-триггерах, представлена в таблице 1.1.

Таблица 1.1 – Таблица истинности для вычитающего счетчика

№ |

|

|

Выходы |

|

|

Число |

|

|

|

|

|

|

|||

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|||

|

|

||||||

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

24 |

|

2 |

1 |

0 |

1 |

1 |

1 |

23 |

|

3 |

1 |

0 |

1 |

1 |

0 |

22 |

|

4 |

1 |

0 |

1 |

0 |

1 |

21 |

|

5 |

1 |

0 |

1 |

0 |

0 |

20 |

|

6 |

1 |

0 |

0 |

1 |

1 |

19 |

|

7 |

1 |

0 |

0 |

1 |

0 |

18 |

|

8 |

1 |

0 |

0 |

0 |

1 |

17 |

|

9 |

1 |

0 |

0 |

0 |

0 |

16 |

|

10 |

0 |

1 |

1 |

1 |

1 |

15 |

|

11 |

0 |

1 |

1 |

1 |

0 |

14 |

|

12 |

0 |

1 |

1 |

0 |

1 |

13 |

|

13 |

0 |

1 |

1 |

0 |

0 |

12 |

|

14 |

0 |

1 |

0 |

1 |

1 |

11 |

|

15 |

0 |

1 |

0 |

1 |

0 |

10 |

|

16 |

0 |

1 |

0 |

0 |

1 |

9 |

|

17 |

0 |

1 |

0 |

0 |

0 |

8 |

|

18 |

0 |

0 |

1 |

1 |

1 |

7 |

|

19 |

0 |

0 |

1 |

1 |

0 |

6 |

|

20 |

0 |

0 |

1 |

0 |

1 |

5 |

|

21 |

0 |

0 |

1 |

0 |

0 |

4 |

|

22 |

0 |

0 |

0 |

1 |

1 |

3 |

|

23 |

0 |

0 |

0 |

1 |

0 |

2 |

|

24 |

0 |

0 |

0 |

0 |

1 |

1 |

|

25 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

5 |

|

|

|

1.2 Функциональная схема

Функциональная схема согласно варианту №9, а именно для асинхронного вычитающего счетчика с модулем счета 25, построенного на D-

триггерах, представлена на рисунке 1.1.

Рисунок 1.1 – Функциональная схема вычитающего счетчика

1.3 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах «Timing» и «Functional», представленное на рисунках 1.2 – 1.3 соответственно.

Рисунок 1.2 – Моделирование функциональной схемы в режиме «Timing»

6

Рисунок 1.3 – Моделирование функциональной схемы в режиме «Functional»

Так как моделирование в режиме «Timing» приближено к реальности и отображает задержки переключения, результат немного искажается от идеального в режиме «Functional».

Значения моделирования совпали со значениями из таблицы истинности.

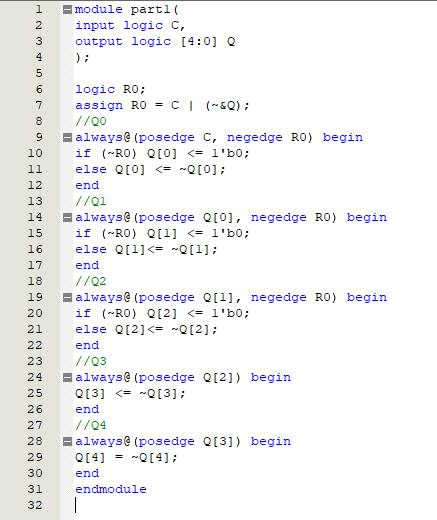

1.4 Описание функциональной схемы на HDL

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры System Verilog, представленный на рисунке 1.4.

7

Рисунок 1.4 – Описание функциональной схемы на языке описания аппаратуры System Verilog

Входы и выходы описаны в строчках 2 – 3. В строчках 6 – 7 описывается формула для организации сброса. В строчках 9 – 30 описываются D - триггеры,

выполняющие функцию вычитающего счетчика с модулем счета 25.

1.5 Схема из RTL Viewer для кода HDL

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 1.5.

8

Рисунок 1.5 – Сформированная схема при помощи RTL Viewer

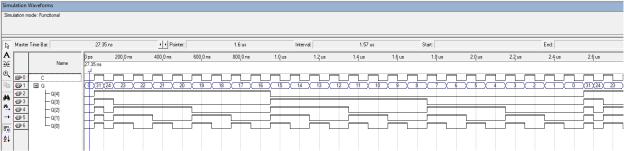

1.6 Моделирование устройства, описанного кодом HDL

Было произведено моделирование устройства, описанного при помощи

System Verilog в режиме «Timing», представленное на рисунке 1.6.

Рисунок 1.6 – Моделирование устройства, описанного при помощи System Verilog в режиме «Timing»

Результат совпал с предыдущим моделированием, а также с таблицей истинности.

9

2 СИНХРОННЫЙ СЧЕТЧИК

2.1 Таблица истинности

Таблица истинности для синхронного счетчика согласно варианту №9, а именно для синхронного суммирующего счетчика с асинхронным сбросом, с модулем счета 31, управляемого передним фронтом, представлена в таблице

2.1.

Таблица 2.1 – Таблица истинности для суммирующего счетчика

|

|

|

Выходы |

|

|

|

||

|

|

|

|

|

|

|

|

|

№ |

R |

Q4 |

Q3 |

|

Q2 |

Q1 |

Q0 |

Число |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

2 |

0 |

0 |

0 |

|

0 |

1 |

0 |

2 |

3 |

0 |

0 |

0 |

|

0 |

1 |

1 |

3 |

4 |

0 |

0 |

0 |

|

1 |

0 |

0 |

4 |

5 |

0 |

0 |

0 |

|

1 |

0 |

1 |

5 |

6 |

0 |

0 |

0 |

|

1 |

1 |

0 |

6 |

7 |

0 |

0 |

0 |

|

1 |

1 |

1 |

7 |

8 |

0 |

0 |

1 |

|

0 |

0 |

0 |

8 |

9 |

0 |

0 |

1 |

|

0 |

0 |

1 |

9 |

10 |

0 |

0 |

1 |

|

0 |

1 |

0 |

10 |

11 |

0 |

0 |

1 |

|

0 |

1 |

1 |

11 |

12 |

0 |

0 |

1 |

|

1 |

0 |

0 |

12 |

13 |

0 |

0 |

1 |

|

1 |

0 |

1 |

13 |

14 |

0 |

0 |

1 |

|

1 |

1 |

0 |

14 |

15 |

0 |

0 |

1 |

|

1 |

1 |

1 |

15 |

16 |

0 |

1 |

0 |

|

0 |

0 |

0 |

16 |

17 |

0 |

1 |

0 |

|

0 |

0 |

1 |

17 |

18 |

0 |

1 |

0 |

|

0 |

1 |

0 |

18 |

19 |

0 |

1 |

0 |

|

0 |

1 |

1 |

19 |

20 |

0 |

1 |

0 |

|

1 |

0 |

0 |

20 |

21 |

0 |

1 |

0 |

|

1 |

0 |

1 |

21 |

22 |

0 |

1 |

0 |

|

1 |

1 |

0 |

22 |

23 |

0 |

1 |

0 |

|

1 |

1 |

1 |

23 |

24 |

0 |

1 |

1 |

|

0 |

0 |

0 |

24 |

25 |

0 |

1 |

1 |

|

0 |

0 |

1 |

25 |

|

|

|

|

10 |

|

|

|

|