Постановка задачи

1.1 Функции программы.

Из анализа технического задания следует, что программа устройства должна обеспечивать:

ввод времени партии у двух игроков осуществляется насчетом (формат времени Ч:ММ:СС:МС);

точность отображения времени 0,1 секунды;

отображать оставшееся время у игроков;

отображать и считать количество ходов игроков;

диапазон количества ходов 0-999;

обеспечивать удобное переключение хода игрока;

автоматическая установка времени по типу партии (пуля, блиц, быстрые, классические)

определить победителя.

1.2 Функциональный смысл входной и выходной информации.

Входная информация:

время игроков на оставшиеся на ходы;

сообщение о готовности к игре;

кнопки переключения хода;

Выходная информация:

индикация окончания времени у одного из игроков;

отображение количества сделанных ходов текущего игрока, т.е. игрока, который ходит в данный момент

1.3 Типы устройств ввода – вывода и формы представления информации

Устройства ввода:

кнопки без фиксации.

Устройства вывода:

Семисегментные индикаторы для отображения: времени обоих игроков, количества ходов текущего игрока.

Двоичные индикаторы для вывода информации о состоянии устройства.

На основании перечисленных требований можно представить разрабатываемое устройство в виде «черного ящика», а также изобразить лицевую панель устройства. Представление устройства в виде «черного ящика» показано на рисунке 1.1. Лицевая панель устройства представлена на рисунке 1.2.

Рисунок 1.1 – Представление разрабатываемого устройства в виде «черного ящика»

Рисунок 1.2 – Лицевая панель разрабатываемого устройства

2 Разработка архитектуры устройства

Разработка архитектуры устройства сводится к разработке архитектуры процессора, архитектуры памяти и архитектуры интерфейса.

2.1 Разработка архитектуры процессора

Разработка архитектуры устройства сводится к разработке архитектуры процессора, архитектуры памяти и архитектуры интерфейса.

Архитектура процессора полностью определяется типом используемого микропроцессора. Поскольку задан тип микропроцессора К1810ВМ88, то архитектура процессора полностью определена. Архитектура процессора изображена на рисунке 2.1.

Рисунок 2.1 – Архитектура процессора

2.2 Разработка архитектуры памяти

В разрабатываемом устройстве необходимо использовать ПЗУ для хранения программы работы процессора и ОЗУ – для хранения работы программы. В связи с простотой устройства и для ОЗУ и для ПЗУ достаточен объем в 2 Кбайта. Распределение адресного пространства между ОЗУ и ПЗУ осуществляется с помощью старшей линии адреса А19. Из архитектуры памяти следует, что ОЗУ выбирается приА19=0, а ПЗУ – приА19=1. На рисунке 2.2 приведена архитектура памяти разрабатываемой МПС.

Рисунок 2.2 – Архитектура памяти

2.3 Разработка архитектуры интерфейса

Архитектура интерфейса разрабатывается на основе схемы представления устройства в виде «черного ящика» (рисунок 1.1). Поскольку эта схема полностью определяет номенклатуру внешних устройств, то остается лишь выбрать соответствующие порты ввода/вывода и методы обмена данными с этими устройствами, определить разрядность внешних устройств и распределить их по разрядам портов ввода/вывода.

Кнопки являются одноразрядными устройствами ввода и должны подключаться к входам порта ввода inport.

Рисунок 2.3 – линейная схема подключения кнопок

Двоичные индикаторы являются одноразрядными устройствами вывода и должны подключаться к выходам порта вывода outflag.

Рисунок 2.4 –схема подключения единичных индикаторов

Для отображения результатов, занимаемой позиции и номера пользователя будем использовать семисегментные индикаторы. Для уменьшения количества портов будем использовать динамическую индикацию для семисегментных индикаторов. В этом случае к каждому индикатору подключается порт подачи данных outsymи порт для стробированияoutnum.

Архитектура вывода представлена на рисунке 2.5. Дисплей состоит из восемнадцати семисегментных индикаторов, на которые выводятся результаты пользователя.

Рисунок 2.5 – Подключение семисегментных индикаторов.

Для измерения времени нам понадобиться таймер. В составе микропроцессорного комплекта К1810 для реализации времязадающих функций предусмотрена БИС К1810ВИ54 (программируемый таймер (ПТ)). Условное графическое обозначение ПТ ВИ54 представлено на рис 2.6. Архитектура таймера представлена на рис 2.7.

Рисунок 2.6 – Условное графическое обозначение ПТ ВИ54

Рисунок 2.7 – Архитектура подключения таймера

Назначение выводов ПТ.

D7 – D0 - выводы данных.

R

D

– чтение. Используется для чтения

содержимого внутренних регистров ПТ.

D

– чтение. Используется для чтения

содержимого внутренних регистров ПТ.W

R

– запись. Используется для загрузки

данных в регистры ПТ.

R

– запись. Используется для загрузки

данных в регистры ПТ.C

S

– выбор кристалла.

S

– выбор кристалла.A1 – A0 – адресные входы, по которым осуществляется адресация к одному их каналов.

<A1, A0> = <0,0> - адрес канала 0;

<A1, A0> = <0,1> - адрес канала 1;

<A1, A0> = <1,0> - адрес канала 2;

<A1, A0> = <1,1> - признак загрузки управляющих слов и команд.

CLK2 – CLK0 – входы тактовых импульсов для управления счетчиком. Срез сигнала на входе CLK приводит к уменьшению содержимого счетчика на единицу.

GATE2 –GATE0 – входы разрешения счета. Сигнал GATE =1 разрешает счет, а GATE=0 запрещает счет и состояние счетчика при этом не меняется.

OUT2 –OUT0 – выходы счетчика. При равенстве счетчика 0 вырабатывается сигнал на выходе этого счетчика, сигнализирующий об окончании счета.

Программируемый таймер К1810ВИ54 включает три канала, каждый из которых состоит из трех 16-разрядных регистров CR,CE,OLи двух 8-разрядных регистровRSWиRS.

CR- регистр пересчета. Служит для хранения констант пересчета. При программировании ЦП записывает в этот регистр константу, соответствующую времени появления сигнала на выходе счетчика.

CE– регистр – счетчик, работающий в режиме вычитания. Изменение содержимогоCEосуществляется по срезу сигналаCLKприGATE=1. При программировании содержимое регистраCRзагружается в регистрCEдля счета.

OL– выходной (буферный) регистр счетчика. Служит для запоминания и хранения мгновенного хранения счетчикаCE, которое в любой момент времени может быть записано командой «Защелка» или «Чтение состояние канала». После выполнения этих команд содержимое регистраOLможет быть прочитано ЦП без остановки дальнейшего счета в регистреCE.

RS– регистр состояния канала. Содержимое этого регистра является словом состояния канала и его можно считывать в ЦП с помощью команды «Чтение состояния канала».

RSW– регистр управляющего слова. Предназначен для записи и хранения управляющего слова, определяющего режим работы канала.

При посылке ЦП в ПТ управляющей информации состояние сигналов на линиях A1,A0 должно быть 1,1. Управляющая информация может быть следующего содержания: управляющее слово CW, команда «Защелка», команда «Чтение состояния канала».Таймер может работать в одном из шести предусмотренных режимов. Для реализации данной задачи наиболее подходит первый режим.

Режим 1(программируемый ждущий мультивибратор). При загрузке

управляющего слова выход OUTустанавливается в 1. После загрузки константы пересчетаNв регистрCRпереход из 0 в 1 сигнала на входеGATEвызывает загрузку регистраCR. На выходеOUTпроисходит переход из 1 в 0 и запускается счетCE. Когда счетчик достигнет 0, на выходеOUTформируется высокий уровень сигнала. Таким образом, результатом работы канала в режиме 1 является формирование отрицательного импульса на выходеOUTдлительностью равнойNпериодов синхронизации. Режим 1 является режимом с перезапуском. По каждому фронту сигналаGATEрегистрCEперезагружается содержимымCR.

Для работы с таймером будет использоваться три порта: outdata– порт записи константы пересчета,indata– чтение содержимого счетчика иoutcomand– порт передачи управляющего слова.

3 Разработка аппаратного обеспечения устройства

Разработка аппаратного обеспечения устройства включает в себя следующие этапы:

– разработка структурной электрической схемы устройства;

– разработка функциональной электрической схемы устройства;

– разработка принципиальных электрических схем устройства;

– расчет дискретных элементов.

Основная элементная база определяется типом микропроцессора. Поскольку тип микропроцессора К1810ВМ88 указан в задании, то в качестве основной элементной базы для построения устройства будем использовать микросхемы МПК БИС К1810, к которому относится этот микропроцессор.

3.1 Разработка структурной электрической схемы

Проектируемое устройство является типовой МПС. Поэтому в его состав входят центральный процессор (ЦП), память (программируемый таймер (ПТ), ОЗУ и ПЗУ) и интерфейс, объединенные шинами адреса, данных и управления. Полная структурная схема устройства приведена на чертеже КП.МПС.000000.09.12Э1 (Приложение Б). Эта схема разработана на основе типовой структуры МПС и представления разрабатываемого устройства в виде «черного ящика» (рисунок 1.1).

Все внешние устройства: кнопки управления, двоичные индикаторы и единичные индикаторы.

В ПЗУ хранится программа работы устройства. Центральный процессор считывает команды этой программы и выполняет их. Это обеспечивает управление ходом вычислительного процесса и решение поставленной задачи. При этом через интерфейс считывается входная информация, которая обрабатывается процессором и выводится на индикаторы. ОЗУ предназначено для хранения промежуточных данных, управляющих признаков и системной информации. Распределение адресного пространства между ПЗУ и ОЗУ осуществляется старшей адресной линией A19. При этом ОЗУ выбирается при A19=0, а ПЗУ – при A19=1. Следовательно, ОЗУ расположено в младшей половине, а ПЗУ – в старшей половине адресного пространства. Расположение ПЗУ в старшей половине адресного пространства необходимо для обеспечения начального запуска программы при включении устройства. Для определения времени реакции нам потребуется таймер. В составе микропроцессорного комплекта К1810 для реализации времязадающих функций предусмотрена БИС К1810ВИ54 (программируемый таймер). Так как других устройств вызывающих прерывания в нашем устройстве нет, то в контроллере прерываний нет необходимости.

3.2 Разработка функциональной электрической схемы

Функциональная схема раскрывает построение блоков структурной схемы, т. е. входящие в них функциональные узлы и связи между ними.

Полная функциональная схема проектируемого устройства приведена на чертеже КП.МПС.000000.09.12Э2 (Приложение В).

В состав процессора входят следующие функциональные узлы: системный генератор (SG), микропроцессор (CPU), регистр адреса (RGA), буфер данных (BD), дешифратор управляющих сигналов (DC) и цепь автоматического сброса.

Системный генератор SG обеспечивает формирование тактовой импульсной последовательности CLK, обеспечивающей функционирование всего устройства. Кроме того, он формирует сигнал готовности READY, поступающий на вход микропроцессора CPU, и сигнал системного сброса RESET, который используется для установки микропроцессора в начальное состояние после включения устройства.

Для включения микропроцессора, прежде всего, требуется стабильный генератор тактовых импульсов и цепь сброса, которая при включении будет удерживать линию RESETв активном состоянии 50 мкс. Для организации шины адреса необходимо использовать адресный регистр, чтобы отделить данные от адреса. Запись адреса в регистр осуществляется по сигналуALE. Для организации шины данных используется двунаправленный шинный буфер, который задает направление передачи данных. Так как в начале каждого цикла шины сначала выдается адрес, то буфера шины данных необходимо активировать по сигналуDEN-. Направление передачи данных задается линиейOP/IP-. Для организации шины управления используется дешифратор, который на основе трех сигналов определяет к какому адресному пространству идет обращение и тип обращения.

Для организации стандартного интерфейса используются регистры, называемые портами. Тип порта определяется внешней логикой, подключаемой к стробирующему входу и входу записи.

Память организуется в виде одного банка памяти разделенного пополам адресной линией A19.

Выходы портов вывода и входы портов ввода подключены к устройствам вывода и устройствам ввода соответственно.

В качестве таймера используем микросхему К1810ВИ54, максимальная частота работы данной микросхемы составляет 2,5 МГц., что нас вполне устраивает. Данную частоту возьмем с выхода генератора PCLK. Один из каналов будем использовать в качестве формирователя тактовых импульсов заданной частоты, а другой в качестве счетчика. Разработанная функциональная схема – КП.МПС.000000.09.12Э2. Она приведена в приложении В.

3.3 Принципиальная схема

Данная схема разрабатывается на основе функциональной схемы.

Микропроцессор ВМ88 (DD2) включен в минимальном режиме, так как разрабатываемая МПС является однопроцессорной. Для организации работы микропроцессора используется тактовый генератор ГФ84 (DD1). Он обеспечивает генерацию стабильных тактовых импульсов для микропроцессора и стандартного интерфейса. В качестве времязадающей цепи используется кварцевый резонаторBQ.

Помимо генерации тактовых импульсов, ГФ84 имеет входы для цепи сброса, чтобы обеспечивать правильный механизм сброса, синхронизированный с выходом тактовых импульсов микропроцессора. RC-цепь служит для удержания линииRESETв активном состоянии в течении 50 мкс.

Регистр адреса состоит из двух регистров ИР82, которые организуют 16-разрядную шину адреса, где 15 линий отводятся под адресацию памяти и 1 линия под разделение адресного пространства памяти.

Шинный буфер ВА86 организует двунаправленную восьмиразрядную шину данных, что полностью соответствует техническим требованиям микропроцессора ВМ88.

Шина управления реализована на дешифраторе КР1533ИД7. Порты ввода/вывода реализованы на регистрах ИР82. Если порт используется как порт ввода, то на вход записи поступает сигнал синхронизации интерфейса, генерируемый ГФ84, а на вход разрешения выхода, комбинация сигналов IOR- и одной из адресных линий, обеспечивающая уровень «0» при обращении к порту. Если порт используется как порт вывода, то выход всегда разрешен, а на вход записи подается комбинация сигналовIOW- и одной из адресных линий, обеспечивающая уровень «1» при обращении к порту.

В качестве портов ввода/вывода используются регистры К1810ИР82 (DD12..DD18). Управление портами вывода производится с помощью логических элементов ИЛИ К1531ЛЕ1. Порты ввода управляются с помощью элементов ИЛИ-НЕ К1531ЛЛ1.

К каждым четырем DIP-корпусам цифровых микросхем подключается керамический конденсаторКМ-5б-П33-0,1 мкФ ± 10%(C4..C22). Для подавления низкочастотных помех используется электролитический конденсаторК53-14-25-10 мкФ ±20%(С3), который устанавливаются в непосредственной близости от разъема.

Для подключения схемы микроЭВМ к схеме устройства используется X1 –вилка2РМ 14/4/1 НЩО.355.023ТУ.

В качестве кнопок выберем кнопки КП-1 (S1-S8).

В качестве семисегментных индикаторов выберем элементы АЛС333Б (HG1 –HG8). В качестве единичных индикаторов выберем светодиоды АЛ307БМ (VD1 – VD3). Резисторы (R25-R27) служат для ограничения тока светодиодов.

3.4 Расчет дискретных электрорадиоэлементов

Наиболее критичными по быстродействию

являются элементы памяти. Быстродействие

элементов памятихарактеризуется

временем выборки адреса. Для выбранных

ПЗУ К573РФ5

![]() нс, а для ОЗУ К537РУ10

нс, а для ОЗУ К537РУ10![]() нс. ПЗУ имеет худшее быстродействие,

поэтому рабочая частота должна выбираться

с учетом его времени выборки адреса.

нс. ПЗУ имеет худшее быстродействие,

поэтому рабочая частота должна выбираться

с учетом его времени выборки адреса.

|

|

(3.1) |

Исходя из этого, выберем

![]() = 2 МГц. Тогда

= 2 МГц. Тогда![]() Выберем кварцевый резонаторРК169МВ-7АП-6МГц.

Выберем кварцевый резонаторРК169МВ-7АП-6МГц.

Для компенсации индуктивности резонатора и снятия с него постоянной составляющей напряжения последовательно с ним включается С1 – конденсатор КМ-5б-П33-10пФ±5%.

Для обеспечения запуска программы с начального адреса при включении МПС используется RC– цепь автоматического сброса, состоящая из элементовR1,C2.

RC-цепь автоматического сброса рассчитывается по следующим формулам:

|

|

(3.2) |

Примем

![]() ,

,![]() и подставим в формулу (3.3), получим:

и подставим в формулу (3.3), получим:

|

где

|

(3.3) |

Из формулы (3.3) следует:

![]() .

Так как конденсаторы имеют меньший

диапазон значений, сначала выберем

конденсатор

.

Так как конденсаторы имеют меньший

диапазон значений, сначала выберем

конденсатор![]() :

:![]() .

Соответственно сопротивление

.

Соответственно сопротивление![]() :

:![]() .

.

Постоянная времени этой цепи выбрана из условия получения требуемой длительности первоначального сигнала сброса (не менее 50 мкс). Для быстрого разряда конденсатора C2 и восстановления исходного состояния цепи автоматического сброса при пропадании напряжения питания +5В используется диод КД522А (VD1). В результате этого при кратковременном пропадании питающего напряжения обеспечивается перезапуск программы с начального адреса.

В качестве устройства ввода выступают кнопки без фиксации. Аналогичным образом рассчитываются резисторы R28 – R34, обеспечивающие уровень логической «1» на выходах не нажатых кнопок. Применим второй закон Кирхгофа для расчета резистораR28:

![]() ,

(3.4.6)

,

(3.4.6)

где Е– напряжение питания (Е= 5 В);n– количество входов

микросхем, подключённых к резистору (n

= 1);![]() – входной ток высокого уровня (

– входной ток высокого уровня (![]() =

30 мА);

=

30 мА);![]() – входное напряжение высокого уровня

(

– входное напряжение высокого уровня

(![]() = 2,4 В).

= 2,4 В).

Из выражения (3.4.5) относительно R28, получим формулу для минимального значения сопротивления:

(3.4.7)

(3.4.7)

Подставив известные значения в формулу (3.4.7), получим:

![]() (кОм).

(кОм).

Выберем резистор R28 = 10 кОм [12].

![]() (Вт)

(Вт)

После расчета электрической мощности этих резисторов R28 – R34выберем резисторы С2-23-0,125-10 кОм ± 5 % [12].

Рассчитаем элементы дисплея. Транзисторы VT1 –VT8 активируют отдельный сегмент на знакосинтезирующем индикаторе. При динамической индикации ток через один сегмент рассчитывается по формуле:

![]() (3.4.8)

(3.4.8)

Для выбранных индикаторов АЛС333Б

![]() мА,k= 15 – количество

индикаторов. Подставив значения в

(3.4.8), получим:

мА,k= 15 – количество

индикаторов. Подставив значения в

(3.4.8), получим:

![]() (мА).

(мА).

Для транзисторов VT1 –VT8 должно

выполняться условие![]() ,

поэтому выбираем в качестве транзисторовVT1 –VT8 транзисторыКТ361А

с

,

поэтому выбираем в качестве транзисторовVT1 –VT8 транзисторыКТ361А

с

![]() =0,5

В,

=0,5

В,![]() =0,4

В и коэффициентом усиления по токуβ=100. [15].

=0,4

В и коэффициентом усиления по токуβ=100. [15].

Рассчитаем транзисторы VT9 –VT16

которые осуществляют выбор конкретного

индикатора. Для транзисторовVT9 –VT16 должно выполняться условие![]() ,

где 8 – количество сегментов

индикатора. Подставив значения, получим,

что

,

где 8 – количество сегментов

индикатора. Подставив значения, получим,

что![]() (мА),

поэтому выбираем в качестве транзисторовVT9 –VT16 транзисторыКТ6116В

с

(мА),

поэтому выбираем в качестве транзисторовVT9 –VT16 транзисторыКТ6116В

с

![]() =0,5

В, и коэффициентом усиления по токуβ=180,

=0,5

В, и коэффициентом усиления по токуβ=180, ![]() мА.

мА.

В расчете из максимального

значения по току выберем токоограничительный

диод SB060-E3/73 ![]() мА,

мА,![]() В.

В.

Рассчитаем номиналы резисторов R9 –R16, которые ограничивают ток через сегмент. По второму закону Кирхгофа:

![]() ,

(3.4.9)

,

(3.4.9)

![]() .

(3.4.10)

.

(3.4.10)

Подставив значения в формулу (3.4.10), получим:

![]() (Ом).

(Ом).

На основании полученных данных в качестве резисторов R9 –R16 выберем из справочника [12] резисторы С2-23-0,25-25 Ом ± 5 %.

Рассчитаем номиналы резисторов R1 –R8.

![]() ,

(3.4.11)

,

(3.4.11)

![]() ,

(3.4.12)

,

(3.4.12)

![]() ,

(3.4.13)

,

(3.4.13)

где S– степень насыщения транзистора,S= 1,5÷2,β– коэффициент усиления по току,β=100. ПримемS= 1,5. Подставив значения в (3.4.13), получим:

![]() (кОм).

(кОм).

На основании полученных данных в качестве резисторов R1 –R8 выберем из справочника [12] резисторы С2-23-0,125-2,4 кОм ± 5 %.

Номиналы резисторов R17 –R24 в цепях базы транзисторов рассчитываются следующим образом:

![]() ,

(3.4.14)

,

(3.4.14)

![]() ,

(3.4.15)

,

(3.4.15)

![]() ,

(3.4.16)

,

(3.4.16)

где![]() ,

,![]() .

Подставив значения в (3.4.16), получим:

.

Подставив значения в (3.4.16), получим:

![]() (кОм).

(кОм).

На основании полученных данных в качестве резисторов R17 –R24 выберем из справочника [12] резисторы С2-23-0,125-470 Ом ± 5 %.

Рассчитаем резисторы для ограничения тока светодиодных индикаторов R25 –R27. По второму закону Кирхгофа для одноконтурной цепи, в которую входит резистор, можно записать:

![]() , (3.4.17)

, (3.4.17)

где

![]() ,

,![]() – ток и напряжение свечения светодиода.

Из формулы (3.4.17) получаем:

– ток и напряжение свечения светодиода.

Из формулы (3.4.17) получаем:

![]() .

(3.4.18)

.

(3.4.18)

Для выбранного светодиода АЛ307БЛ

![]() = 12 мА,

= 12 мА,![]() = 2 В. Тогда, подставив значения в (3.4.18),

получим

= 2 В. Тогда, подставив значения в (3.4.18),

получим

![]() После расчета рассеиваемой мощности в

качестве ограничительных резисторовR25 –R27

выберем из справочника [12] резисторы

С2-23-0,125-250 Ом ± 5 %.

После расчета рассеиваемой мощности в

качестве ограничительных резисторовR25 –R27

выберем из справочника [12] резисторы

С2-23-0,125-250 Ом ± 5 %.

Перечень элементов для устройства приведен в Приложении Д.

4 Разработка программного обеспечения устройства

4.1 Представление программы в виде черной сферы

Так как в проектируемом устройстве все функции выполняются программным путем, то представление программы в виде «черной сферы» будет практически полностью совпадать с представлением устройства в виде «черного ящика».

Представление программы проектируемой МПС в виде «черной сферы» приведено на рисунке 4.1.

Рисунок 4.1 – Представление разрабатываемого устройства в виде «черного ящика»

4.2 Статическая модель программы

Анализируя требования к программе, а так же с учетом произведенной декомпозиции получим исходную схему представления поставленной задачи, которая представлена на рисунке 4.2.

Рисунок 4.2 – Исходная схема представления задачи «Электронные шахматные часы»

Из данной схемы следует, что проектируемая программа должна обрабатывать входную информацию с кнопок управления и отображать выходную информацию на дисплеях и двоичных индикаторах. Исходя из этих сведений, произведем декомпозицию исходной схемы представления программы и получим структурную схему после первого этапа декомпозиции, которая представлена на рисунке 4.3.

Рисунок 4.3 – Структурная схема программы

(после первого этапа декомпозиции)

Рисунок 4.3 – Структурная схема программы

(после первого этапа декомпозиции)

Разобьем процесс вывод времени на подпроцессы: вывод количества ходов, вычисление и вывод времени. Контрольный процесс включает в себя формирование флагов управления, а также сброс и задержку времени. Процесс формирования времени разобьём на подпроцессы: декрементирование и расчет.

Рисунок 4.4 – Статическая модель программы (после второго этапа декомпозиции)

Анализируя выделенные в результате второго этапа подзадачи, можно сделать вывод, что все они имеют чётко определённые функции и не требуют дальнейшей детализации. Следовательно, декомпозиция программы работы устройства выполнена полностью, в результате чего построена её статическая модель. Для дальнейшего проектирования программы работы устройства необходимо определить структуру данных во всех наборах её статической модели.

4.3 Структура данных программы

Рациональная форма представления данных определяется формой представления входной и выходной информации.

Результаты разработки структуры данных программы проектируемого устройства приведены в таблице 4.3.1.

|

Наименование данных |

Символьное имя |

Формат данных |

Кодирование данных |

примечание | |||||||

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

| |||

|

Время первого игрока |

timeL |

6 байт |

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Накопительная часть |

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Младшая цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Старшая цифра | |||

|

Время второго игрока |

timeR |

6 байт |

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Младшая цифра |

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Старшая цифра | |||

|

Хранение времени первого игрока |

SaveTimeL |

6 байт |

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Младшая цифра |

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Старшая цифра | |||

|

Количество ходов первого игрока |

xodL |

3 байта |

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Младшая цифра |

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Старшая цифра | |||

|

Количество ходов второго игрока |

xodR |

3 байта |

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Младшая цифра |

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Средняя цифра | |||

|

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Старшая цифра | |||

|

Тип партии |

variant |

байт |

0 |

0 |

0 |

0 |

* |

* |

* |

* |

Позиционный код |

|

Номер пользователя |

nomberuser |

2 байта |

0 0 |

0 0 |

0 0 |

0 0 |

* * |

* * |

* * |

* * |

Десятичное число от 00 до 99 |

|

Место пользователя |

mesto |

2 байта |

0 0 |

0 0 |

0 0 |

0 0 |

* * |

* * |

* * |

* * |

Десятичное число от 00 до 99 |

|

Флаг начала игры |

flstart |

байт |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

Включен Выключен |

|

Флаг ручной установки |

flagrset |

байт |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

Включен Выключен |

|

Флаг неверной установки времени |

flflase |

байт |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

Включен Выключен |

|

Флаг текущего хода |

flreverse |

байт |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

1 0 |

Включен Выключен |

|

Образ кнопок |

obraz |

байт |

* |

* |

* |

* |

* |

* |

* |

* |

Каждый бит отвечает за свою кнопку |

|

Вспомогательная переменная |

old |

байт |

* |

* |

* |

* |

* |

* |

* |

* |

Хранит старое значение кнопок |

Таблица 4.3.1 – Структура данных программы «Электронные шахматные часы».

4.4 Алгоритмизация программы

4.4.1 Алгоритмы макроуровня

Алгоритм одноуровневого представления программы изображен на рисунке 4.4.1. Он отображает распределение исполнителей, выделенных на этапе декомпозиции, по времени. Многоуровневый алгоритм представления изображен на рисунке 7.2. Помимо распределения исполнителей по времени, он отображает уровни вложенности подпрограмм.

Рисунок 4.4.1 –Алгоритм работы программы (одноуровневое представление)

Рисунок 4.4.2 – Алгоритм работы программы

4.4.2 Алгоритмы исполнителей

В данном разделе представлены алгоритмы исполнителей, которые непосредственно вызываются в программе.

Итак, после определения основных программных исполнителей необходимо

разработать алгоритм каждого из них.

Подзадача «Функциональная подготовка» (podgotovka) производит инициализацию флагов и начальных значений переменных.

Подзадача «Ввод» (readkey) осуществляет считывание данных с кнопок, расположенных на лицевой панели устройства и формирует соответствующий их состоянию образ в памяти. Граф-схема представлена на рисунке 4.4.2.

Рисунок 4.4.2 – Граф-схема алгоритма «ввод»

Подзадача «контрольный процесс» (control) осуществляет анализ образа клавиатуры и формирует значение флагов. Граф-схема представлена на рисунке 4.4.3.

Рисунок 4.4.3 – Граф-схема алгоритма «контрольный процесс»

Подзадача «установка времени» (settime) осуществляет изменение номера пользователя. Граф-схема представлена на рисунке 4.4.4.

Рисунок 4.4.4 – Граф-схема алгоритма «установка времени»

Подзадача «сохранение времени» (savetime) осуществляет сохранение переменных времени игроков. Граф-схема алгоритма представлена на рисунке 4.4.5.

Рисунок 4.4.5 – Граф-схема алгоритма «сохранение времени»

Подзадача «вычисление времени» (timing) осуществляет получение времени игроков. Граф-схема алгоритма представлена на рисунке 4.4.6.

Рисунок 4.4.6 – Граф-схема алгоритма «вычисление времени»

Подзадача «обратное время» (revers) осуществляет генерацию случайного числа. Граф-схема алгоритма представлена на рисунке 4.4.7.

Рисунок 4.4.7 – Граф-схема алгоритма «обратное время»

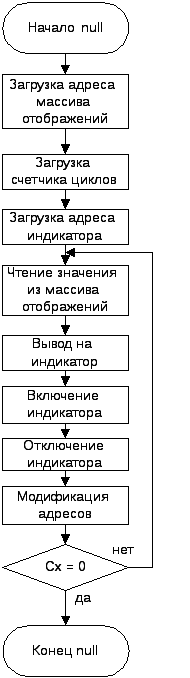

Процедура «вывод времени на индикаторы» (Display) осуществляет формирование образа переменнойtimeи вывода его на семисегментные индикаторы. Граф-схема представлена на рисунке 4.4.8.

Рисунок 4.4.8.– Граф-схема алгоритма «вывод времени на индикаторы»

Процедура «вывод времени на индикаторы» (Display) осуществляет формирование образа переменнойtimeи вывода его на семисегментные индикаторы. Граф-схема представлена на рисунке 4.4.9.

Рисунок 4.4.9.– Граф-схема алгоритма «вывод времени на индикаторы»

Процедура «вывод сообщения» (null) вызывается в случаи отсутствия результата по выбранному значению места или пользователя. Граф-схема представлена на рисунке 4.4.10.

Рисунок 4.4.10.– Граф-схема алгоритма «вывод сообщения»

,

,