Билет №20 Вопрос №1

Техническое обеспечение микропроцессорных систем.

Структура МП определяет состав и взаимодействие основных устройств и блоков, размещённых на его кристалле. В эту структуру входят:

Центральный процессор, главное вычислительное устройство, состоящее из устройства управления и одного или нескольких операционных устройств.

Внутренняя память (кэш-память, блоки оперативной и постоянной памяти).

Интерфейсный блок, обеспечивающий выход на системную шину и обмен данными с внешними устройствами через параллельные или последовательные порты ввода-вывода.

Периферийные устройства (таймерные модули, аналогово-цифровые преобразователи, специализированные контроллеры).

Вспомогательные схемы (генератор тактовых импульсов, схемы для выполнения отладки и тестирования, сторожевой таймер и ряд других)

В современных МП реализуются следующие варианты архитектур.

CISC – архитектура реализована во многих типах МП, выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации. Типичным примером CISC – процессоров являются МП семейства Pentium. Они выполняют более 200 команд разной степени сложности, которые имеют размер от одного до пятнадцати байт и обеспечивают более 10 различных способов адресации.

RISC – архитектура отличается использованием ограниченного набора команд фиксированного формата. Такие процессоры обычно реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта. Также значительно сокращается число используемых способов адресации. При этом для сокращения количества обращений к памяти RICS процессоры имеют увеличенный объём внутреннего РЗУ- от 32 до нескольких сотен регистров, тогда как в CISC процессорах число регистров общего назначения обычно составляет 8-16. Указанные достоинства RISC архитектуры привели к тому, что во многих современных CISC процессорах используется RISC ядро, выполняющее обработку данных. При этом поступающие сложные разноформатные команды предварительно преобразуются в последовательность простых RISC операций, быстро выполняемых этим процессорным ядром. Таким образом, RISC – это сокращенный набор команд, уменьшенный фиксированный формат команд, алгоритмическая ориентация на конвейерные структуры с большим числом уровней совмещение в конвейере, что позволяет выполнять команды за один машинный цикл. RISC – архитектурой обеспечивают выигрыш в производительности по сравнению с СISC – процессорами при реализации относительно простых алгоритма управления, но в то же уступают последнем в областях применения, где требуется выполнение сложных расчётов и алгоритмов управления с элементами «искусственного интеллекта». Поэтому лучше универсальные – СRISC. Граница между суперскалярным и СRISC – архитектурами очень условна.

VLIW – архитектура. Ее особенностью является использование очень длинных команд (до 128 бит и более), отдельные поля которых содержат коды, обеспечивающие выполнение различных операций. Таким образом, одна команда вызывает выполнение сразу нескольких операций параллельно в различных операционных устройствах, входящих в структуру микропроцессора.

Принстонская архитектура, которая часто называется архитектурой Фон-Неймана, характеризуется использованием общей оперативной памяти для хранения программ, данных, а так же для организации стека. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают команды и данные.

Гарвардская архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. Недостатки данной архитектуры связаны с необходимостью проведения большого числа шин, а также с фиксированным объёмом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи. Гарвардская архитектура получила широкое распространение в микроконтроллерах – специализированных микропроцессорах для управления различными объектами, рабочая программа которых хранится в отдельном ПЗУ.

Во внутренней структуре современных высокопроизводительных микропроцессоров реализуется конвейерный принцип выполнения команд. При этом процесс выполнения команд разбивается на ряд этапов.

1) Выборка очередной команды

2) Декодирование выбранной команды

3) формирование адреса операнда

4) Приём операнда из памяти

5) Выполнение операции

6) Размещение результата в памяти

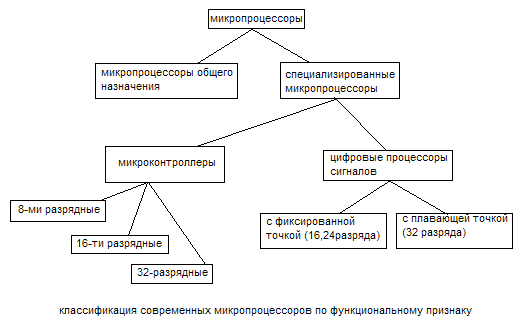

Выделяются 2 класса: микропроцессоры общего назначения и специализированные микропроцессоры (Рис 2.1.2)

Микропроцессоры общего назначения предназначены для решения широкого круга задач обработки разнообразной информации. Их основной областью являются персональные компьютеры, рабочие станции, серверы и другие рабочие системы массового применения.

Микроконтроллеры являются специализированными микропроцессорами, которые ориентированы на реализацию устройств управления, встраиваемых в разнообразную аппаратуру.

Классификация современных микропроцессоров по функциональному признаку

8-разрядные микроконтроллеры представляют наиболее многочисленную группу этого класса микропроцессоров, которые имеют относительно низкую производительность, которая, однако, вполне достаточна для решения широкого круга задач управления различными объектами. Это простые и дешёвые микроконтроллеры, ориентированные на использование в относительно несложных устройствах массового выпуска. Основными областями их применения являются бытовая и измерительная техника, промышленная автоматика, автомобильная электроника, теле, видео, аудиоаппаратура, средства связи. Для этих микроконтроллеров характерна реализация Гарвардской архитектуры, где используется отдельная память для хранения программ и данных.

16-разрядные микроконтроллеры во многих случаях являются усовершенствованной модификацией своих 8-разрядных прототипов. Они характеризуются не только увеличенной разрядностью обрабатываемых данных, но и расширенной системой команд и способов адресации, увеличенным набором регистров и объёмом адресуемой памяти. Основная сфера применения таких микроконтроллеров- сложная промышленная автоматика, телекоммуникационная аппаратура, медицинская и измерительная техника.

32-разрядные микроконтроллеры содержат высокопроизводительный процессор, соответствующий по своим возможностям младшим моделям микропроцессоров общего назначения. В ряде случаев процессор, используемый в этих микроконтроллерах, аналогичен CISC или RISC – процессорам, которые выпускаются или выпускались ранее в качестве микропроцессоров общего назначения.

Во внутренней структуре этих микроконтроллеров реализуется Принстонская или Гарвардская архитектуры. Входящие в их состав процессоры могут иметь CISC- или RISC- архитектуру, а некоторые из них содержат несколько исполнительных конвейеров.

Основные локальные интерфейсы периферийных устройств

|

Категория |

Международное обозначение |

Отечественное обозначение |

Примечания |

|

Параллельный двухточечный |

Centronix BS4421 |

ИРПР-М ИРПР |

8-разрядные 16-разрядные данные |

|

Последовательный двухточечный |

CL (Current Loop) RS232C (нуль-модем) |

ИРПС(токовая петля) Стык С2 (нуль-модем) |

Наиболее распространённые |

|

Последовательный многоточечный |

RS422, RS423, RS485 USB, USB2 |

Стык С2-4С |

|

Для дуплексной связи (одновременно передачи в двух противоположных направлениях) используется четырехпроводная линия. Такой принцип используется в интерфейсе ИРПС. Интерфейс содержит цепь 1 «Передаваемые данные» (Пд+/Пд-) и цепь 2 «Принимаемые данные» (Пр+/Пр-). Интерфейс не регламентирует типы применяемых кабелей и разъемов.

RS232 – Этот тип интерфейса применим для синхронной и асинхронной связи между устройствами в симплексном, полудуплексном и дуплексном режимах. Стандарт регламентирует состав, назначение и обозначение линий (цепей) интерфейса, их нумерацию, электрические характеристики, обозначения и уровни сигналов интерфейса, скорости передачи данных и тип используемых разъемов. Соединения по интерфейсу RS-232C реализуются через стандартные 9- или 25-контактные разъемы типа DB9 или DB25. Интерфейсы ИРПС и RS232C отличаются лишь параметрами сигналов «0», «1». Информационный сигнал в ИРПС - ток, когда «0» соответствует 2 мА, «1» - 20 мА. В RS232C «0» соответствует -12 В, «1» - +12 В (допуск ±[8..14] В). Скорость и дальность передачи токового сигнала больше, чем сигнала по напряжению. Интерфейсы RS232C и ИРПС легко совместимы между собой.

Многоточечный интерфейс RS485 отличается от двухточечных тем, что здесь иcпользуется балансная (симметричная) линия связи . Параметры сигнала А – В :

± 5 в ( «1» -+5в - 5в; «0» -5в - +5в).

Балансный интерфейс является значительно более помехозащищенным, чем небалансный, так как при вычитании потенциала одной информационной шины из потенциала другой на входе операционного усилителя уничтожается синфазная помеха, наиболее характерная для рядом расположенных проводников. Поэтому именно балансный интерфейс используется для организации передачи данных на большие расстояния.

Скорость передачи информации стандартизирована, измеряется в бит/с=бод:

1200, 2400, 4800, 9600, 19200, 57600 бод, - ИРПС, RS232

62.5, 375, 1000, 2400 Кбод - RS485.