Л2 Организация процессора

.pdf

ЭВМ и ПУ. Лекция 2 |

Щемелева Т.К. |

ЛЕКЦИЯ 2. ОРГАНИЗАЦИЯ ПРОЦЕССОРА

Новые понятия: логический элемент; комбинационная схема;

запоминающий элемент; схема с памятью; узел (блок); дешифратор; регистр; счетчик; устройство; УУ с «жесткой» логикой; УУ с программируемой логикой; регистр команд; счетчик команд; регистр флагов; регистр адреса; микрокоманда; микрооперация; микропрограмма; стадии (этапы) выполнения команды;

Основные вопросы: 1. Основные типы логических схем аппаратуры

ЭВМ: Логические элементы. Узлы. Устройства. .2. Функциональная организация процессора: Арифметико-логическое устройство (АЛУ). Устройство управления (УУ). 2. Принцип микропрограммного управления. 4. Структурная организация процессора. 5. Стадии (этапы) выполнения команды.

Для того чтобы понять, как управлять аппаратными средствами процессора на языке ассемблер необходимо изучить их возможности с точки зрения программиста.

2.1 Основные типы логических схем аппаратуры ЭВМ.

Преобразование информации в ЭВМ выполняется в электронных схемах, имеющих различную степень сложности. Схемы являются цифровыми, т.е. они обрабатывают сигналы дискретного вида, каждый из которых может принимать в любой момент времени только одно из двух логических значений – единицу (1) или нуль (0). На физическом уровне для кодирования 1 и 0 используют два числовых значения какого-либо параметра электрического сигнала, обычно напряжения. Многие электронные технологии используют для кодирования

единицы, например, напряжение в |

2-2.5 вольта, |

а |

для нуля – 0 вольт так, как |

показано на рис.2.1. Информация |

объемом |

1 |

бит передается от одной |

электронной схемы к другой по одному проводнику. Представление изменений во времени дискретного сигнала называется временной (ударение на последний слог) диаграммой сигнала. На рис. 2.1. показан передаваемый по проводнику (линии) некоторый дискретный сигнал А, который до момента времени t1 имел значение логической 1, а после t1 принял значение логического 0.

U(в)

А

1

0

t

t1

Рисунок 2.1. - Способ кодировки логических сигналов 1 и 0.

С помощью временной диаграммы можно отобразить изменения во времени сигналов на входах и выходах электрических схем ЭВМ любого уровня:

1

ЭВМ и ПУ. Лекция 2 |

Щемелева Т.К. |

принципиальных, функциональных, структурных. Временная диаграмма есть один из способов графического описания закона работы любой схемы ЭВМ. Напомним и другие известные способы описания логики работы цифровых схем:

схемы (блок-схемы) алгоритмов;

логические функции;

графы автоматов;

таблицы истинности и др.

По функциональной сложности цифровые схемы принято делить на

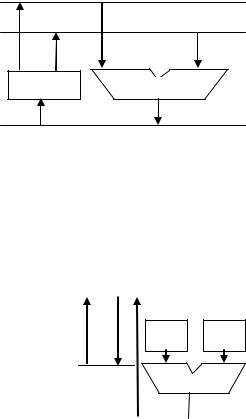

элементы, узлы (блоки) и устройства. Отметим здесь, не раскрывая подробнее, что по уровню детализации электрические схемы делят на структурные, функциональные и принципиальные. По стандартам в технической документации цифровые схемы изображаются так, как показано на рис.2.2а): в виде прямоугольника, причем входы обозначаются линиями слева, а выходы – линиями справа. Однако ввиду разных причин в учебной литературе часто отступают от этих правил. Рассмотрим логику работы цифровых схем в указанном порядке.

2.1.1. Логические элементы.

Элемент - это простейшая схема, выполняющая операции над значениями двоичных переменных. Элементы делятся на логические, запоминающие и

вспомогательные.

Логические элементы (ЛЭ) выполняют двоичные (бинарные) операции, на основе которых осуществляются практически все преобразования информации в ЭВМ. В качестве логических элементов используются элементы И, ИЛИ, НЕ и другие, производные от них.

Запоминающий элемент (ЗЭ) хранит только одно логическое значение (0 или 1) одной двоичной переменной. В процессорах, интерфейсных схемах и некоторых типах ЗУ в качестве ЗЭ применяют триггеры различных типов.

Вспомогательные элементы усиливают или формируют сигналы стандартной формы, но, как правило, не выполняющие никаких логических функций.

|

СТ |

Q |

|

|

|

1 |

|

n |

|

|

|

|

+1 |

|

|

|

n |

а) б) Рисунок 2.2. - Условные графические обозначения цифровых схем

а) ЛЭ типа ИЛИ, б) суммирующего двоичного счетчика

2.1.2. Узлы

2

ЭВМ и ПУ. Лекция 2 |

Щемелева Т.К. |

Узлы состоят из ЛЭ и выполняют операции преобразования информации над несколькими двоичными переменными. В зависимости от состава узлы могут быть 2-х типов: комбинационного (комбинационные схемы — КС) или накапливающего (цифровые автоматы, т.е. схемы с памятью).

Узлы комбинационного типа состоят из ЛЭ. Их главная особенность заключается в том, что выходной сигнал (Y) в текущий такт времени зависит только от входных сигналов (X) в том же такте. Несмотря на кажущуюся примитивность логики работы КС, все основные преобразования информации в ЭВМ выполняются с их помощью. Это объясняется тем, что в основе преобразования данных заложено выполнение логических или арифметических операций. К типовым КС относятся сумматоры, дешифраторы, компараторы,

мультиплексоры и др. [1,§ 1.4.]. Например, типовой дешифратор –это схема с N входами и K выходами, причем на один двоичный N-разрядный код схема выставляет 1 только на одном из К выходов, а на остальные выставляет нули.

Узлы с памятью (автоматы) состоят из ЛЭ и ЗЭ. Информация, записанная в памяти автомата, называется состоянием автомата (Q). При работе автомата в его памяти накапливается обобщенная информация обо всех входных сигналах, поступивших к данному моменту времени, поэтому состояние автомата и выходной сигнал зависят от входных сигналов в текущий и предыдущие такты. Наличие памяти позволяет автомату выполнять многотактные заданные алгоритмы обработки данных.

Несколько узлов могут объединяться в функциональные блоки (например, блок сумматора может включать в себя собственно сумматор и регистр сумматора).

2.1.2.1Типовые узлы с памятью

Ктиповым узлам с памятью относятся регистры и счетчики.

Регистры предназначены для приема, временного хранения и выдачи

данных. Регистр – основная схема хранения информации не только в процессоре, но и в контроллере, адаптере и порту ЭВМ. Основу регистра составляют ЗЭ - триггеры, число которых равно разрядности хранимых в регистре данных, т.е. n- разрядный двоичный код хранится в n- разрядном регистре. Параллельным называют . n-разрядный регистр с одновременной (т.е. параллельной записью.) записью в него всех n разрядов двоичного кода. Параллельный регистр имеет наиболее простую схему. Обычно именно его называют просто регистром.

Кроме хранения двоичных кодов регистры могут выполнять сдвиг кодов на один или сразу на несколько разрядов, как в сторону старших, так и в сторону младших разрядов. Такие регистры называются сдвигающими.

На основе регистра строят схемы счета единиц (нулей) – счетчики. Счетчиком называется регистр, который «считает» входные сигналы, т.е. под действием каждого входного сигнала хранимый двоичный код изменяется на «1». В зависимости от направления счета счетчики могут быть суммирующими или вычитающими. Суммирующие счетчики при поступлении каждого входного импульса увеличивают показания (состояния каждого триггера, т.е. состояние счетчика) на единицу, вычитающие – уменьшают. Принято обозначать вход

3

ЭВМ и ПУ. Лекция 2 |

Щемелева Т.К. |

суммирующего счетчика «+1», а вычитающего - «-1» . Графическое обозначение суммирующего n-разрядного счетчика с прямыми и инверсными выходами приведено на рис. 2.1.б). На вход, обозначенный как +1, поступают суммируемые логические сигналы (единицы). С выхода счетчика Q, состоящего из n выходных линий, снимается состояние счетчика в виде n – разрядного двоичного кода.

2.2. Функциональная организация процессора

Схемы каждого устройства работают согласованно во времени. Это обеспечивается их синхронизацией периодическими сигналами генератора тактовых импульсов (ГТИ). Напомним, что такт – это период сигналов тактовой частоты. Если считать, что на рис. 2.1. показан один выходной сигнал ГТИ, то именно его продолжительность и составляет один такт.

Процессор является основным «мозговым» устройством ЭВМ, в котором исполняется считываемый из ОЗУ (ПЗУ) программный (исполняемый) кода, который получается в результате трансляции текста программы на каком-либо языке программирования. Процессор ЭВМ объединяет следующие блоки, которые традиционно называются тоже устройствами: устройство управления (УУ), арифметико-логическое устройство (АЛУ) и блоки регистров.

2.2.1. Арифметико-логическое устройство (АЛУ)

АЛУ предназначено для выполнения арифметических и логических операций над данными разного формата. В зависимости от характера выполняемой операций и формата данных различают несколько типов операций (см. лекцию 1), в т. ч.:

арифметические - над целыми числами (в форме с фиксированной с точкой);

арифметические - над вещественными числами (в форме с плавающей с точкой);

арифметические - над двоично-десятичными числами (операции десятичной арифметики, например, над числами в кодах ASCII);

логические.

Взависимости от набора операций и особенностей реализации алгоритмов их выполнения организация АЛУ может быть различной.

По характеру использования различают многофункциональные и блочные АЛУ. Многофункциональные АЛУ настраиваются на заданный тип операций с помощью управляющих сигналов. (Обратим внимание, что входы АЛУ для управляющих сигналов (а значит и сами сигналы) на схемах АЛУ в этой лекции не показаны). Блочные АЛУ включают в себя отдельные блоки для операций различного типа. Эти блоки могут работать параллельно, что повышает

быстродействие АЛУ, однако требует больших затрат на оборудование.

АЛУ строится на КС, поэтому в операциях над двумя операндами оба операнда должны устанавливаться на обоих входах АЛУ одновременно! На его выходе формируется результат преобразования операндов и признаки (условия), характеризующие результат. К таким признакам относятся, например, знак результата, равенство результата нулю и др. Признаки называют флагами.

4

ЭВМ и ПУ. Лекция 2 |

Щемелева Т.К. |

Основу АЛУ составляет двоичный сумматор для двоичных дополнительных кодов чисел, т.к. их суммирование составляет основу алгоритмов 4-х арифметических операций: сложение, вычитание, умножение, деление (см. лекцию 2 и [1, 1.3; 2,Гл.7.]). В зависимости от числа магистралей различают трех- , двух- и одномагистральные АЛУ. Рассмотрим особенности выполнения сложения в них.

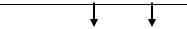

а) Трехмагистральное АЛУ

Структура трехмагистрального АЛУ (рис.2.3) позволяет выполнить за один такт чтение операндов из регистров блока РЕГИСТРЫ (Р-ры) на АЛУ, их суммирование в АЛУ и сохранения суммы в регистре того же блока. Однако три многоразрядные магистрали занимают значительную часть кристалла микросхемы, поэтому такие схемы редко используются.

A

B

Р-ры |

АЛУ |

|

C

Рисунок - 2.2. Трехмагистральное АЛУ

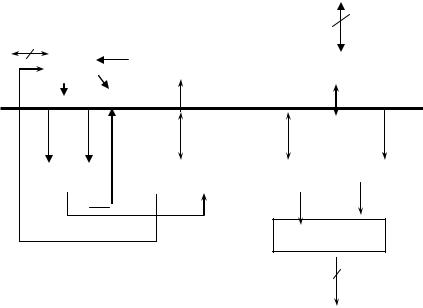

б) Одномагистральное АЛУ

Одномагистральное АЛУ использует два буферных регистра (рис.2.4.). В таком АЛУ сложение выполняется за три такта. В первом такте осуществляется чтение первого операнда из блока Р-ры в БР1, во втором - второго операнда из блока Р-ры в БР2, а в третьем операнды суммируются; результат записывается в один из регистров блока Р-ры.

БР1 |

БР2 |

|

: |

|

|

|

|

|

|

|

|

|

|

|

Р-ры |

|

|

АЛУ |

|

|

|

|

|

||

|

|

|

|

|

|

Рисунок 2.4.- Одномагистральное АЛУ |

|

|

|

|

|

|

|

|

|

||

2.3. Устройство управления (УУ)

2.3.1.Функции УУ. Принцип микропрограммного управления

УУ – важнейшая часть процессора, реализующая функции управления и обеспечивающая работу ЭВМ как единой системы.

Для уяснения функций УУ следует рассматривать ЭВМ как совокупность компонентов, между которыми происходит пересылка информации, и ее обработка. Каждая пересылка происходит в определенный такт времени и инициируется своим сигналом управления (СУ). Тогда управление сводится к выдаче из УУ нужного набора СУ в нужной временной последовательности . Конструктивно УУ выполняется в виде центрального блока, призванного

5

ЭВМ и ПУ. Лекция 2 Щемелева Т.К.

формировать СУ, и отдельных схем, распределенных по всему компьютеру и служащих для использования этих сигналов.

Входной информацией для центрального блока УУ служит код операции (КОП) текущей команды, который определяет конкретную выполняемую операцию. Он поступает в УУ из регистра, хранящего в процессоре текущую команду (РКОМ) и служит для выработки СУ, передаваемых на все устройства и узлы компьютера. Помимо кода операции при работе УУ использует флаги. Они необходимы для реализации ветвлений в алгоритме программы. УУ вырабатывает СУ при поступлении на него тактовых импульсов с ГТИ. Кроме того, УУ получает сигналы из системной шины ЭВМ, например, запросы на прерывание программы, подтверждения приема информации и т.п.

Выходной информацией УУ являются СУ, направляемые в различные устройства ЭВМ, прежде всего в процессор (для приема данных с ШД в регистры, перемещения между регистрами, регистрами и АЛУ) и в системную шину (для передачи СУ в устройства памяти и ввода-вывода). Любое элементарное действие в ЭВМ производится только при поступлении соответствующего СУ из УУ. Возможная частота формирования сигналов на выходе УУ определяется импульсами с ГТИ. Элементарная неделимая пересылка или преобразование информации, выполняемое в течение одного такта под воздействием СУ, называется микрооперацией (МО). СУ, инициирующие МО, можно назвать микрокомандами (МКК). В течение одного такта в разных схемах могут одновременно выполняться несколько независимых МО. Последовательность МКК, реализующая операции или команды, называется микропрограммой (МПР). Например, команда умножения по классическому алгоритму выполняется как МПР циклического типа, состоящая из МО сложения (множимого с частичными произведениями) и поразрядных сдвигов частичных произведений и множителя. Поскольку УУ формируют сигналы для выполнения микроопераций, их часто называют микропрограммными автоматами.

Выделяют 2 класса УУ по способу формирования СУ:

1) УУ с программируемой логикой – [2, Гл.6]. МПР хранится в специальной памяти УУ в виде последовательности кодов – МК. Каждая МК содержит код МО и сведения об адресах операндов этой МО;

2) УУ с «жесткой» (схемной, аппаратной) логикой МПР необходима для построения УУ любого типа.

Список МО для УУ, как правило, невелик. Приведем его ниже.

-пересылка (установка, запись);

-поразрядый сдвиг двоичного кода (вправо или влево);

-поразрядная коньюнкция двоичных кодов;

-поразрядная дизьюнкция двух двоичных кодов

-поразрядная инверсия;

-равнозначность (или ее отрицание);

-алгебраическое сложение дополнительных кодов двоичных чисел.

2.3.2. УУ с «жесткой» логикой.

6

ЭВМ и ПУ. Лекция 2 |

Щемелева Т.К. |

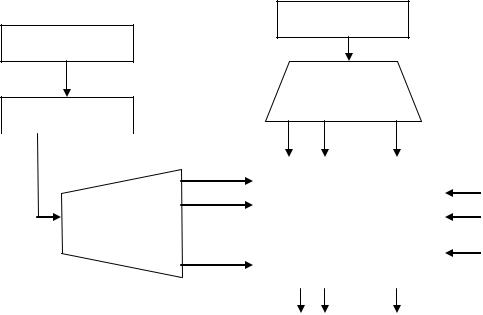

Простейший вариант реализации подобного УУ приведен на рис. 2.5. В

состав УУ входят счетчик тактов, дешифратор тактов, регистр команды (Рком), дешифратор кода операции и логические схемы формирования С. Код операции и номер такта поступают на раздельные дешифраторы и затем на логические схемы формирования СУ. На эти же схемы поступают различные осведомительные сигналы, в т.ч. флаги МО. Сигнал для каждой МО формируются своим собственным набором логических схем, который невозможно изменить, не меняя всѐ УУ, то и обуславливает название – «с жесткой логикой».

Регистр команды с

КОп

Генератор

тактовых

Дешифратор

КОп

Счетчик тактов

|

|

|

1Т |

Умнож |

Слож … Пересылка |

ф |

||

|

|

|

||||||

|

|

|

|

|

|

|

||

|

|

|

|

|

Логические схемы |

|

||

|

Дешифратор |

|

|

|

||||

|

|

|

|

|

л |

|||

|

|

|

формирования сигналов |

|

||||

|

тактов |

2Т |

|

|

||||

|

|

|

а |

|||||

|

|

|

. |

|

|

управления |

|

|

|

|

|

|

|

|

|

||

|

|

|

. |

|

|

|

г |

|

|

|

|

|

|

|

|

||

|

|

|

.nТ |

|

|

|

|

и |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Сигналы управления

Рисунок 2.5.- Структура УУ с «жесткой» логикой

КОП как поле команды, хранящейся в Регистре команды, используется для определения того, какие СУ и в какой последовательности должны формироваться. Для каждой операции дешифратор КОП формирует отдельный СУ. ГТИ, как уже говорилось, формирует тактовые импульсы, к которым «привязаны» СУ, в строго определенные моменты времени. Содержимое счетчика тактов увеличивается на 1 после завершения очередного такта. К выходам счетчика подключен дешифратор тактов, который расшифровывает двоичный код в счетчике и выставляет сигнал на соответствующем такту выходе.

МПР представляют в виде схемы (блок-схемы) алгоритмов. Пример схемы алгоритма МПР операции сложения дан на рис. 2.7.В операторный i-блок вписывают выполняемую в течение одного такта МО. СУ, инициирующий эту МО, обозначается Yi. С операторным блоком связаны один вход и один выход. В каждой условной вершине Хj записывается один из элементов множества логических условий как правило, флагов МО.

Курсовая работа по этой дисциплине состоит в разработке схемы (блоксхемы) алгоритма МПР.

2.4. Структурная организация процессора.

7

ЭВМ и ПУ. Лекция 2 |

Щемелева Т.К. |

|

Рассмотрим структуру процессора на простейшем примере 8-разрядного |

||

МП с |

одномагистральным АЛУ. |

Схема приведена на рис. 2.6. МП, |

используемые в ПЭВМ IBM PC, даже |

в первых моделях, значительно сложнее, |

|

однако, |

наряду с другими все названные блоки и узлы присутствуют и в них, |

|

только в более сложной логической и схемотехнической реализации. Простейший МП с одной внутренней шиной и внешними шинами ША, ШД,

ШУ состоит из следующих уже известных и новых блоков:

УУ и АЛУ.

РОН - регистры общего назначения - для временного хранения операндов и результатов выполненных операций.

Управляющие регистры

- |

Регистр команды - |

для хранения |

текущей |

команды; |

- |

Счетчик команд (программный счетчик) - для хранения и модификации |

|||

|

адреса текущей |

команды; |

|

|

-Регистр флагов - для хранения флагов;

-Регистр адреса - для хранения адреса устройства, к которому обращается МП.

-БФД - буфер данных, вспомогательная схема, обеспечивающая выбор направления и моменты передачи по ШД, определяемые СУ из УУ

|

|

|

|

|

|

Д |

|

У |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

УУ |

|

Регистр команд |

|

БФД |

|

|

|

|

(РГкоманд) |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

АЛУ |

|

Регистр |

|

РОН |

|

|

||

Счетчик команд |

||||||||

|

|

|

флагов |

|

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Регистр адреса

(РА)

А

.

Рисунок.2.6. - Структура 8-разрядного МП

8

ЭВМ и ПУ. Лекция 2 |

Щемелева Т.К. |

2.5.Стадии (этапы) выполнения команды

Для уяснения принципов работы МП рассмотрим пример выполнения команды сложения. Пусть одно слагаемое хранится в ячейке памяти (ОЗУ), а второе – в регистре МП. Тогда команда на языке ассемблер может иметь следующий формат:

Сложение |

[166] |

АХ |

(КОП) |

(адрес ячейки памяти) |

(имя регистра процессора) |

|

|

|

Упрощенно выполнение этой команды в МП, схема которого представлена на рис. 2.6., можно описать следующими этапами:

выборка (или чтение) очередной команды в регистр команды из ячейки памяти с адресом, указанным в счетчике команд;

декодирование кода операции с помощью дешифратора в УУ;

чтение первого операнда из ячейки ОЗУ с адресом 166 на АЛУ;

чтение второго операнда из регистра МП с именем АХ на АЛУ.

исполнение операции в сумматоре АЛУ;

сохранение результата в ячейке ОЗУ с адресом 166 (по умолчанию - по первому адресу в команде).

По завершению команды УУ выдает СУ на автоматическое изменение содержимого счетчика команд для обращения процессора к ОЗУ за следующей командой. Для линейного участка программы содержание счетчика команд после каждой команды увеличивается на число ячеек, хранящих предыдущую команду.

По сигналу с УУ этот адрес выставляется на ША и все повторяется для новой команды.

Обратим внимание, что на тех стадиях, когда требуется обращение МП к другим устройствам, внешним по отношению к МП (например, к памяти), в работе участвуют ША, ШД, ШУ.

Для МП с одной внутренней магистралью упрощенная схема алгоритма команды сложения в виде блочной структуры представлена на рис.2.7. Напомним (см. лекц. 2), что операнды, например, в ПЭВМ IBM PC, в регистрах и в ячейках памяти хранятся в дополнительном коде, т.е.готовы к поразрядному суммированию. Поскольку каждый из блоков состоит из элементарного действия, т.е. МО, эта схема есть схема алгоритма МПР команды сложения.

Как следует по рис. 2.7. выполнение команды по самой короткой ветви займет 7 тактов.

Список рекомендуемой литературы.

1.Максимов Н. В., Партыка Т. Л., Попов И. И. Архитектура ЭВМ и вычислительных систем. – М.: Форум: Инфра-М, 2005. – 512 с.

2.Цилькер Б. Я., Орлов С. А. Организация ЭВМ и систем. – СПб.: -

Питер, 2004. – 668с.

9

ЭВМ и ПУ. Лекция 2 |

Щемелева Т.К. |

Начало

Адрес текущей команды из СК -> ША;

Y1

СУ «Читать» -> ШУ; В РГ команд из сегмента кода ОЗУ по

ШД передается команда

Y2 Дешифратор УУ расшифровывает КОп

Да |

Оп1 в регистре |

Нет |

X3 |

|

|

МП ? |

|

|

|

|

Да |

Нет |

Оп1 в регистре |

|

X4 |

AX ? |

|

Да |

Операция |

Нет |

X1 |

сложения ? |

|

Нет |

Да |

Оп1 в ОЗУ ?

X2

Y4 166 -> РА

РА -> ША;

Y5 СУ «Читать» -> ОЗУ; Оп1 из ШД -> Вх1 АЛУ

Y3 Оп1 из AX -> Вх1 АЛУ

Нет |

Оп2 в Регистре |

Да |

|

|

|

|

|

|

X5 |

AX ? |

|

|

|

Y6 Оп2 из AX -> Вх2 АЛУ

Y7

Исполнение операции в сумматоре АЛУ

Результат из АЛУ -> ШД; Y8 СУ «Запись» -> ШУ;

166 -> ША;

Y9 Увеличение счетчика команд на 1

Конец

Рисунок 2.7. - Микропрограмма выполнения команды сложения.

Контрольные вопросы и задания:

1)Что общего между двоичным регистром и двоичным счетчиком.

2)Сколько выходов имеет дешифратор с двумя,… десятью входами?

3)Сколько флагов может хранить 8-ми битовый регистр.

10