- •В. Ф. Нестерук Организация эвм и систем

- •Удк 004.2 (075)

- •Редактор н. Н. Пацула

- •История развития электронных цифровых вычислительных машин

- •Организация операционных устройств

- •Организация операционной части

- •Пример структурной организации оч для выполнения логических операций

- •Пример реализации оч для суммирования чисел с фиксированной запятой в прямых кодах

- •Выходных шинах, применяемых в схеме устройства элементов и узлов, либодля выработки лу в схему могут вводиться специальные элементы и узлы.

- •Микрооперации Логические условия

- •Организация интегральной операционной части

- •Примеры реализации операций в интегральной оч

- •Аппаратное наращивание интегральной оч

- •Организация управляющей части

- •Типовая структура управляющей части

- •Пример структурной реализации бму серии к584 ву1

- •Основные режимы адресации бму

- •Интерфейсные средства микроЭвм

- •Организация системы синхронизации

- •Пример интегрального контроллера синхронизации к583вг1

- •Организация микроЭвм с микропрограммным управлением

- •Типовые циклы функционирования микроЭвм

- •Организация командного управления

- •Форматы и адресность команд

- •Адресации в командном цикле

- •Библиографический список

- •Содержание

Пример реализации оч для суммирования чисел с фиксированной запятой в прямых кодах

Структурная схема алгоритма операции суммирования приведена на рис.9. В ней содержатся как операторные, так и условные вершины. Следовательно, в ОЧ кроме основного результата должны будут формироваться и сигналы логических условий. В качестве ЛУ могут быть использованы значения конкретных битов на входных и

Выходных шинах, применяемых в схеме устройства элементов и узлов, либодля выработки лу в схему могут вводиться специальные элементы и узлы.

Д ля

перехода к построению структурной схемы

ОЧ необходимо определить перечень

используемых элементов и узлов.

Основываясь на практическом опыте,

сделаем следующий выбор. В качестве

узлов фиксации операндов и результата

будем применять регистры, как это

делалось в ранее рассмотренном примере.

Суммирование и вычитание кодов будем

осуществлять в универсальном

ля

перехода к построению структурной схемы

ОЧ необходимо определить перечень

используемых элементов и узлов.

Основываясь на практическом опыте,

сделаем следующий выбор. В качестве

узлов фиксации операндов и результата

будем применять регистры, как это

делалось в ранее рассмотренном примере.

Суммирование и вычитание кодов будем

осуществлять в универсальном

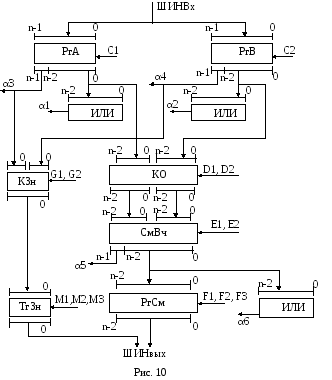

сумматоре-вычитателе, а прямое или перекрестное подключение операндов ко входам сумматора-вычитателя – с помощью коммутатора операндов. Так как знак результата формируется отдельно, то для его выработки и хранения будем использовать коммутатор знаков и триггер знака. Для анализа кодов на равенство нулю задействуем сборки логических элементов «ИЛИ».

Возможный вариант структурной схемы устройства приведён на рис. 10, где используются следующие обозначения: ШИНВх и ШИНВых – n-разрядные входная и выходная шины данных; РгА, РгВ и РгСм – входные регистры операндов А и В и регистр модуля результата; КО и КЗн – коммутаторы операндов и знаков; ТгЗн – триггер знака результата; СмВч – сумматор-вычитатель; ИЛИ – логические сборки ИЛИ. Расшифровка сигналов управления микрооперациями и сигналов логических условий дана соответственно в табл. 2 и 3.

Таблица 2 Таблица 3

Микрооперации Логические условия

|

Логические условия |

Примечание |

|

1 |

=0, если А=0 =1, если А0 |

|

2 |

=0, если В=0 =1, если В0 |

|

3 |

=0, если А≥0 =1, если А0 |

|

4 |

=0, если В≥0 =1, если В0 |

|

5 |

=0, если ()≥0 =1, если иначе |

|

6 |

=0, если ()=0 =1, если иначе |

|

Микро–операции |

Примечание |

|

C1, C2, F1, M1 |

Приём в Рг |

|

D1 |

Прямая передача |

|

D2 |

Перекрёстная передача |

|

E1 |

Суммирование |

|

E2 |

Вычитание |

|

G1 |

Передача знака операнда А |

|

G2 |

Передача знака операнда В |

|

M2, F2 |

Выдача результата |

|

F3, M3 |

Сброс РгСм и ТгЗн |

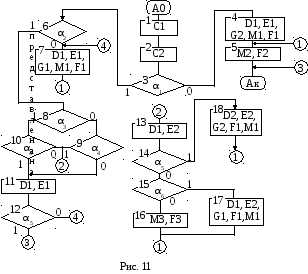

ГСА микропрограммы в соответствующих символических обозначениях МО и ЛУ показана на рис. 11.

Структурная схема операционной части может быть реализована в нескольких вариантах, что зависит от налагаемых условий по быстродействию, использованию элементной базы, стоимости реализации и прочего. В рассматриваемом примере используется одноформатная шина ввода, что приводит к последовательному вводу данных в вершинах С1 (вершина 1) и С2 (вершина 2). Сравнение знаков в примере выполняется программно, сначала знак А (вершина 8), потом знак В (9 или 10 вершины).

Если бы в схему был введён сумматор по модулю 2 (рис. 12), то сравнение знаков производилось бы за один такт, а не за два такта. Если один из операндов равен нулю, то в примере выполняется холостое суммирование со вторым операндом (4 или 7 вершины). Чтобы ускорить этот процесс, можно было бы ввести средство передачи операнда сразу в выходной регистр (с помощью дополнительных коммутаторов).

В результате неоднозначности структурной реализации ОЧ будет наблюдаться и неоднозначное отображение исходного алгоритма в микропрограмму.