- •2)Электронно-дырочный p-n переход и его основные свойства.

- •3)Полупроводниковыерезисторы:варисторы,термо- Тензорезисторы Назначение. Характеристики, основные параметры.

- •4. Полупроводниковые диоды.

- •5 Биполярные транзисторы. Устройство, принцип действия.

- •6. Схемы включения, характеристики и режим работы биполярных транзисторов.

- •7. Полевые транзисторы. Устройство, принцип действия, характеристики, основные параметры.

- •8. Тиристоры: динистры, тринистры. Устройство, вах, основные параметры.

- •9. Оптоэлектронные приборы: фоторезисторы, свето-, фотодиоды, фототранзисторы, фототиристоры, оптроны. Назначение, характеристики, основные параметры.

- •10. Маркировка и обозначение полупроводниковых приборов и интегральных микросхем.

- •11. Источники вторичного электропитания

- •12 Выпрямители. Схемы выпрямления, их расчет

- •13.Стабилизаторы напряжения и тока: параметрические и компенсационные,их параметры и характеристики.

- •14.Управляемые выпрямители

- •15.Основные параметры и характеристики усилителей.Обратныесвязи,их влияние на работу усилителя.

- •16.Однокаскадный усилитель на биполярном транзисторе с общим эмиттером: принцип действия

- •17.Многокаскадный усилитель

- •18.Операционный усилитель: назначение, устройство, характеристики, типы.

- •23 Компатор и мультивибраторр

- •24. Генераторы гармонических колебаний генераторы

- •22. Ключевой режим работы транзистора.

- •31. Цифровые счётчики. Схемная реализация. Типовые имс.

- •32. Регистры памяти и регистры сдвига. Схемная реализация. Типовые имс.

- •40. Аналогово-цифровые преобразователи.

- •Ацп последовательного счёта.

- •Ацп последовательного приближения.

- •Ацп параллельного типа.

- •Цифро-аналоговые преобразователи.

22. Ключевой режим работы транзистора.

В этом режиме рабочая точка может находиться только в двух возможных положениях: либо в зоне отсечки (транзистор заперт и его можно рассматривать как разомкнутый ключ), либо в зоне насыщения (транзистор полностью открыт и его можно рассматривать как замкнутый ключ). В активной зоне рабочая точка находится только в течение короткого промежутка времени, необходимого для перехода её из одной зоны в другую. Поэтому при работе в ключевом режиме линия нагрузки может на среднем своем участке выходить за пределы гиперболы допустимых мощностей, при условии, что переход транзистора из закрытого состояния в открытое и наоборот производится достаточно быстро (рис. 3.38).

Как

уже было показано выше, транзистор в

режиме отсечки можно представить в виде

разомкнутого ключа, так как практически

все напряжение источника питания падает

между его эмиттером и коллектором, а

ток коллектора

близок к нулю. Входное напряжение

близок к нулю. Входное напряжение приложено к эмиттерному переходу

транзистора в запирающем направлении

(рис. 3.39).

приложено к эмиттерному переходу

транзистора в запирающем направлении

(рис. 3.39).

В

режиме насыщения во входной цепи

транзистора протекает достаточно

большой ток базы, при котором ток

коллектора достигает максимального

значения

, близкого к

, близкого к –максимально

возможному току в цепи источника питания.

При этом напряжение

–максимально

возможному току в цепи источника питания.

При этом напряжение транзистора имеет минимальное значение

, близкое к нулю, что позволяет представить

транзистор в виде замкнутого ключа.

Отсюда и название этого режима работы

– ключевой. В режиме насыщения напряжение

на коллекторном переходе

транзистора имеет минимальное значение

, близкое к нулю, что позволяет представить

транзистор в виде замкнутого ключа.

Отсюда и название этого режима работы

– ключевой. В режиме насыщения напряжение

на коллекторном переходе может быть определено:

может быть определено:

+

+ (3.54)В

обычном режиме напряжение

(3.54)В

обычном режиме напряжение смещает

коллекторный переход в обратном

направлении, т. е.

смещает

коллекторный переход в обратном

направлении, т. е. <

0

<

0

Ток

коллектора

,β-коэффициент

передачи по току, может достичь величины,

при которой

,β-коэффициент

передачи по току, может достичь величины,

при которой (критерием насыщения транзистора ).

(критерием насыщения транзистора ).

Минимальное значение базового тока, при котором выполняется условие, называется током насыщения .Чем больше базовый ток значения , тем глубже насыщение транзистора, тем больше заряд инжектированных из эмиттера носителей накапливается в базе. Относительное значение этого превышения называется степенью насыщения транзистора N.

25 К элементам булевой алгебры относят:1)const-логические 0 и 1;2)переменные-х1,х2,х3..;3)функции у=f(x1,x2,x3..)

Логические элементы. Элемент И - это логическая схема, на выходе которой 1 появляется только тогда, когда на все его входы поступает сигнал 1. Если на какой-либо из входов

поступает

О, на выходе появляется О.

На рис. 12.46 показаны стандартные обозначения, используемые для элементов И. Элемент И может иметь любое количество входов, большее одного.

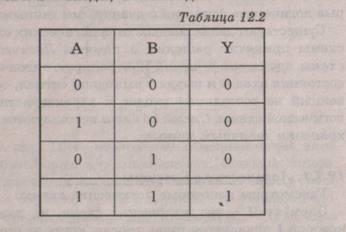

Состояние

и логическую связь между входными и

выходными сигналами элемента И отражает

так называемая таблица истинности

(табл. 12.2), которая показывает выходное

состояние двухвходово-го элемента для

любых возможных состояний входов: А и

В - входы; У - выход.

Элемент И выполняет операцию логического умножения. Логическое умножение известно как функция И.

Элемент

ИЛИ - это логическая схема, на выходе

которой появляется 1, если на любой из

его входов подана 1. На его выходе

появляется О, если на все его входы

поданы О. Этот элемент, как и элемент И.

может иметь два или более входов. На

рис. 12.47 показаны стандартные обозначения,

используемые для элементов ИЛИ с двумя,

тремя и четырьмя входами.Значения на

выходе элемента ИЛИ с двумя входами

приведены в таблице истинности (табл.

12.3):

А и В - входы; Y – выход

Элемент ИЛИ выполняет логическую операцию сложения.

Элемент

НЕ выполняет функцию, которая называется

инверсией, или дополнением, и обычно

называется инвертором. Цель инвертора

- сделать состояние выхода противоположным

состоянию входа. В логических цепях

возможны два состояния 1 и О. Состояние

1 также называют высоким, чтобы указать,

что напряжение в этом состоянии выше,

чем в состоянии 0.

Схематическое обозначение инвертора показано на рис. 12.48.

Работу инвертора отражает таблица истинности (табл. 12.4). Вход инвертора обозначен А, а выход А (читается «не А»), Черточка над буквой А показывает отрицание А. Поскольку инвертор имеет только один вход, то возможны только два состояния входа.

Элемент И-НЕ является комбинацией элементов И и НЕ. Элемент И-НЕ является наиболее широко используемой логической функцией. Это обусловлено тем. что эти элементы могут быть использованы для создания некоторых других логических элементов.

Схематическое

обозначение элемента И-НЕ показано на

рис. 12.49. Ни рисунке также показана его

эквивалентность последователю включенным

элементу И и инвертору. Кружочек ни

выходе обозначает инвертирование

функции И.

Ниже приведена таблица истинности для двухвходового элемента И-НЕ (табл. 12.5). Заметим, что выход элемента И-НЕ является отрицанием выхода элемента И. Подача О на любой вход дает на выходе1.

Элемент ИЛИ-НЕ является комбинацией элемента ИЛИ и инвертора. Подобно элементу И-НЕ, элемент ИЛИ НЕ также может быть использован для создания других логических элементов. Схематическое обозначение элемента ИЛИ-НЕ показало на рис. 12.50. На рисунке также показана его эквивалентность последовательно включенным элементу ИЛИ и инвертору. Кружочек но выходе показывает инвертирование функции ИЛИ.

Таблица 12.6 - таблица истинности для двухвходового элемента ИЛИ-НЕ. Заметим, что его выход является отрицанием выхода элемента ИЛИ. 1 на выходе появляется только тогда, когда на оба входа поданы О- Если на любой из входов подана 1, то на выходе будет О. Существуют элементы ИЛИ-НЕ с двумя, тремя, четырьмя и восемью входами.

ТТЛ логика

В ТТЛ операцию «И» выполняет многоэмиттерный транзистор. Если хотя бы на один из входов будет подаваться сигнал логического нуля, соответствующий эмиттерный переход транзистора VT1 будет открыт, и через него будет протекать ток от плюса источника питания (ИП), через резистор R1, база-эмиттер VT1, общий провод, минус источника питания. В цепи коллектора VT1, а следовательно, и в цепи базы VT2, ток будет отсутствовать, транзистор VT2 будет находиться в режиме отсечки, на выходе будет высокий уровень напряжения логической единицы. При подаче на оба входа логических единиц оба эмиттерных перехода закрываются, и ток будет протекать по цепи от плюса ИП, через R1, база-

коллектор VT1 и на базу VT2. Транзистор VT2 перейдёт в режим насыщения и на выходе установится низкий уровень напряжения логического нуля.

26 Шифратор — это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду. Число входов и выходов в полном шифраторе связано соотношением п = 2т, где п — число входов, т — число выходов. Основное назначение шифратора — преобразование номера источника сигнала в код (например, номера нажатой кнопки некоторой клавиатуры).

Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Число входов и выходов в так называемом полном дешифраторе связано соотношением т = 2n, где п — число входов, а т — число выходов. Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным.

Дешифратор — одно из широко используемых логических устройств. Его применяют для построения различных комбинационных устройств.

Так,

микросхема КР531ИД14 представляет собой

два дешифратора 2 х 4, т. е. каждый дешифратор

имеет два информационных входа и четыре

инверсных выхода, а также инверсный

вход разрешения.

Цифры на входе (1,2) обозначают вес разряда двоичного числа, а цифры на выходе (0—3) определяют десятичное число, соответствующее заданному числу на входе.

При логической 1 на входе разрешения на всех выходах будут также логические 1. При активизации входа разрешения, т. е. при Е = 0, логический 0 появляется на том выходе дешифратора, номер которого соответствует десятичному эквиваленту двоичного числа, поданного на информационные входы. Благодаря наличию входа разрешения можно наращивать размерность дешифраторов.

27. Мультиплексором называют комбинационное устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход. Мультиплексоры обозначают через MUX (от англ. multiplexor), а также через MS (от англ. multiplexor selector). Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Кроме информационных входов в мультиплексоре имеются адресные входы и, как правило, разрешающие (стробирующие). Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных входов n и числом адресных входов m действует соотношение n = 2m, то такой мультиплексор называют полным. Если n < 2m, то мультиплексор называют неполным.

Демультиплексором называют устройство, в котором сигналы с одного информационного входа поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры обозначают через DMX или DMS.

Если

соотношение между числом выходов n

и числом адресных входов m

определяется равенством n

= 2m,

то такой демультиплексор называется

полным, при n

< 2m

демультиплексор является неполным.

Мультиплексор-демультиплексор К561КП1

Cодержит два четырехвходовых мультиплексора

4 → 1, которые могут использоваться

и как демультиплексоры.

28.Различают полные сумматоры и полусумматоры. Полный сумматор предназначен для сложения трех одноразрядных чисел A, B и C, где в качестве числа C выступает перенос из предыдущего разряда P. В результате выполнения операции сложения в каждом разряде, кроме суммы, может возникнуть перенос в старший разряд P. Для построения схемы сумматора составим таблицу истинности .

Таблица истинности полного сумматора

По таблице составим логические выражения СДНФ, описывающие работу полного сумматора:

Полученные выражения приводят к достаточно сложной схемной реализации полного сумматора в базисах И-НЕ или ИЛИ-НЕ. Поэтому полный сумматор обычно строится из двух полусумматоров.

Полусумматор при выполнении операции сложения не учитывает переноса из предыдущего разряда. Работу полусумматора можно описать:

Таблица истинности полусумматора

Из таблицы следует:

Реализация полусумматора показана на рис. 2.2,а. На рис. 2.2,б показано его условное обозначение.

Полный сумматор строится из двух полусумматоров по схеме приведенной на рис. 2.3,а. Условное обозначение полного сумматора показано на рис. 2. 3,б.

Рис. 2. 3. Схема полного сумматора и его условное обозначение

Для сложения n - разрядных чисел требуется один полусумматор в младшем разряде и n- 1 полных сумматоров (рис. 2. 4).

Сумматоры с различной разрядностью выпускаются в виде ЦИС.

Например: 155ИМ1 – одноразрядный сумматор; 155ИМ2 – двухразрядный

сумматор; 155ИМ3 – четырехразрядный сумматор.

29.Триггером называется устройство с двумя устойчивыми состояниями. Триггеры представляют собой простейшие последовательностные устройства и широко используются в электронных устройствах различного назначения как в виде самостоятельных узлов, так и в качестве элементов для построения более сложных цифровых устройств (счетчиков, регистров, запоминающих устройств). К триггерам относят большой класс устройств, отличительной особенностью которых является способность оставаться в одном из двух устойчивых состояний, которые могут изменяться под действием внешних сигналов. При этом состояния триггера распознаются по уровням выходных напряжений, соответствующих уровням “0” и “1”.

Основным свойством триггера является наличие памяти, под которой подразумевается его способность сохранять свое состояние (“0” или “1”) и после прекращения воздействия внешних сигналов. Таким образом, триггер является элементарной ячейкой памяти для хранения одного двоичного разряда числа.

Обобщенная схема триггерного устройства показана на рис. 3.1 и состоит из устройства управления УУ и триггерной ячейки ТЯ.

Существует множество разновидностей триггеров, отличающихся выполняемыми функциями, способами управления записью информации, схемотехническими решениями и т.д. По выполняемым функциям классификацию триггеров производят по состоянию его выходов в момент его срабатывания и после. При этом различают следующие основные виды: RS, JK, T и D - триггеры. По способу управления записью информации различают:

• асинхронные триггеры с записью непосредственно с поступлением информационного сигнала на его вход;

• тактируемые (синхронные) триггеры с записью информации только при подаче тактирующего импульса.

При этом срабатывание триггера может происходить одновременно с поступлением тактирующего импульса (триггер, работающий по уровню), после окончания тактирующего

импульса (триггер с внутренней задержкой), прохождения нескольких тактирующих импульсов (многотактные триггеры), или в моменты изменения состояния тактирующего импульса (синхронизация по фронту).

RS – триггеры

RS–триггер имеет два управляющих входа S (set) и R (reset), с помощью которых выполняются установки триггера в то или иное состояние (рис. 3. 2,а):

Q = 1 при S=1 и R=0 ( установка триггера);

Q = 0 при S=0 и R=1 (сброс триггера);

Qn+1=Qnпри S=R=0 (режим хранения предыдущего состояния);

S=R=1 – запрещенная комбинация управляющих сигналов, которая

может привести к неопределенному состоянию триггера.

Учитывая связь текущего состояния триггера Qn+1 с предыдущим состоянием Qn при различных комбинациях управляющих сигналов S и R, из табл. 3. 1 можно сформировать сокращенную таблицу истинности (табл. 3. 2). Рассматриваемый триггер является асинхронным, т.к. изменение его состояния происходит непосредственно с поступлением управляющих сигналов. Принцип работы асинхронного RS-триггера поясняется временными диаграммами, показанными на рис. 3. 3.

Схемотехнически RS-триггер может быть реализован на элементах 2ИЛИ-НЕ (рис. 3. 2,б) и 2И-НЕ (рис. 3.2,в) с использованием перекрестных положительных обратных связей. В триггере на элементах 2И-НЕ изменение состояния происходит при низких уровнях сигналов S и R . В синхронных RS-триггерах могут быть использованы различные способы синхронизации. На рис. 3. 4,а и б показаны схемотехническая реализация и условное обозначение RS-триггера с синхронизацией по уровню (высокому). На рис. 3. 4,в приведены диаграммы работы такого триггера. Изменение состояний происходит только при высоких уровнях сигнала синхронизации С.

В RS-триггере с синхронизацией по фронту изменение состояния происходит в момент изменения уровня сигнала С. При этом возможна синхронизация как по переднему, так и по заднему фронту (срезу). Такие триггеры строятся по двухступенчатой схеме и в них процессы приема и записи данных разделены во времени. Схема триггера с синхронизацией по заднему фронту и его условное обозначение приведены на рис. 3. 5.

30.JK-триггеры

JK-триггер имеет два управляющих входа J (jump) и K (keep) и функционирует подобно RS-триггеру, но при этом не имеет запрещенных комбинаций управляющих сигналов. J - вход подобен S – входу, а K-вход подобен R-входу. При всех комбинациях сигналов на входе, кроме J=K=1, он действует подобно RS-триггеру. При J=K=1 в каждом такте происходит «опрокидывание» триггера и его состояние меняется на противоположное (табл. 3. 3). На рис. 3. 6 показано условное обозначение JK-триггера c синхронизацией по переднему фронту.

JK-триггеры относятся к универсальным устройствам в отношении их применения как для построения других типов триггеров, так и более сложных устройств последовательного принципа действия. Во всех сериях ИС выпускаются JK-триггеры с различными функциональными возможностями. Например, ИС 155ТВ1 (рис. 3. 8) имеет по три входа J и K, связанных логической операцией И, что существенно расширяет возможности ее применения при реализации различных алгоритмов управления состояниями триггера без применения дополнительных элементов.

Т-триггеры

Т-триггеры иначе называются счетными и применяются для построения счетчиков и делителей частоты. Такой триггер имеет один тактовый вход и его состояние меняется каждый раз при подаче счетного импульса Т=1 и остается неизменным при Т=0. Таблица состояния триггера приведена в табл. 3. 4. Обозначение Т-триггера и диаграммы работы приведены на рис. 3. 9.

D –триггеры

Отличительной особенностью D-триггера (триггера задержки) является то, что он сохраняет информацию, поступившую на D-вход в предыдущем такте работы до прихода синхроимпульса, т.е. его состояние может изменяться с задержкой на один такт. Синхронизация работы производится по переднему или заднему фронту. Условное обозначение D-триггера с синхронизацией по переднему фронту и диаграммы его работы показаны на рис. 3. 11.