- •Разработайте дешифратор выбора регистра вывода 32-х дискретных сигналов.

- •Разработайте дешифратор выбора регистра вывода 17-и дискретных сигналов.

- •Разработайте схему мультиплексирования 32-х дискретных сигналов для модуля ввода мпсу.

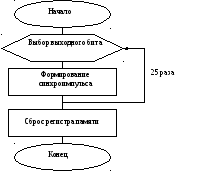

- •Разработайте схему мультиплексирования 25-и дискретных сигналов для модуля ввода мпсу.

- •Разработайте электронный ключ для вывода дискретных управляющих сигналов постоянного тока.

- •Оптопара аот110а.

- •Разработайте электронный ключ для вывода дискретных управляющих сигналов переменного тока.

- •Реализуйте аппаратно схему подсчета внешних событий.

- •Реализуйте программно-аппаратно схему подсчета внешних событий.

- •1. Выбор режима таймера счетчика:

- •Разработайте функциональную схему устройства ввода аналоговой информации. Используйте схему выборки-хранения для устранения динамической ошибки.

- •Разработайте функциональную схему устройства вывода аналоговой информации. Используйте цап с матрицей r-2r.

- •Организуйте опрос, нормализацию, фильтрацию и коррекцию динамической ошибки (схему выборки-хранения) 8-ми полупроводниковых датчиков температуры.

- •Организуйте стабилизацию сигнала, нормализацию, гальваническую развязку и опрос 32-х индуктивных датчиков положения.

-

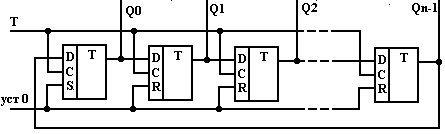

Реализуйте аппаратно схему подсчета внешних событий.

Счетчиком называют устройство, предназначенное для подсчёта числа импульсов поданных на вход. Они, как и сдвигающие регистры, состоят из цепочки триггеров. Разрядность счетчика, а следовательно, и число триггеров определяется максимальным числом, до которого он считает.

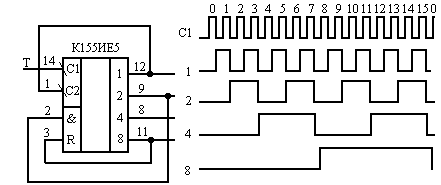

Для счетчика с К=10 нужны четыре триггера (так как 23<10<24) должен иметь десять устойчивых состояний N==0,1...,8,9. В том такте, когда он должен был перейти в одиннадцатое устойчивое состояние (N=10), его необходимо сбросить в исходное нулевое состояние. Для такого счётчика можно использовать микросхему К155ИЕ5 рисунок 3, введя цепи обратной связи с выходов счетчика, соответствующих числу 10 (т. е. 2 и 8) на входы установки счетчика в 0 (вход R). В самом начале 11-го состояния (число 10) на обоих входах элемента И микросхемы появляются логические 1, вырабатывающие сигнал сброс всех триггеров счетчика в нулевое состояние.

Счетчик потребляет ток 15 мА, по входу С0 максимальная частота до 10 МГц и по входу С1 до 32МГц.

-

Реализуйте программно-аппаратно схему подсчета внешних событий.

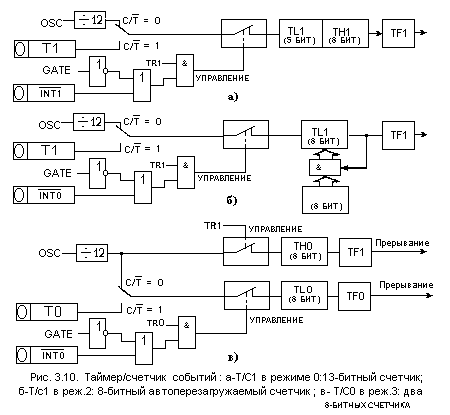

1. Выбор режима таймера счетчика:

Режим

0.

Перевод любого Т/С в режим 0 делает его

похожим на таймер МК48 (8-битный счетчик),

на вход которого подключен 5-битный

предделитель частоты на 32. Работу Т/C в

режиме 0 на примере Т/C1 иллюстрирует

рис.

13, а. В этом режиме таймерный регистр

имеет разрядность 13 бит. При переходе

из состояния "все единицы" в

состояние "все нули" устанавливается

флаг прерывания от таймера TF1. Входной

синхросигнал таймера 1 разрешен (поступает

на вход T/C), когда управляющий бит TR1

установлен в 1 и либо управляющий бит

GATE (блокировка) равен 0, либо на внешний

вывод запроса прерывания

![]() поступает уровень 1.

поступает уровень 1.

Отметим попутно, что установка бита GATE в 1 позволяет использовать таймер для измерения длительности импульсного сигнала, подаваемого на вход запроса прерывания.

Р

Рис.

13. Таймер/счетчик событий: а - T/C1 в режиме

0: 13-битный счетчик; б - Т/С1 в режиме 2:

8-битный автоперезагружаемый счетчик;

в - Т/С0 в режиме 3: два 8-битный счетчика.

Режим 2. В режиме 2 работа организована таким образом, что переполнение (переход из состояния "все единицы" в состояние "все нули") 8-битного счетчика TL1 приводит не только к установке флага TF1 (рис. 13, б), но и автоматически перезагружает в TL1 содержимое старшего байта (TH1) таймерного регистра, которое предварительно было задано программным путем. Перезагрузка оставляет содержимое ТН1 неизменным. В режиме 2 Т/С0 и Т/С1 работают совершенно одинаково.

Режим 3. В режиме 3 Т/C0 и Т/C1 работают по-разному. Т/C1 сохраняет неизменным свое текущее содержимое. Иными словами, эффект такой же, как и при сбросе управляющего бита TRI в нуль.

Работу

T/C0 в режиме 3 иллюстрирует рис.

13, в. В режиме 3 TL0 и ТН0 функционируют

как два независимых 8-битных счетчика.

Работу TL0 определяют управляющие биты

T/C0 (![]() ,

GATE, TR0), входной сигнал

,

GATE, TR0), входной сигнал

![]() и флаг переполнения TF0, Работу TH0, который

может выполнять только функции таймера

(подсчет машинных циклов МК), определяет

управляющий бит TR1. При этом ТН0 использует

флаг переполнения TF1.

и флаг переполнения TF0, Работу TH0, который

может выполнять только функции таймера

(подсчет машинных циклов МК), определяет

управляющий бит TR1. При этом ТН0 использует

флаг переполнения TF1.

Режим 3 используется в тех случаях применения МК51, когда требуется наличие дополнительного 8-битного таймера или счетчика событий. Можно считать, что в режиме 3 МК51 имеет в своем составе три таймера/счетчика. В том случае, если Т/С0 используется в режиме 3, Т/С1 может быть или включен, или выключен, или переведен в свой собственный режим 3, или может быть использован последовательным портом в качестве генератора частоты передачи, или, наконец, может быть использован в любом применении, не требующем прерывания.

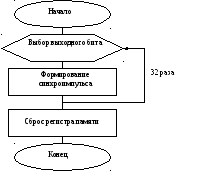

2. Алгоритм: (запуск……………счет)

-

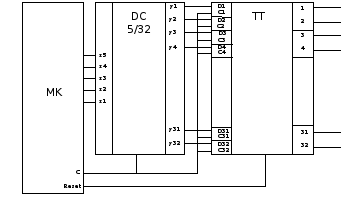

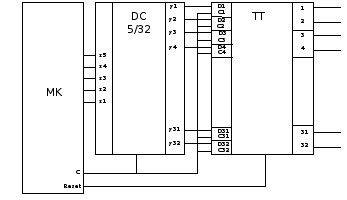

Разработайте схему хранения 32-х выходных сигналов цифрового канала вывода МПСУ, принимая нагрузочную способность шины данных не более двух ТТЛ – нагрузок. Разработайте фрагмент программы вывода данных.

-

Разработайте схему хранения 25-х выходных сигналов цифрового канала вывода МПСУ, принимая нагрузочную способность шины данных не более двух ТТЛ – нагрузок. Разработайте фрагмент программы вывода данных.