Московский Технический Университет Связи и Информатики

Кафедра Электроники и микроэлектронных средств телекоммуникации

ОТЧЁТЫ(K)

По лабораторным работам по курсу

«Электроника в технике почтовой связи»

Лабораторный цикл: «Моделирование запоминающих элементов на

интегральных микросхемах»

Студент гр. УИ0301

Востропятов Н. А.

Лабораторная работа №1 ___________допуск___________приём Лабораторная работа №2 ___________допуск___________приём Лабораторная работа №3 ___________допуск___________приём Лабораторная работа №4 ___________допуск___________приём

Методические указания при выполнении лабораторных работ по циклу «Моделирование запоминающих элементов на интегральных микросхемах».

Для хранения двоичной информации, организации вычислительных и логических операций, синхронизации работы систем управления применяются триггеры. Триггер - это устройство с двумя устойчивыми состояниями, способное хранить одну двоичную единицу информации - бит. Он является основным элементом электронных устройств с памятью. Триггер в интегральном исполнении состоит из запоминающего элемента (собственно триггера) и схемы управления, которая преобразует входные сигналы в сигналы, оказывающие непосредственное воздействие на триггер. В сериях интегральных микросхем имеются разнообразные модификации триггеров. Наиболее часто применяются следующие типы триггеров [1,2,3]:

-

асинхронные RS-триггеры;

-

синхронные RS-триггеры;

-

D триггеры;

-

JK-универсальные триггеры.

Триггеры имеют различные виды входов:

R (от английского RESET) — раздельный вход установки в состояние лог. «О»;

S (от английского SET) - раздельный вход установки лог. «1»;

К - вход установки универсального триггера в состояние «0»;

J - вход установки универсального триггера в состояние «1»;

Т - счетный вход;

D (от английского DELAY) - информационный вход установки триггера в состояние, соответствующее логическому уровню на этом входе;

С - управляющий (синхронизирующий) вход .

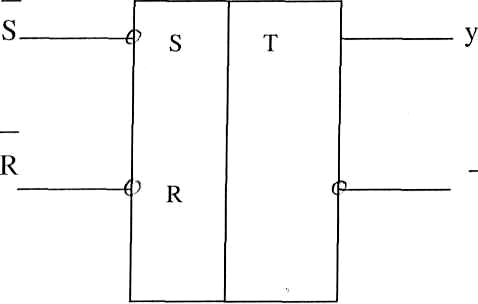

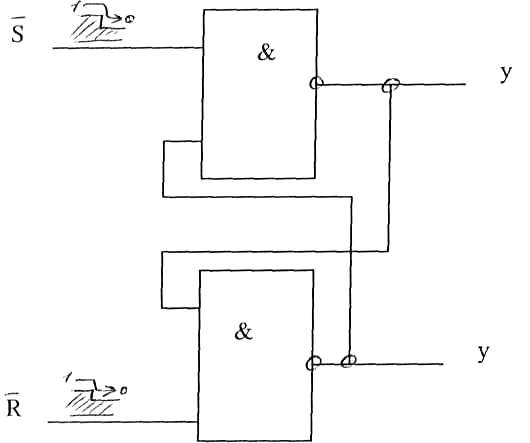

Асинхронные RS-триггеры чаще всего реализуются на базе логических компонентов 2И-НЕ, имеющих инверсные входы. Структурная схема асинхронного RS-триггера представлена на рис.1.

У

Рассмотрим все состояния RS-триггера.

а) если на входах неS=l; неR=l, то состояние триггера не изменяется;

б) если на входе неS=0; неR=l, то триггер опрокинется, т.е. перейдет в «1»«0», а на выходе y=1;

в) если неS=l; неR=0, то триггер опрокинется в состояние «0», а на выходе возникает y=0;

г) при неS=0; неR=0 - состояние триггера неопределенное (и поэтому является «запрещенным»).

RS-триггер имеет статические выходы, т.е. опрокидывание осуществляется при переходе «1» —► «0».

Синхронный rs-триггер

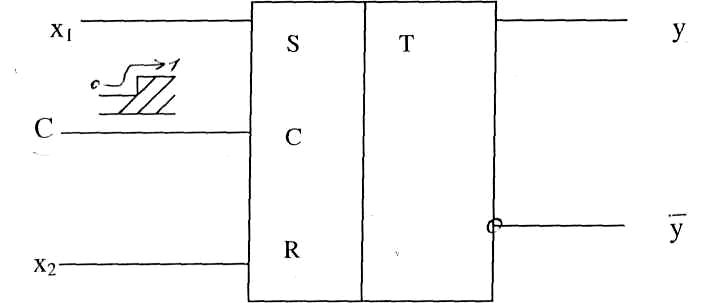

Структурная схема синхронного RS-триггера приведена на рис. 3 и имеет динамический вход синхронизации С

Функциональная схема синхронного RS-триггера (рис.4) выполнена на основе элементов 2И-НЕ

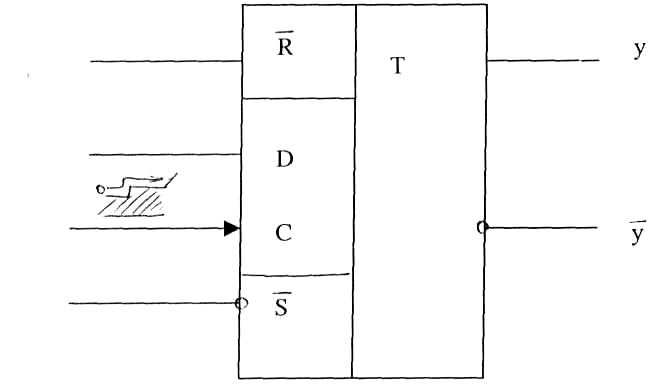

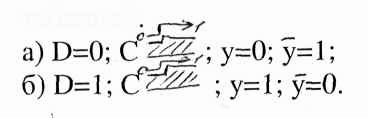

D-триггер имеет один информационный вход (D-вход) и вход синхронизации (С-вход). При положительном перепаде напряжения на входе С триггер переходит в состояние, определяемое уровнем логического сигнала на входе D. D-триггер может иметь также входы установки исходного состояния R и S, рис.5.

один из двух триггеров типа К155ТМ2. Последовательность работы D-триггера может быть представлена таблицей:

Объединяя выводы неу и D, получаем счетный режим D-триггера. При этом динамический вход С является счетным входом.

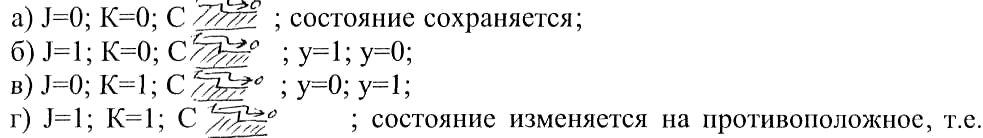

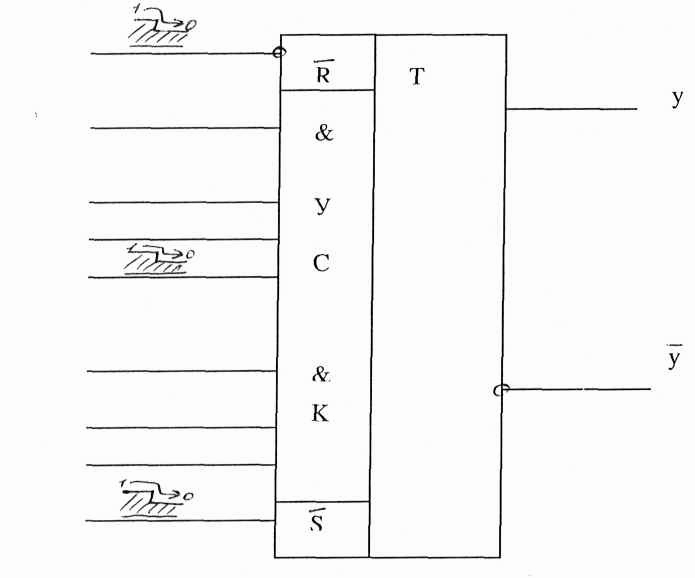

Универсальный JK-тригтер два информационных входа J и К, а также вход синхронизации С. Запись единицы информации осуществляется в момент опрокидывания триггера, т.е. при переходе его из состояния «1» в «0». Это соответствует определению - «статический вход».

Работа JK-триггера иллюстрируется таблицей:

обеспечивается счетный режим.

В сериях ИМС часто встречаются триггеры Ж с расширенной входной логикой. Примером может служить триггер типа К155ТВ1, имеющий по три конъюнктивно связанных входа J и К (рис.6).

Это дает возможность использовать подобные триггеры JK в многоканальных регистровых устройствах, а также в счетчиках с целями параллельного переноса. Наличие установочных входов неS и неR предоставляет дополнительные функциональные возможности при разработке электронной аппаратуры.

ЛАБОРАТОРНАЯ РАБОТА №1

Исследование работы асинхронного RS-триггера

I. ЦЕЛЬ РАБОТЫ

Изучение работы асинхронного RS-триггера

II. ЗАДАНИЕ

Предварительная часть

-

Изучить работу асинхронного RS-триггера. [1,2,3].

-

Начертить функциональную схему асинхронного RS-триггера на базе 2И-НЕ

-

Задать последовательность работы источников сигналов типа STIM1 [4,5]. В данной работе создаются два сигнала Z1 и Z2. Сигнал Z1 образует следующую временную закономерность адекватную последовательности работы по входу S асинхронного RS-триггера:

-

установить «1»;

-

перевести триггер в состояние «0» за время, равное τ;

-

перевести триггер в состояние «1» за время, равное τ;

-

хранить в течение 3τ состояние «1» и после этого перейти в состояние «0»;

-

образовать очередной цикл в момент перехода триггера из «0» в «1»;

-

хранить «1» в течение 3τ после чего перевести триггер в состояние «0».

Сигнал Z2 формирует следующую временную последовательность, рассчитанную на два цикла работы на входе R асинхронного RS-триггера:

-

установить на входе неR - «1»;

-

перевести триггер в состояние «0» и хранить в течение времени 3τ;

-

перевести триггер «0» —► «1» за время τ. При этом триггер опрокидывается, т.е. «0» —►«1», а в триггер запишется «1»;

-

хранить в течение 3τ состояние «1» после чего осуществляется перевод из «1»—► в «0»;

- по окончанию второго цикла за τ устанавливается состояние «1». 4. В таблице даны значения временных параметров τ в наносекундах (10-9).

|

Номер бригады |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

τ |

1 |

2 |

3 |

4 |

1,5 |

2,5 |

3,5 |

4,5 |

5 |