Методическое пособие

.pdf

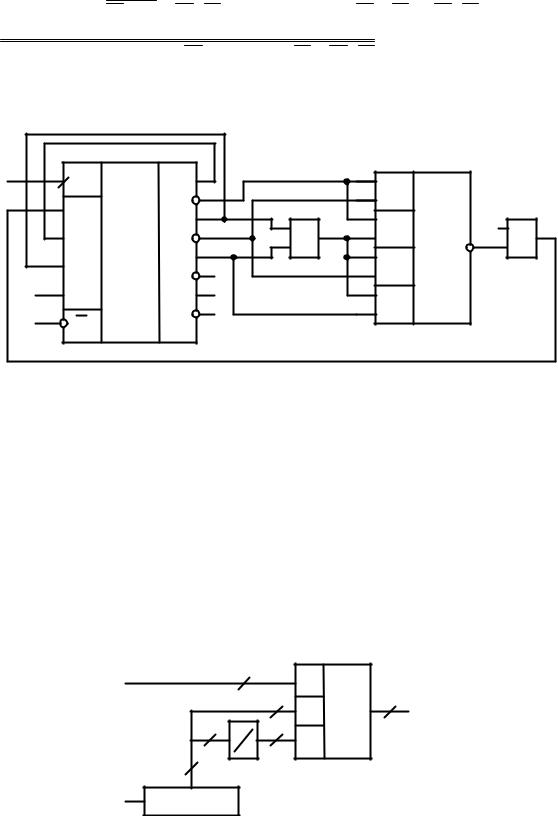

1.21. Разработать преобразователь 4-разрядного прямого кода целого числа x3.x2 x1x0 в обратный F3.F2F1F0 ( x3 и F3 – знаковые разряды).

Решение.

Схема преобразователя приведена на рис. 28. По входам SE выбрана нулевая операция 0000. При x3 = MO = 0, CR n =1 выбирается арифметическая

операция A = 0.x2 x1x0 |

= x3.x2 x1x0 , а при x3 = MO = 1 выполняется операция |

|||||||||||||||

|

|

= |

|

|

= x3.x2 x1x0 , т.е. на выходах Fi получаем обратный код. |

|||||||||||

|

A |

0.x2 x1x0 =1.x2 x1x0 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 28. Преобразователь 4-разрядного прямого кода в обратный на КР1533ИП3

1.22. Разработать преобразователь 4-разрядного обратного кода целого числа x3.x2 x1x0 в дополнительный F3.F2F1F0 ( x3 и F3 – знаковые разряды).

Решение.

Схема преобразователя приведена на рис. 29. По входам SE выбрана

девятая операция 1001, по входу МO – |

арифметическая, |

|

n |

=1 |

– без |

CR |

|||||

переноса. В результате выполняется операция A + B = X +000x3 . |

При |

x3 =0 |

|||

результат операции равен X , а при x3 =1 – |

X +1, что соответствует переходу |

||||

от обратного кода к дополнительному. |

|

|

|

|

|

1.23. Разработать преобразователь 4-разрядного дополнительного кода целого числа x3.x2 x1x0 в обратный F3.F2F1F0 ( x3 и F3 – знаковые разряды).

Решение.

Схема преобразователя приведена на рис. 30. Выполняется постоянно пятнадцатая арифметическая операция (SE=1111, МO=0). Если число Х

положительное ( x3 =0 ), то выполняется функция A = X , если число Х

отрицательное, то A −1 = X −1 что соответствует переходу от дополнительного кода к обратному.

21

|

|

|

|

SE |

ALU |

|

Y |

|

|

|

|

|

|

|

|

|

|||||

“1” |

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

1 |

|

|

CR |

n+4 |

|

|

|

|

|

|

|

|

|

||||

“0” |

|

|

|

2 |

|

|

X |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

||||

|

|

|

|

3 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

x0 |

|

|

|

A0 |

|

|

F0 |

|

F0 |

|

|

|

|

|

|

|

|||||

x1 |

|

|

|

B0 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

|

A1 |

|

|

F1 |

|

F1 |

||

|

|

|

|

|

|

|||||

x2 |

|

|

|

B1 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

|

A2 |

|

|

F2 |

|

F2 |

||

|

|

|

|

|

|

|||||

x3 |

|

|

|

B2 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

|

A3 |

|

|

F3 |

|

F3 |

||

|

|

|

|

|

|

|||||

|

|

|

|

B3 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

“0” |

|

|

|

MO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

“1” |

|

|

|

CRn |

|

|

A=B |

|

|

|

|

|

|

|

|

|

|||||

Рис. 29. Преобразователь 4-разрядного обратного кода в дополнительный

на КР1533ИП3

|

|

|

|

SE |

ALU |

|

Y |

|

|

|

|

|

|

|

|

|

|||||

“1” |

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

1 |

|

|

CR |

n+4 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

2 |

|

|

X |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

3 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x0 |

|

|

|

A0 |

|

|

F0 |

|

F0 |

|

|

|

|

|

|

|

|||||

“0” |

|

|

B0 |

|

|

|

||||

|

|

|

|

|

|

|

|

|||

x1 |

|

|

|

A1 |

|

|

F1 |

|

F1 |

|

|

|

|

|

|

|

|||||

x2 |

|

|

|

B1 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

|

A2 |

|

|

F2 |

|

F2 |

||

|

|

|

|

|

|

|||||

x3 |

|

|

|

B2 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

|

A3 |

|

|

F3 |

|

F3 |

||

|

|

|

|

|

|

|||||

|

|

|

|

B3 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

“0” |

|

|

|

MO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

CRn |

|

|

A=B |

|

|

|

|

|

|

|

|

|

|

||||

Рис. 30. Преобразователь 4-разрядного дополнительного кода в обратный

на КР1533ИП3

2.СЧЁТЧИКИ И РЕИСТРЫ

2.1.Привести схему, реализующую на счётчике КР1533ИЕ7 модуль счёта k = 11 в режиме суммирования. Нарисовать несколько тактов временной диаграммы до и после момента параллельного занесения информации.

Решение.

Модуль счёта k в режиме суммирования определяется по формуле

k = 2n −1− D ,

22

откуда определим число D для параллельного занесения информации:

D = 2n −1−k = 24 −1−11 = 410 = 01002 .

Схема счётчика с модулем k = 11 приведена на рис. 31. Выходная частота следования импульсов Fвых в k раз меньше, чем входная fвх.

|

|

|

|

|

|

|

|

Fвых |

||

|

|

|

|

|

|

|

|

|||

fвх |

|

|

+1 |

CT2 |

CR |

|||||

|

|

|

|

|

||||||

“1” |

|

|

-1 |

|

|

|

|

|

|

|

|

|

|

BR |

|

|

|

||||

|

|

|

|

|

||||||

“0” |

|

|

1 |

|

1 |

|

Q1 |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

2 |

|

|

|

||||

|

|

|

|

2 |

|

|

|

|

||

“1” |

|

|

3 |

|

|

Q2 |

|

|||

|

|

|

|

|||||||

|

|

|

4 |

|

3 |

|

Q3 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

C |

|

|

|

||||

“0” |

|

|

|

4 |

|

Q4 |

|

|

||

|

|

|

|

|

|

|||||

|

|

R |

|

|

||||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 31. Счётчик с модулем счёта k = 11 на КР1533ИЕ7 в режиме суммирования

На рис. 32 приведен фрагмент временной диаграммы работы схемы, приведенной на рис. 31.

fвх |

t |

Q1 |

t |

Q2 |

t |

Q3 |

t |

Q4 |

t |

CR(Fвых,C) |

t |

Рис. 32. Фрагмент временной диаграммы работы схемы, приведенной на рис. 31

2.2. На одной ИМС КР1533ТВ9 и логических элементах той же серии построить генератор чисел 7 – 2 – 4 – 11.

Решение.

Для построения генератора нужна последовательностная схема на 4 состояния (два триггера), к выходам которой подключается выходная логика, имеющая четыре выхода y3 y2 y1 y0 , так как для кодирования числа 11

23

необходимо четыре двоичных разряда. Четыре состояния можно получить в схеме регистра сдвига, суммирующего счётчика, вычитающего счётчика или пересчётного устройства, обеспечивающего любую заданную последовательность состояний. Выберем схему вычитающего двухразрядного счётчика. Выходы yi определим из табл. 13.

|

|

|

Таблица 13 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

y3 =Q2Q1 =Q2Q1; |

||||||||||||

|

|

|

|

|

|

|||||||||||

Q2 |

Q1 |

y3 |

y2 |

y1 |

y0 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||

y2 =Q1; |

||||||||||||||||

0 |

0 |

0 |

1 |

1 |

1 |

|||||||||||

1 |

1 |

0 |

0 |

1 |

0 |

|

|

|

|

|||||||

y1 =Q2 |

|

; |

||||||||||||||

Q1 |

||||||||||||||||

1 |

0 |

0 |

1 |

0 |

0 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||

y0 =Q2. |

||||||||||||||||

0 |

1 |

1 |

0 |

1 |

1 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||

Функциональная схема генератора чисел приведена на рис. 33. Схема построена на одной ИМС КР1533ТВ9 и одной ИМС КР1533ЛА3.

“1” |

S1 T1 |

J1 |

Q1 |

|

y3 |

|

& |

& |

|||

K1 |

||||

|

|

|

С |

C1 |

Q1 |

y2 |

|

|||

|

R1 |

|

|

“1” |

S2 |

T2 |

|

|

|

J2 |

Q2 |

& |

y1 |

|

|

|

|

K2 |

Q2 |

|

|

C2 |

y0 |

||

|

“1”  R2

R2

Рис. 33. Генератор чисел 7 – 2 – 4 – 11 на двух JK-триггерах ИМС КР1533ТВ9 и логических элементах

2.3. На выходах четырех JK-триггеров (две ИМС КР1533ТВ15) и логических элементах этой же серии построить генератор чисел 7 – 2 – 4 – 11. Построить полный граф шестнадцати (24) состояний.

Решение.

Составим таблицу переходов (табл. 14) генератора чисел. С помощью

управляющей табл. 15 J K -триггера заполним столбцы Ji , Ki табл. 14.

24

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 14 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

Q2 |

Q1 |

Q0 |

|

J3 |

K |

3 |

|

J2 |

K2 |

J1 |

K1 |

J0 |

K0 |

|

|||||||||||

|

0 |

1 |

1 |

1 |

0 |

× |

|

× |

0 |

|

× |

1 |

× |

0 |

|

||||||||||||

|

0 |

0 |

1 |

0 |

0 |

× |

|

1 |

× |

|

× |

0 |

0 |

× |

|

||||||||||||

|

0 |

1 |

0 |

0 |

1 |

× |

|

× |

0 |

|

1 |

× |

1 |

× |

|

||||||||||||

|

1 |

0 |

1 |

1 |

× |

0 |

|

1 |

× |

|

× |

1 |

× |

1 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

Таблица 15 |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

Qt →Qt+1 |

|

J |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

K |

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

0 |

0 |

|

0 |

× |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

0 |

1 |

|

1 |

× |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

1 |

0 |

|

× |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

1 |

1 |

|

× |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Составляем карты Карно для |

Ji и |

|

|

i , в избыточных состояниях ставим |

|||||||||||||||||||||||

K |

|||||||||||||||||||||||||||

кресты.

Q |

|

|

|

|

|

Q |

|

|

|

|

||

|

1 |

|

|

|

|

|

|

1 |

|

|

|

|

Q Q |

00 |

01 |

11 |

10 |

Q Q |

00 |

01 |

11 |

||||

3 |

2 |

0 |

3 |

2 |

0 |

|||||||

Q |

|

|

|

|

|

Q |

|

|

|

|

||

|

00 |

x |

x |

x |

0 |

|

00 |

x |

x |

x |

||

|

01 |

1 |

x |

0 |

x |

|

01 |

x |

x |

1 |

||

|

11 |

x |

x |

x |

x |

|

11 |

x |

x |

x |

||

|

10 |

x |

x |

x |

x |

|

10 |

x |

x |

1 |

||

|

|

|

|

|

|

|

J3 |

|

|

|

|

|

|

|

|

Рис. 34. |

|

|

|

|

Рис. 35. |

||||

Q |

|

|

|

|

|

Q |

|

|

|

|

||

|

1 |

|

|

|

|

|

|

1 |

|

|

|

|

Q Q |

00 |

01 |

11 |

10 |

Q Q |

00 |

01 |

11 |

||||

3 |

2 |

0 |

3 |

2 |

0 |

|||||||

Q |

|

|

|

|

|

Q |

|

|

|

|

||

|

00 |

x |

x |

x |

0 |

|

00 |

x |

x |

x |

||

|

01 |

1 |

x |

x |

x |

|

01 |

x |

x |

0 |

||

|

11 |

x |

x |

x |

x |

|

11 |

x |

x |

x |

||

|

10 |

x |

x |

x |

x |

|

10 |

x |

x |

1 |

||

|

|

|

|

|

|

|

J0 |

|

|

|

|

|

|

|

|

Рис. 36. |

|

|

|

|

Рис. 37. |

||||

10

0

x x x

K1

10 x

x x x

K0

По картам Карно составляем логические выражения для Ji и Ki

J3 =Q1 , J2 =1, J1 =1, J0 =Q2 , K3 =0, K2 =0 , K1 =Q0 , K0 =Q3 .

25

Для построения графа состояний выпишем 16 – 4 = 12 избыточных состояний (табл. 16), по уравнениям Ji , Ki заполним значения Ji , Ki , а по

табл. 17 переключения JK -триггера определим следующие состояния в момент времени t+1.

Таблица 16

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t+1 |

|

|

|

Q10 |

Q3 Q2 Q1 Q0 |

J3 K |

3 |

J2 |

K2 |

J1 |

K1 |

J0 |

K0 |

Q3 Q2 Q1 Q0 |

Q10 |

|||||||||||||

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

14 |

|||||||

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

14 |

|||||||

3 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

6 |

|||||||

5 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

10 |

|||||||

6 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

|||||||

8 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

6 |

|||||||

9 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

7 |

|||||||

10 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

4 |

|||||||

12 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

3 |

|||||||

13 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

3 |

|||||||

14 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

9 |

|||||||

15 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

3 |

|||||||

Таблица 17

J |

K |

|

Qn+1 |

||

0 |

0 |

|

0 |

||

0 |

1 |

|

Qn |

||

|

|

|

|

|

|

1 |

0 |

|

Q |

n |

|

1 |

1 |

|

1 |

||

Граф состояний показан на рис. 38. Из графа следует, что схема не имеет тупиковых состояний и при любом сбое из любого избыточного состояния в конечном счёте вернётся к генерации состояний 7 – 2 – 4 – 11. Функциональная схема генератора приведена на рис. 39.

Возможно объединение Ji с Ki и использование JK -триггера как D-триггера с определением Di , однако в этом случае потребуется дополнительная логика.

2.4. В 3-разрядный (на КР1533ТМ2) регистр Q3Q2Q1 последовательности максимальной длины ПМД с обратной связью Dr =Q3 Q2 добавить логику на

элементах той же серии для получения модуля счета k =5 методом скачка (скачок из a1 =001, Dr =1) и обеспечить также выход из нулевого состояния.

Решение.

Булеву функцию Dr обратной связи с учетом выхода из нуля можно записать в виде

26

Dr =Q2 Q3 +Q3 Q2Q1 +Q3 Q2 Q1 =Q2 Q3 +Q3 Q2 (Q1 +Q1 )=Q2 Q3 +Q3 Q2 =

=Q2 Q3 +Q2Q3 +Q2Q3 +Q3 Q2 =Q2 Q3 +Q2 (Q3 +Q3 )=Q2 Q3 +Q2 =Q2 Q3 Q2

На рис. 40 показана функциональная схема пересчетного устройства.

7

7  2

2  4

4  11

11

|

|

|

10 |

5 |

|

|

9 |

|

12 |

|

|

0 |

14 |

15 |

3 |

6 |

8 |

13

1

Рис. 38. Граф генератора чисел 7 – 2 – 4 – 11

|

|

DD1 |

|

|

DD2 |

“1” |

S1 |

T |

“1” |

S1 |

T |

|

J1 |

|

Q3 |

J1 |

Q1 |

|

|

|

|||

“0” |

K1 |

|

|

K1 |

Q1 |

|

C1 |

|

|

C1 |

|

|

|

|

|

||

|

R1 |

|

“1” |

R1 |

|

“1” |

S2 |

T |

|

S2 |

T |

|

J2 |

|

Q2 |

J2 |

Q0 |

|

|

|

|||

“0” |

K2 |

|

|

K2 |

|

|

C2 |

|

|

C2 |

|

“1” |

R2 |

|

“1” |

R2 |

|

С |

|

|

|

|

|

Рис. 39. Генератор чисел 7 – 2 – 4 – 11 на четырёх JK-триггерах КР1533ТВ15

27

Рис. 40. Пересчётное устройство с модулем счёта k = 5

Функцию Dr =Q2 Q3 Q2 можно реализовать также на одном корпусе КР1533ЛП12 по схеме рис. 41.

+5В

Q3 |

=1 |

=1 |

Q2 |

|

|

|

“1” |

|

|

|

|

“0” |

=1 |

|

|

|

“1” |

=1 |

Dr |

|

||

|

|

Рис. 41. Реализация функции Dr = Q2 Q3 Q2 на одном корпусе КР1533ЛП12

Граф пересчетного устройства показан на рис. 42.

Рис. 42. Граф пересчетного устройства, приведенного на рис. 40

2.5. В |

задаче 2.4 обеспечить k =6 (скачок должен быть из состояния |

a3 =011, Dr |

=0 ). Регистр построить на КР1533ТМ8. |

Решение.

Обратную связь Dr запишем в следующем виде:

Dr =(Q2 Q3 ) Q3Q2Q1 +Q3 Q2 Q1 .

Если нанести это выражение на карту Карно, то конъюнктивный терм Q3 Q2 Q1 упростится до Q2 Q1 .Тогда

28

Dr =(Q2 Q3 ) Q3Q2Q1 +Q2 Q1 =(Q2 Q3 )(Q3 +Q2 +Q1 )+Q2 Q1 =

=(Q2 Q3 )Q3 +(Q2 Q3 )Q2 +(Q2 Q3 )Q1 +Q2 Q1

Функциональная схема приведена на рис. 43 и содержит 3 корпуса ИМС

(КР1533ТМ8, КР1533ЛР13, КР1533ЛП5).

C |

C |

T |

Q1 |

|

& |

1 |

|

|

D1 |

|

Q1 |

|

|

||

|

|

|

|

|

|

||

|

|

Q2 |

|

& |

“1” |

|

|

|

|

|

|

|

|||

|

D2 |

|

Q2 |

=1 |

=1 |

||

|

D3 |

|

Q3 |

|

& |

|

|

|

|

Q3 |

|

|

|

||

|

|

|

|

|

|

|

|

|

D4 |

|

Q4 |

|

& |

|

|

“1” |

R |

|

Q4 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

Рис. 43. Функциональная схема к задаче 2.5

2.6. Построить на КР1533ТМ2 и ИМС той же серии 3-разрядный счетчик, который при управляющем сигнале M = 1 работает как счетчик в коде Грея, а при M = 0 как двоичный суммирующий счетчик.

Решение.

Можно составить таблицу переходов, нанести на карты Карно функции возбуждения Di D-триггеров, минимизировать межразрядные связи как

функции f (Q2 ,Q1,Q0 ,M ), преобразовать их для реализации на логических

элементах с минимальным количеством корпусов.

Рассмотрим ещё один вариант решения задачи по схеме рис. 44, где X/Y – преобразователь двоичного кода в код Грея.

M |

|

|

1 |

|

A |

MS |

|

|

|

|

|

|

|||

|

|

|

|

3 |

0 |

3 |

Y |

|

|

3 |

X |

3 |

|

||

|

|

1 |

|

|

|||

|

3 |

|

Y |

G |

|

|

|

|

B |

|

|

|

|

|

|

С |

CT2 |

|

|

|

|

|

|

Рис. 44. Структурная схема счётчика (с выходами Y), который при M = 1

работает как счетчик в коде Грея (G), а при M = 0

как двоичный (B) суммирующий счетчик

29

Сам счётчик СТ2 постоянно работает как двоичный суммирующий счётчик, но на выход Y = y2 y1 y0 мультиплексора-селектора в зависимости от

сигнала по входу M проходит либо двоичный код B =b2b1b0 , либо код Грея

G = g2 g1g0 .

Как известно gi =bi bi+1 , при 0 ≤i ≤ n −1 и gn =bn . Функциональная схема задачи приведена на рис. 45.

Рис. 45. Функциональная схема к задаче 2.6

Схема на рис. 45 построена на четырёх корпусах серии КР1533 (2 корпуса КР1533ТМ2, 1 корпус КР1533ЛП5, 1 корпус КР1533КП16).

2.7. Синтезировать на КР1533ТМ2 и логических элементах той же серии асинхронный суммирующий счётчик с остановкой в состоянии a10 = 1010. Для

повторного цикла счёта предусмотреть общий вход сброса R . Привести несколько тактов временной диаграммы ( a8 ,a9 ,a10 ,a0 ,a1 ).

Решение.

Необходимо разработать комбинационную схему KC (рис. 46), выход которой C′= C (С – вход счётных импульсов) при состояниях счётчика a0 −a9 и

C′= 0 при a10 = 1010, а при a11 −a15 – безразличное значение. Покажем это на карте Карно (рис. 47).

30