- •Содержание

- •Введение

- •1 Цель курсового проектирования

- •2 Задание на курсовое проектирование

- •3 Разработка структурной схемы вычислительного устройства

- •4 Выбор системы команд и определение форматов команд вычислительного устройства

- •5 Разработка алгоритма командного цикла вычислительного устройства

- •5.1 Алгоритм выборки команды

- •5.2 Алгоритм перехода к подпрограмме прерывания

- •5.3 Алгоритм формирования операндов для арифметико-логического устройства

- •5.4 Алгоритм выполнения команд передачи управления

- •5.5 Алгоритм вызова подпрограммы

- •5.6 Алгоритм возврата из подпрограммы

- •5.7 Алгоритмы операций со стеком

- •5.8 Алгоритмы выполнения операций с ву

- •5.9 Алгоритмы системных операций

- •5.10 Алгоритм выполнения операции записи в озу

- •5.11 Алгоритм выполнения операции чтения из озу

- •6 Разработка алгоритмов выполнения арифметических и логических операций

- •6.1 Алгоритм выполнения операций сложения и вычитания

- •6.2 Алгоритм выполнения логических операций

- •6.3 Алгоритм выполнения операции умножения

- •6.4 Алгоритм выполнения операции деления

- •7 Проектирование операционного автомата устройства выполнения команд

- •8 Проектирование операционного автомата арифметико-логического устройства

- •9 Проектирование устройств управления процессора и алу двухступенчатой организации процесса управления

- •9.1. Проектирование управляющего автомата устройства управления процессора

- •9.2. Проектирование управляющего автомата устройства управления алу

- •10 Пример кодирования пзу мк мпа алу для реализации микропрограммы операций сложения и вычитания

- •11 Разработка функциональной схемы процессора

- •Заключение

- •Список использованной литературы

- •Приложение

2 Задание на курсовое проектирование

Вариант задания №2

Исходные данные для проектирования описаны в таблице 1

|

Характеристика команд |

АЛУ |

ЗУ |

УУ |

Характеристи-ка данных | |||||||

|

Адрес-ность |

Формат |

Способ адреса-ции |

Разрядность |

Разря-дность |

Емкость |

Тип УА |

Разрядность | ||||

|

2 |

AS, RR |

П К О |

32 |

8 |

16 |

ППЛ |

16 | ||||

Таблица 1 – Задание на курсовое проектирование

Список операций, выполняемых устройством, должен быть следующим:

арифметические операции:

сложение;

вычитание;

умножение;

деление;

логические операции:

дизъюнкция;

конъюнкция;

сложение по модулю два;

условный переход по значению >0;

условный переход по значению <0;

условный переход по значению =0;

условный переход по переполнению;

безусловный переход;

вызов подпрограммы;

возврат из подпрограммы;

операции с запоминающим устройством:

запись в запоминающее устройство;

чтение из запоминающего устройства;

операции со стеком:

запись;

чтение;

сложение со стеком;

вычитание из стека;

операции с внешними устройствами:

запись во внешнее устройство;

чтение из внешнего устройства;

системные операции:

останов;

разрешение прерывания;

запрещение прерывания;

возврат из прерывания;

загрузка регистра базы;

загрузка указателя стека.

3 Разработка структурной схемы вычислительного устройства

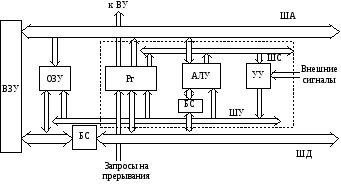

В курсовом проекте необходимо разработать процессор и организацию его взаимодействия с запоминающими и внешними устройствами. Структурная схема вычислительного устройства представлена на рисунке 1

Рисунок 1 – Структурная схема вычислительного устройства.

ОЗУ – оперативно запоминающее устройство;

Pr – блок регистров и логических схем;

АЛУ – арифметико-логическое устройство;

УУ – устройство управления;

БС – блок согласования разрядности шин;

ША – шина адреса;

ШД – шина данных;

ШУ – шина управления;

ШС – шина состояния;

ВУ – внешнее устройство.

4 Выбор системы команд и определение форматов команд вычислительного устройства

Определим разрядности основных шин и блоков, регистров, а так же разрядности команд и данных и количество регистров, обеспечивающих выполнение заданного набора операций.

Разрядность

шины данных (ШД) определяется из варианта

задания. В нашем случае разрядность ШД

равна 16, т.е. ШД (15-0). Для определения

разрядности шины адреса (ША) используем

заданные в таблице 2.1

параметры запоминающего устройства:

разрядность слова и емкость. Определим

количество ячеек памяти:

,

для того, чтоб адресовать все ячейки

ОЗУ необходима разрядность ША равная

11, т.к. 211

= 2048. Получаем

ША(10-0).

,

для того, чтоб адресовать все ячейки

ОЗУ необходима разрядность ША равная

11, т.к. 211

= 2048. Получаем

ША(10-0).

Что бы найти разрядность шины управления (ШУ) надо определить формат команд. Для кодирования операций нам понадобиться поле кода операций (КОП). Так как количество операций, которые необходимо реализовать в разрабатываемом устройстве 28, нам понадобиться 5 двоичных разрядов для двоичного кодирования.

После выбора количества разрядов КОП необходимо закодировать все операции системы команд представленные в таблице 2.

Таблица 2 – Кодирование команд

|

№ п/п |

Код операции |

Тип операции |

Мнемоника операции |

|

1 |

00000 |

Сложение |

add |

|

2 |

00001 |

Вычитание |

sub |

|

3 |

00010 |

Умножение |

mul |

|

4 |

00011 |

Деление |

div |

|

5 |

00100 |

ИЛИ |

or |

|

6 |

00101 |

И |

and |

|

7 |

00110 |

ИСКЛЮЧАЮЩЕЕ ИЛИ |

xor |

|

8 |

00111 |

Условный переход, если >0 |

jns |

|

9 |

01000 |

Условный переход, если <0 |

js |

|

10 |

01001 |

Условный переход, если =0 |

jz |

|

11 |

01010 |

Условный переход по переполнению |

jo |

|

12 |

01011 |

Безусловный переход |

jmp |

|

13 |

01100 |

Переход к подпрограмме |

call |

|

14 |

01101 |

Выход из подпрограммы |

ret |

|

15 |

01110 |

Запись в ЗУ |

stm |

|

16 |

01111 |

Чтение из ЗУ |

ldm |

|

17 |

10000 |

Запись в стек |

push |

|

18 |

10001 |

Чтение из стека |

pop |

Продолжение таблицы 2

|

№ п/п |

Код операции |

Тип операции |

Мнемоника операции |

|

19 |

10010 |

Сложение со стеком |

sadd |

|

20 |

10011 |

Вычитание из стека |

ssub |

|

21 |

10100 |

Запись в ВУ |

out |

|

22 |

10101 |

Чтение из ВУ |

in |

|

23 |

10110 |

Останов |

stop |

|

25 |

10111 |

Разрешение прерывания |

sif |

|

26 |

11000 |

Запрещение прерывания |

rif |

|

27 |

11001 |

Возврат из прерывания |

iret |

|

28 |

11010 |

Загрузка регистра базы |

ldb |

|

29 |

11011 |

Загрузка указателя стека |

ldsp |

В задании дано два формата команды, чтоб их закодировать достаточно одного бита: ФК AS = 1, ФК RR = 0.

Для того чтобы закодировать содержимое поля тип адресации (ТА), необходимо два разряда, так как задано три типа адресации. Для прямой адресации (П) код ТА = 00, для косвенной (К) – ТА = 01 и для относительной (О) – ТА = 10.

Для команды формата AS получаем:

Рисунок 2 – формат команды AS

Первым операндом данной команды является аккумулятор, так как его местоположение определяется однозначно, в команде он явно не указывается. Вторым операндом для этой команды является поле адреса ячейки оперативной памяти S разрядности 11, равную разрядности ША. Так как разрядность команды должна быть кратна степени двойки, дополним ее до 32 разрядов. Получаем разрядность формата команды (31-0).

Для того, чтобы определить формат RR необходимо выбрать разрядность поля R. Для выбора разрядности поля R сначала необходимо выбрать число регистров общего назначения (РОН). Пусть число РОН будет 8, тогда для кодирования номеров регистров достаточно 3 бит.

Получаем следующий формат команды для RR:

Рисунок

3– формат команды RR

Рисунок

3– формат команды RR

Для удобства организации выборки команды из памяти, анализа команды и определения разрядности шины управления (ШУ) дополним разрядность команды этого формата так же до 32 разрядов.

Разрядность ШУ равна разрядности формата команды, т.е. получаем ШУ(31-0)

Составим содержательную таблицу 3 кодирования всех вариантов форматов команд

Таблица 3 – Кодирование форматов команд

|

Код операции |

Формат команды |

Тип адресации (ТА) |

Код ТА |

Содержание операции | ||||

|

Арифметические | ||||||||

|

add 00000 |

RR |

П |

00 |

РОН[R]:=РОН[R1]+РОН[R2] | ||||

|

К |

01 |

РОН[R]:=OP[РОН[R1]]+OP[РОН[R2]] | ||||||

|

О |

10 |

РОН[R]:=OP[B+РОН[R1]]+OP[B+РОН[R2]] | ||||||

|

AS |

П |

00 |

A:= A +OP[S] | |||||

|

К |

01 |

A:= A +OP[OP[S]] | ||||||

|

О |

10 |

A:= A +OP[B+S] | ||||||

|

sub 00001 |

RR |

П |

00 |

РОН[R]:=РОН[R1]-РОН[R2] | ||||

|

К |

01 |

РОН[R]:=OP[РОН[R1]]-OP[РОН[R2]] | ||||||

|

О |

10 |

РОН[R]:=OP[B+РОН[R1]]-OP[B+РОН[R2]] | ||||||

|

AS |

П |

00 |

A:= A -OP[S] | |||||

|

К |

01 |

A:= A -OP[OP[S]] | ||||||

|

О |

10 |

A:= A -OP[B+S] | ||||||

|

mul 00010 |

RR |

П |

00 |

РОН[R]:=РОН[R1]*РОН[R2] | ||||

|

К |

01 |

РОН[R]:=OP[РОН[R1]]*OP[РОН[R2]] | ||||||

|

О |

10 |

РОН[R]:=OP[B+РОН[R1]]*OP[B+РОН[R2]] | ||||||

|

AS |

П |

00 |

A:= A *OP[S] | |||||

|

К |

01 |

A:= A *OP[OP[S]] | ||||||

|

О |

10 |

A:= A *OP[B+S] | ||||||

|

div 00011 |

RR |

П |

00 |

РОН[R]:=РОН[R1]/РОН[R2] | ||||

|

К |

01 |

РОН[R]:=OP[РОН[R1]]/OP[РОН[R2]] | ||||||

|

О |

10 |

РОН[R]:=OP[B+РОН[R1]]/OP[B+РОН[R2]] | ||||||

|

AS |

П |

00 |

A:= A /OP[S] | |||||

|

К |

01 |

A:= A /OP[OP[S]] | ||||||

|

О |

10 |

A:= A /OP[B+S] | ||||||

Продолжение таблицы 3

|

Код операции |

Формат команды |

Тип адресации (ТА) |

Код ТА |

Содержание операции | ||||

|

Логические | ||||||||

|

or 00100 |

RR |

П |

00 |

РОН[R]:=РОН[R1] | ||||

|

К |

01 |

РОН[R]:=OP[РОН[R1]]

| ||||||

|

О |

10 |

РОН[R]:=OP[B+РОН[R1]] | ||||||

|

AS |

П |

00 |

A:=

A

| |||||

|

К |

01 |

A:=

A

| ||||||

|

О |

10 |

A:=

A

| ||||||

|

and 00101 |

RR |

П |

00 |

РОН[R]:=РОН[R1] | ||||

|

К |

01 |

РОН[R]:=OP[РОН[R1]]

| ||||||

|

О |

10 |

РОН[R]:=OP[B+РОН[R1]] | ||||||

|

AS |

П |

00 |

A:=

A

| |||||

|

К |

01 |

A:=

A

| ||||||

|

О |

10 |

A:=

A

| ||||||

|

xor 00110 |

RR |

П |

00 |

РОН[R]:=РОН[R1] | ||||

|

К |

01 |

РОН[R]:=OP[РОН[R1]] | ||||||

|

О |

10 |

РОН[R]:=OP[B+РОН[R1]] | ||||||

|

xor 00110 |

AS |

П |

00 |

A:=

A

| ||||

|

К |

01 |

A:=

A

| ||||||

|

О |

10 |

A:=

A

| ||||||

|

Команды передачи управления | ||||||||

|

jns 00111 |

RR |

П |

00 |

if (SF = 0) and (ZF=0) then PC:=РОН[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

if (SF = 0) and (ZF=0) then PC:= A | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

js 01000 |

RR |

П |

00 |

if (SF = 1) then PC:=РОН[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

if (SF = 1) then PC:= A | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

jz 01001 |

RR |

П |

00 |

if (ZF = 1) then PC:=РОН[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

if (ZF = 1) then PC:= A | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

Продолжение таблицы 3

|

Код операции |

Формат команды |

Тип адресации (ТА) |

Код ТА |

Содержание операции | ||||

|

jo 01010 |

RR |

П |

00 |

if (OF = 1) then PC:=РОН[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

if (OF = 1) then PC:= A | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

jmp 01011 |

RR |

П |

00 |

PC:=РОН[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

PC:= A | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

call 01100 |

RR |

П |

00 |

SP:= SP-2, OP[SP]:=PC+1 PC:=РОН[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

SP:= SP-2, OP[SP]:=PC+1 PC:= A | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

ret 01101 |

|

П |

00 |

PC:=OP[SP] SP:=SP+2 | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

Операции с ЗУ | ||||||||

|

stm 01110 |

RR |

П |

00 |

POН[R1]:= РОН[R2] | ||||

|

К |

01 |

OP[РОН[R1]]:= РОН[R2] | ||||||

|

О |

10 |

OP[B+ РОН[R1]]:= РОН[R2] | ||||||

|

AS |

П |

00 |

OP[S]:= A | |||||

|

К |

01 |

OP[OP[S]]:= A | ||||||

|

О |

10 |

OP[B+S]:= A | ||||||

|

ldm 01111 |

RR |

П |

00 |

РОН[R]:= РОН[R1] | ||||

|

К |

01 |

РОН[R] := OP[РОН[R1]] | ||||||

|

О |

10 |

РОН[R]:= OP[B+РОН[R1]] | ||||||

|

AS |

П |

00 |

A:= OP[S] | |||||

|

К |

01 |

A:= OP[OP[S]] | ||||||

|

О |

10 |

A:= OP[B+S] | ||||||

Продолжение таблицы 3

|

Код операции |

Формат команды |

Тип адресации (ТА) |

Код ТА |

Содержание операции | ||||

|

Операции со стеком | ||||||||

|

push 10000

|

RR |

П |

00 |

SP:=SP-1, OP[SP]:=РОН[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

SP:=SP-1, OP[SP]:=OP[S] | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

pop 10001 |

RR |

П |

00 |

РОН[R]:= OP[SP], SP:=SP+1 | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

OP[S]:= OP[SP], SP:=SP+1 | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

sadd 10010 |

RR |

П |

00 |

OP[SP]:= OP[SP]+POH[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

OP[SP]:= OP[SP]+A | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

ssub 10011 |

RR |

П |

00 |

OP[SP]:= OP[SP]-POH[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

OP[SP]:= OP[SP]-A | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

Операции с ВУ | ||||||||

|

out 10100 |

RR |

П |

00 |

RgED:=РОН[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

RgED:=OP[S] | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

in 10101 |

RR |

П |

00 |

РОН[R]:= RgED | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

OP[S]:= RgED | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

Продолжение таблицы 3

|

Код операции |

Формат команды |

Тип адресации (ТА) |

Код ТА |

Содержание операции | ||||

|

Системные операции | ||||||||

|

stop 10110 |

RR |

П |

00 |

WF:=0 | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 | ||||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

sif 10111 |

RR |

П |

00 |

IF:=1 | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 | ||||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

rif 11000 |

RR |

П |

00 |

IF:=0 | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 | ||||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

iret 11001 |

|

П |

00 |

PC:=OP[SP], SP:=SP+1 RgF:=OP[SP], SP:=SP+1 | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

ldb |

RR |

П |

00 |

B:=РОН[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

B:=OP[S] | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

ldsp |

RR |

П |

00 |

SP:=РОН[R] | ||||

|

К |

01 | |||||||

|

О |

10 | |||||||

|

AS |

П |

00 |

SP:=OP[S] | |||||

|

К |

01 | |||||||

|

О |

10 | |||||||

Примечание. В данной таблице приняты следующие сокращения наименований и условные обозначения содержимого полей, ячеек ОП и регистров: R1, R2,S – значения полей из кода инструкции; OP – операнд из памяти; А – аккумулятор; SP – регистр – указатель стека; PC – регистр – программный счетчик; AS – адресация «аккумулятор – ячейка оперативной памяти»; RR – адресация «регистр–регистр»; RgED – регистр внешнего устройства; RgF – регистр флагов; WF – флаг пуска-останова процессора; SF – флаг знака; OF – флаг переполнения; ZF – флаг нуля; [address] – операнд из ячейки с адресом address; RB – регистр базы; IF – флаг прерывания.

РОН[R2]

РОН[R2] OP[РОН[R2]]

OP[РОН[R2]] OP[B+РОН[R2]]

OP[B+РОН[R2]] OP[S]

OP[S] OP[OP[S]]

OP[OP[S]] OP[B+S]

OP[B+S] РОН[R2]

РОН[R2] OP[РОН[R2]]

OP[РОН[R2]] OP[B+РОН[R2]]

OP[B+РОН[R2]] OP[S]

OP[S] OP[OP[S]]

OP[OP[S]]

OP[B+S]

OP[B+S] РОН[R2]

РОН[R2] OP[РОН[R2]]

OP[РОН[R2]] OP[B+РОН[R2]]

OP[B+РОН[R2]] OP[S]

OP[S] OP[OP[S]]

OP[OP[S]]

OP[B+S]

OP[B+S]