- •Содержание

- •1. Описание проектируемой интегральной схемы и ее конструктивно - технологической реализации

- •Моделирование схемы

- •3. Проектирование топологии элементов схемы

- •3.1 Выбор исходных данных

- •3.2 Расчет конструктивных размеров и параметров планарных транзисторов

- •3.3 Расчёт резисторов

- •4. Описание технологии проектируемой имс

- •5. Выбор корпуса

- •6. Топология ис

- •Заключение

- •Список литературы

Содержание

3. Проектирование топологии элементов схемы 7

3.1 Выбор исходных данных 7

3.2 Расчет конструктивных размеров и параметров планарных транзисторов 8

3.3 Расчёт резисторов 13

4. Описание технологии проектируемой ИМС 17

5. Выбор корпуса 18

6. Топология ИС 19

Заключение 25

Список литературы 26

1. Описание проектируемой интегральной схемы и ее конструктивно - технологической реализации

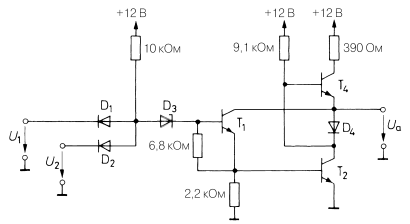

Схема представляет собой логический элемент «И-НЕ», реализованный на модифицированной диодно-транзисторной логике (МДТЛ). Принцип действия ДТЛ заключается в следующем: ток базы транзистора VT1 протекает через резистор R1 при запертых входных диодах VD1 и VD2, то есть, когда все входные напряжения находятся в состоянии логической «1», транзистор VT1 открыт и находится в состоянии логического «0». Таким образом, реализуется функция «И-НЕ». Отличие МДТЛ от обычной ДТЛ заключается в том, что сдвоенный диод VD3 заменен стабилитроном. В результате уровень переключения по входу поднят до 6 В, и при напряжении питания 12 В запас помехоустойчивости достигает 5 В. Чтобы повысить коэффициент разветвления по выходу, элементы медленнодействующей помехоустойчивой логики (МПЛ) снабжаются двухтактным оконечным каскадом, представляющим собой эмиттерный повторитель. При запирании транзистора VT2 выходной ток протекает через эмиттерный повторитель VT3. Как только VT2 начинает проводить ток, потенциал его коллектора становится низким. В случае омической выходной нагрузки выходное напряжение также падает. При емкостной нагрузке через через транзистор VT2 должен протечь ток разряда конденсатора. Чтобы в таком случае транзистор VT3 был заперт, предусмотрен диод VD4, пропускающий ток разряда через проводящий транзистор VT2. Транзисторы, обладающие малым быстродействием, позволяют искусственно увеличить время переключения, а применение внешних конденсаторов делает его еще большим. Благодаря этому короткие импульсы помех не страшны даже тогда, когда их амплитуда превышает запас помехоустойчивости.

Рис.1 – схема логического элемента МПЛ И-НЕ

Моделирование схемы

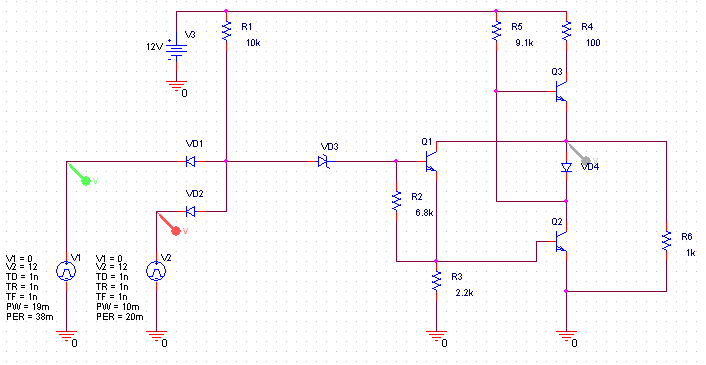

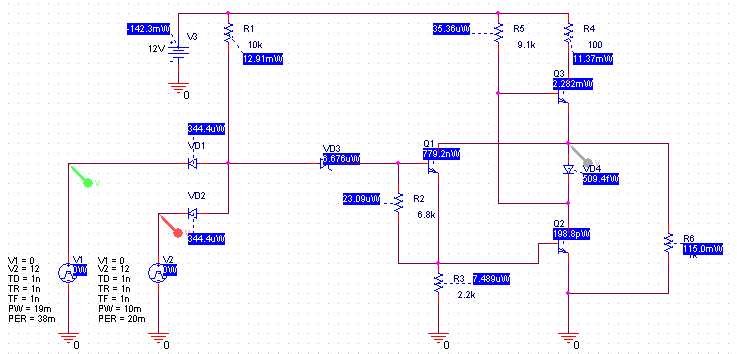

Для проверки работоспособности схемы проведем моделирование в среде Orcad(рис.2).

Рис.2 - Модель ЛЭ в среде OrCAD.

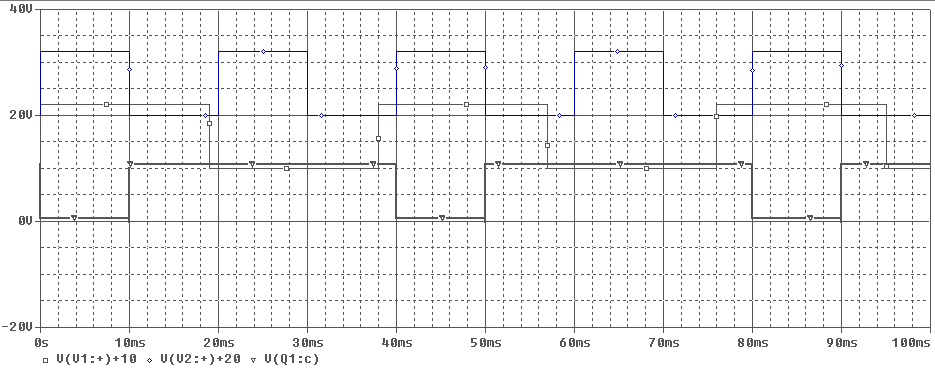

На рис.3 представлен выходной сигнал, по которому можно судить о работоспособности схемы.

Рис.3 - Результаты моделирования, напряжение на выходе

Рис.4 - Рабочие токи

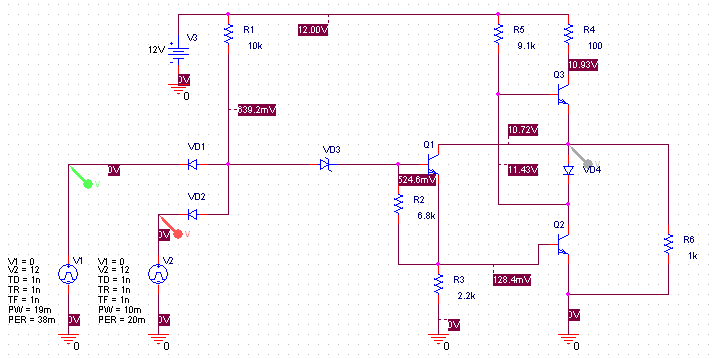

Максимальный ток эмиттера равен 10.72 mА, ток коллектора равен 10.66mА (транзисторVT3).

Рис.5 - Рабочие напряжения

Рис.6 – Мощности, выделяемые на резисторах схемы

3. Проектирование топологии элементов схемы

3.1 Выбор исходных данных

Для дальнейших расчетов примем исходные данные, приведенные в таблице 1. Значения параметров выбраны в соответствии с технологическими требованиями и возможностями ЗАО «ГРУППА КРЕМНИЙ-ЭЛ».

Таблица 1

|

Название параметра |

Обозначение |

Численные данные |

|

Макс. напряжение коллектор-база |

UКБ |

15 В |

|

Макс. обратное напряжение эмиттер-база |

UЭБ |

7 В |

|

Глубина коллекторного перехода |

xjk |

2,5 мкм |

|

Приповерхностная концентрация акцепторов в базе |

Nas |

2.5∙1018см–3 |