ЭВУ 2 семестр / Презентации ЭВУ в пдф / Кэширование 2

.pdf

Lection 14

Кэширование памяти (продолжение)

•Физический факультет, ЭВУ и системы, 7 семестр,2013 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2013 Dr. Mokhovikov

Outline

Структура записи в кэш :

●строка кэша;

●размер тэга и индекса .

Уровни кэша :

●Cache L1;

●Cache L2;

●Cache L3.

●Кэш жертв.

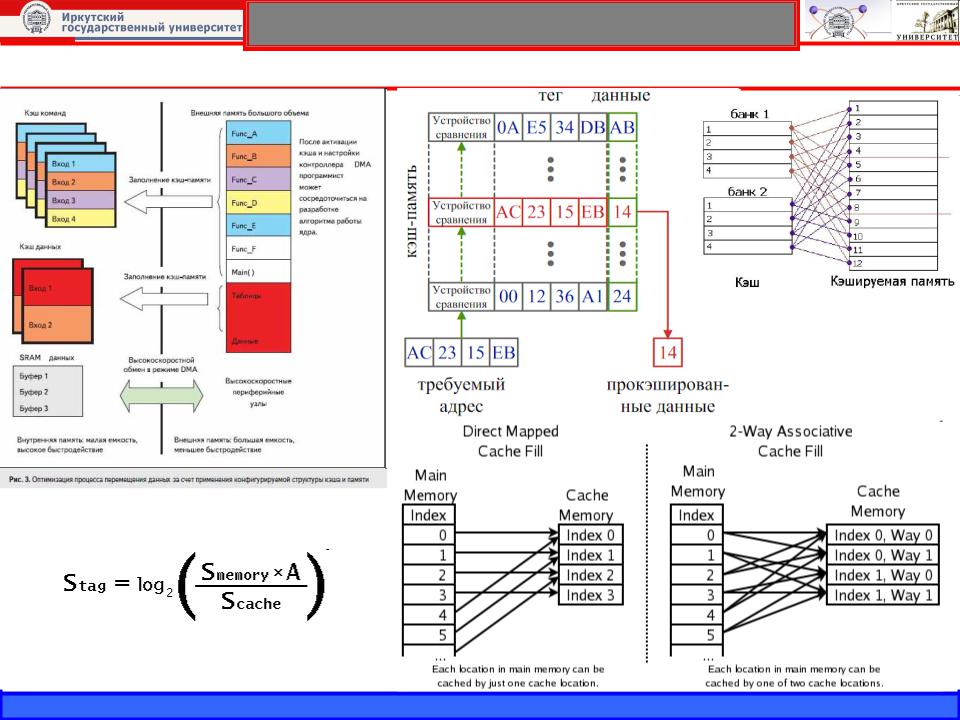

Способы отображения основной памяти на кэш :

●случайное отображение;

●детерминированное отображение;

●комбинирование отображение.

Архитектуры кэша:

●кэш прямого отображения;

●наборно-ассоциативный кэш;

●полностью ассоциативный кэш.

Список используемой литературы

•Физический факультет, ЭВУ и системы, 7 семестр,2013 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2013 Dr. Mokhovikov

|

|

|

Структура записи в кэш |

|||

Типичная структура записи в кэше |

|

|

|

|

|

|

dynamic |

static |

|

|

|||

Блок данных |

тег |

|

индекс |

смещение |

бит |

|

|

актуальности |

|||||

|

|

|

|

|

||

непосредственную копию |

|

|

|

|

данная запись содержит |

|

данных из основной памяти. |

|

|

|

|

актуальную (самую свежую) копию. |

|

Адрес памяти разделяется (от старших бит к младшим) |

||||||

|

|

|

на тег, индекс и смещение. |

|

||

Для абстрактной системы с макс. |

Размер индекса зависит от |

При обращении к такой кэшу происходит |

||||

|

|

|

|

|

||

кэшируемым объёмом RAM в |

|

размеров сегмента кэш- |

|

сравнение тега адреса с тегами всех |

||

1Гб и кэш-памятью (неважно |

|

памяти и строки. |

|

строк кэша, причем это сравнение |

||

какого уровня) размером в 1Мб с |

Фактически, его должно быть |

происходит за один такт. если в |

||||

2-канальной ассоциативностью |

достаточно для нумерации |

результате сравнения тег адреса |

||||

совпадет с тегом одной из строк, то это |

||||||

потребуется ровно 11 бит для |

|

всех строк в пределах |

|

|||

|

|

значит, что произошло КЭШ попадание, и |

||||

каждого тэга. |

|

отдельно взятого сегмента. |

||||

|

нужный байт будет прочитан из |

|||||

|

|

|

|

|

||

Другими словами, для адресации |

Например, если имеется |

|

выбранной строки по полю |

|||

любым отдельным тэгом 1Гб / |

сегмент кэш-памяти в 512Кб |

смещения. Если же тег адреса не |

||||

512Кб = 2048 сегментов памяти |

с 32-байтными строками, то |

совпал ни с одним тегом строк, то это – |

||||

потребуется log2(2048) = 11 бит. |

размер индекса составит |

|

промах и нужная строка в кэша |

|||

|

отсутствует. |

|||||

|

|

log2(512Кб / 32б) = 14 бит. |

||||

|

|

|

||||

•Физический факультет, ЭВУ и системы, 7 семестр,2013 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2013 Dr. Mokhovikov

|

|

|

|

Строка кэша |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Блок данных |

тег |

индекс |

|

смещение |

бит |

|

|

|

актуальности |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Каждая строка в каком-либо сегменте имеет свой постоянный номер, который не

подлежит изменению.

Если имеется N сегментов кэш-памяти, => N строк кэш-памяти с одинаковым индексом. Увеличение размера строки при неизменном размере сегмента приведёт к уменьшению

размера индекса, а также и к уменьшению их количества вследствие уменьшения числа строк.

В то же время увеличение размера строки приводит к увеличению задержек при

загрузке/выгрузке строк из других уровней кэш-памяти или RAM.

К тому же, больший размер строки ухудшает эффективность кэш-памяти вследствие

большей степени её засорения ненужной информацией.

Среднее время доступа к кэшу можно определить следующим образом: tср = tобр + Рпр * tпр, где tобр - время обращения при попадании;

tпр - потери времени при промахе; Рпр– вероятность промаха.

•Физический факультет, ЭВУ и системы, 7 семестр,2013 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2013 Dr. Mokhovikov

Кэш-память: Размер строки, тэга и индекса

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.Как правило, поля данных защищаются либо |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

1.Ко всему прочему, каждая строка кэш-памяти |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

проверкой чётности (parity checking) на уровне |

|

||||||||

|

|

обычно обладает некоторой избыточной |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

отдельных байт, либо одним из протоколов |

|

||||||||

|

|

информацией для надлежащего контроля за |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

проверки и коррекции ошибок (ECC — Error |

|

||||||||

|

|

ошибками. |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

Checking and Correcting) на уровне целого поля, |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

большинство из которых основывается на |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

алгоритме Хэмминга (the Hamming algorithm). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3.Тэги могут защищаться однобитовой |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

проверкой чётности, хотя эта практика |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

распространена в значительно меньшей |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

степени, чем защита полей данных. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.Тем не менее, какой бы из алгоритмов защиты |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

информации ни был выбран, его обслуживающая |

|

||||

|

|

|

|

|

|

|

|

|

|

|

логика привнесёт сложности в существующую |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

разработку и неминуемо отразится на задержках при |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

5.Если точнее, то при каждой операции |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

работе. |

|

|||||||

|

|

|

|

|

чтения контрольная сумма поля данных |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

должна быть сосчитана и сверена с |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

сохранённой. Наиболее тяжёлым является |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

случай частичной записи в |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

действительную строку, т.к. контрольная |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

сумма должна быть сосчитана дважды: до и |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

после изменения строки. |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

•Физический факультет, ЭВУ и системы, 7 семестр,2013 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2013 Dr. Mokhovikov

Уровни кэша

Кэш центрального процессора разделён на несколько уровней. В универсальном процессоре в настоящее время число уровней может достигать 3.

Кэш-память уровня N+1 как правило больше по размеру и медленнее по скорости доступа и передаче данных, чем кэшпамять уровня N.

Самой быстрой памятью является кэш первого уровня — L1-cache. По сути, она является неотъемлемой частью процессора, поскольку расположена на одном с ним кристалле и входит в состав функциональных блоков.

В современных процессорах обычно кэш L1 разделен на два кэша: кэш команд (инструкций) и кэш данных (в соответствии с Гарвардской архитектурой)

•Физический факультет, ЭВУ и системы, 7 семестр,2013 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2013 Dr. Mokhovikov

L1 Cache

Большинство процессоров без L1 кэша не могут функционировать.

L1 кэш работает на частоте процессора, и, в общем случае, обращение к нему может производиться каждый такт.

Зачастую является возможным выполнять несколько операций чтения/записи одновременно.

Латентность доступа обычно равна 2−4 тактам ядра, т.е. время доступа для выполнения элементарных операций.

Объём обычно невелик — не более 128 Кбайт.

•Физический факультет, ЭВУ и системы, 7 семестр,2013 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2013 Dr. Mokhovikov

Cache L2

Вторым по быстродействию является L2-cache — кэш второго уровня, обычно он расположен на кристалле, как и L1.

В старых процессорах — набор микросхем на системной плате. Объём L2 кэша от 128 Кбайт до 1−12 Мбайт.

В современных многоядерных процессорах кэш второго уровня, находясь на том же кристалле, является памятью раздельного пользования — при общем объёме кэша в nM Мбайт на каждое ядро приходится по nM/nC Мбайта, где nC количество ядер процессора.

Обычно латентность L2 кэша, расположенного на кристалле ядра, составляет от 8 до 20 тактов ядра.

•Физический факультет, ЭВУ и системы, 7 семестр,2013 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2013 Dr. Mokhovikov

Cache L3

Кэш третьего уровня наименее быстродействующий, но он может быть очень внушительного размера — более 24 Мбайт. L3 кэш медленнее предыдущих кэшей, но всё равно значительно быстрее, чем оперативная память.

В многопроцессорных системах находится в общем пользовании и предназначен для синхронизации данных различных L2.

Иногда существует и 4 уровень кэша, обыкновенно он расположен в отдельной микросхеме. Применение кэша 4 уровня оправдано только для высоко производительных серверов и мейнфреймов.

•Физический факультет, ЭВУ и системы, 7 семестр,2013 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2013 Dr. Mokhovikov

Уровни кэша

Проблема синхронизации между различными кэшами (как одного, так и множества процессоров) решается когерентностью кэша.

Существует 3 варианта обмена информацией между кэш-памятью различных уровней

инклюзивный |

эксклюзивный |

неэксклюзивный |

Инклюзивная архитектура предполагает дублирование информации кэша верхнего уровня в нижнем

Эксклюзивная кэш-память предполагает уникальность информации, находящейся в различных уровнях кэша

Неэксклюзивный

кэш может вести

себя как угодно.

•Физический факультет, ЭВУ и системы, 7 семестр,2013 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2013 Dr. Mokhovikov