- •Учебное пособие по дисциплине: «Прикладная электроника» Северск, сгти - 2003

- •Предисловие

- •1 Импульсная и цифровая техника

- •1.1 Общие сведения

- •1.2 Ключевой режим работы биполярных транзисторов

- •1.3 Импульсный режим работы операционных усилителей. Компараторы. Триггер Шмитта

- •1.4 Позиционные системы счисления

- •1.5 Функции алгебры логики и их основные свойства

- •1.5.1 Основные определения

- •1.6 Элементарные функции алгебры логики

- •1.7 Аналитическая запись функций алгебры логики

- •1.8 Аксиомы, основные теоремы и тождества алгебры логики

- •1.9 Минимизация функций алгебры логики

- •1.9.1 Основные определения

- •1.9.2 Постановка задачи минимизации в классе днф

- •1.9.3 Аналитическая минимизация

- •4.9.4 Метод неопределенных коэффициентов и минимизирующих карт

- •1.9.5 Метод минимизирующих карт

- •1.9.6 Карты Карно

- •2 Цифровые интегральные схемы

- •2.1 Логические элементы

- •2.1.1 Логический элемент не

- •2.1.2 Логический элемент или

- •2.1.3 Логический элемент и

- •2.1.4 Логический элемент или - не

- •2.1.5 Логический элемент и - не

- •2.2 Классификация

- •2.3 Основные характеристики и параметры лэ

- •2.3.1 Сравнение обобщенных параметров цифровых микросхем

- •2.3.2 Типовые корпуса микросхем

- •2.4 Элементы с памятью (триггеры, счетчики)

- •2.4.1 Триггеры сR,Sуправлением

- •2.4.2 Триггеры с синхронным управлением

- •2.4.3 Триггеры сJk-управлением

- •2.4.4 Триггеры сD-управлением

- •2.4.5 Разное

- •3 Вопросы анализа и синтеза невременных схем

- •3.1 Логические сети

- •3.2 Теорема анализа и эквивалентные схемы

- •3.3 Синтез логических схем с одним выходом

- •3.4 Синтез логических схем со многими выходами

- •3.5 Синтез схем по неполностью определенным собственным функциям

- •3.6 Пример синтеза устройства - преобразователя кодов

- •4 Синтез и анализ схем, работа которых зависит от времени

- •4.1 Временные булевы функции. Основные определения

- •4.2 Основные свойства временных булевых функций

- •4.3 Синтез и анализ схем с помощью временных булевых функций

- •5 Схемотехника элементов интегрального исполнения

- •5.1 Схемотехника элементов серий ттл

- •5.1.1 Основные принципы построения схем

- •5.1.2 Основные параметры и характеристики серий ттл

- •5.1.3 Функциональный состав ттл ис и ттлш ис

- •5.2 Схемотехника элементов серий кмоп

- •5.2.1 Инвертор на комплиментарной моп-паре

- •5.2.2 Основные логические элементы и-не, или-не,z

- •5.2.3 Функциональный состав кмоп ис

- •5.2.4 Основные характеристики ис к564

- •5.2.4.1 Энергетические характеристики

- •5.2.4.2 Передаточные характеристики

- •5.2.4.3 Помехоустойчивость

- •5.2.4.4 Быстродействие

- •5.2.4.5 Напряжение питания

- •5.2.4.6 Входные характеристики

- •5.2.4.7 Нагрузочная способность

- •5.2.4.8 Надежность ис к564

- •5.2.5 Основные характеристики ис cерии кр1554

- •5.2.5.1 Технические характеристики

- •5.2.5.3 Предельные электрические режимы эксплуатации микросхем серии кр1554

- •5.2.5.4 Функциональный состав микросхем серии кр1554

2.4.4 Триггеры сD-управлением

Наиболее часто в цифровых интегральных микросхемах, а также в импульсных устройствах применяют триггеры с единственным входом данных D(data), так называемыеD-триггеры.

Одна из причин их появления была в том,

что число выводов у корпусов микросхем

ранних разработок не превышало 14, а

стоимость многовыводного корпуса

составляла значительную часть от

стоимости готовой микросхемы. Для

D-триггера требуется всего

четыре внешних вывода: вход данныхD,

тактовый вход С, два выходаQи

![]() (один из них может отсутствовать). СхемаD-триггера (рис. 2.34,а)

отличается от схемыRST-триггера

(рис. 2.29,б) наличием инвертораDD1.1,

добавленного между входамиSиR. Теперь состояние

неопределенности для входовRиSисключается, так как

инверторDD1.1 формирует

на входеRсигнал

(один из них может отсутствовать). СхемаD-триггера (рис. 2.34,а)

отличается от схемыRST-триггера

(рис. 2.29,б) наличием инвертораDD1.1,

добавленного между входамиSиR. Теперь состояние

неопределенности для входовRиSисключается, так как

инверторDD1.1 формирует

на входеRсигнал![]() .

.

Рис. 2.34 - Триггер со входом D

Согласно таблице логических состояний

D-триггера (рис. 2.34,б)

в некоторый момент времениtnна входDможно подать

напряжения низкого или высокого уровня.

Если в последующий моментtn+1придет положительный перепад тактового

импульса, состояния на выходахQn+1и![]() будут соответствовать табл. 2.34,б.

будут соответствовать табл. 2.34,б.

На рис. 2.34, в показаны диаграммы записи вD-триггер напряжений высокого и низкого входных уровней и их считывание. Непременное условие правильной работыD-триггера — это наличие защитного интервала времени после прихода запускающего импульсаUDперед тактовымUC (интервал времениtn+1-tn оговаривается справочными данными наD-триггер).

Рисунок 2.35 - Счетчик-делитель на 2: а - структурная схема;б - применениеD-триггера для деления на 2

Если снабдить D-триггер

цепью обратной связи, соединяющей выход![]() со входомD, он станет

работать как Т-триггер, т. е. делитель

частоты в 2 раза (счетчик). Действительно,

нетрудно видеть, что делитель на рис.

2.35,апо фазировке сигналов соответствует

Т-триггерному, рассмотренному на рис.

2.30,а. На рис. 2.35,бпоказаны

осциллограммы работы делителя на два

частоты тактовой последовательностиUC.

со входомD, он станет

работать как Т-триггер, т. е. делитель

частоты в 2 раза (счетчик). Действительно,

нетрудно видеть, что делитель на рис.

2.35,апо фазировке сигналов соответствует

Т-триггерному, рассмотренному на рис.

2.30,а. На рис. 2.35,бпоказаны

осциллограммы работы делителя на два

частоты тактовой последовательностиUC.

а - изRSв Т;б- изDв Т;е— изJKв Т;г — Т-триггер со входом разрешения Е1;д - JKвD;е - RSTвD;ж-RSTвJK

Рисунок 2.36 - Схемы взаимного преобразования триггеров

2.4.5 Разное

В заключение рассмотрим несколько схем взаимного преобразования триггеров.

На рис. 2.36,а—впоказаны схемы делителей частоты наRST-,D- иJK-триггерах соответственно. ТриггерDможно преобразовать в Т (делитель на 2), снабдив делитель дополнительным входом разрешенияEI(рис 2.36,г). В режимеD-триггера можно использоватьJK-иRST-триггеры (рис. 2.36,д,е). ИзRST-триггера можно получитьJK-триггер по схеме (рис 2.36,ж)

3 Вопросы анализа и синтеза невременных схем

3.1 Логические сети

При математическом описании тех или иных физических объектов, как правило, отвлекаются от целого ряда второстепенных факторов и процессов, действующих в этих физических объектах. Такая абстракция необходима для создания общей математической теории для целого класса родственных между собой физических процессов.

Целью настоящей главы является разработка методов и способов анализа и синтеза физических устройств, предназначенных для переработки дискретной информации.

Мы будем изучать не сами эти устройства, а некоторым образом адекватные им математические схемы. Эта адекватность выражается в том, что работа обеих схем (физической, реально действующей и математической абстрактной) описывается с помощью одних и тех же математических соотношений.

Такую адекватную математическую схему мы будем называть логической сетью.

Дадим более четкое определение понятия логической сети. Пусть мы имеем конечное множество А:

![]()

И пусть нам задано множество В, элементами которого являются упорядоченные пары элементов множестваА:

![]()

Здесь i,j— любые из элементов множестваA, i≠j. Пусть, наконец, нам задано некоторое множествоF, элементами которого являются логические функции

![]()

Установим однозначное соответствие между множествами F иA, т. е. сопоставим каждому элементу множестваА один из элементов множестваF.

Определение. Совокупность множеств А и В совместно с однозначным отображением множества F на множество А называется логической сетью.

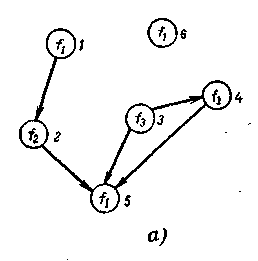

Определенное таким образом понятие логической сети совпадает с понятием ориентированного нагруженного графа. Геометрической интерпретацией логической сети служит некоторая схема логической сети, которая строится следующим образом. На плоскости в произвольном порядке располагаются элементы множества А. (Для их обозначения будем использовать кружок). Эти элементы называются вершинами графа (рис. 3-1,a).

Рис. 3-1.

Символ соответствующего данному кружку элемента i (т.е. номер) пишется справа от этого кружка. Внутри кружка вписывается элемент множестваF, сопоставленный при отображенииF на А элементу, соответствующему данному кружку. Наконец, все кружки соединяются между собой ориентированными стрелками согласно элементам множестваВ. Элементу (i, j)соответствует стрелка, идущая от кружка, сопоставленного элементуi, к кружку, сопоставленному элементуj. Эти стрелки носят название ребер графа.

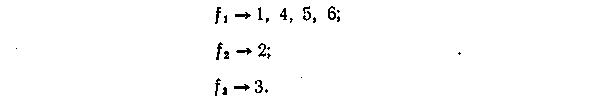

Пример 1. Пусть

и отображение F наА задано как

Соответствующая схема заданной логической сети показана на рис. 3-1,а.

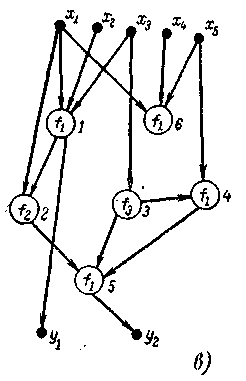

Введем в рассмотрение множество аргументов

![]()

Произведем теперь отображение некоторых подмножеств множества X на некоторые элементы множестваА

![]()

где X* некоторое подмножество множестваX. При геометрической интерпретации элементы множестваX будем изображать жирными точками и называть входами схемы логической сети. Задание отображения подмножестваX* на элементыai эквивалентно заданию множества С следующего вида:

![]()

Геометрической интерпретацией множества С являются ребра, проведенные из соответствующих входов схемы к вершинам графа, сопоставленным нужным элементам множества А.

Пример 2. Для логической сети на рис. 3-1,азаданы:

Соответствующая схема логической сети приведена на рис. 3-1 ,б.

Потребуем теперь, чтобы элементы множества В обладали тем свойством, что для всякого элемента (i,j) i<j. Подобную логическую сеть назовем упорядоченной или логической сетью без обратных связей.

Теперь ограничим отображение множества F наА следующим образом. Потребуем, чтобы функцияfj,, сопоставляемая вершине с номеромi, зависела бы от стольких аргументов, сколько ребер входит в данную вершину. Эквивалентным требованием является ограничение на элементы множествВ и С при заданном отображенииF наА. Суммарное число пар вида (i,j) и(xi, j) не должно превышать числа аргументов, имеющихся у функции, сопоставленной вершине с номеромj. Логическую сеть, для которой выполнено это требование, назовем правильной.

Определение. Упорядоченная и правильная логическая сеть называется регулярной логической сетью (РЛС).

В дальнейшем будем рассматривать только правильные логические сети, а на протяжении этого раздела ограничимся рассмотрением только регулярных логических сетей. Рассмотрим, наконец, множество выходов

![]()

Произведем теперь взаимно однозначное отображение некоторого подмножества А* множестваА на множествоY. Для возможности такого отображения, очевидно, необходимо выполнение неравенстваk≤ m*, гдеm* — число элементовА*. Геометрической интерпретацией этого отображения будут ребра, направленные от элементов множестваА* к соответствующим элементам множестваY. Элементы множестваY, как и элементы множестваX, будем обозначать жирными точками.

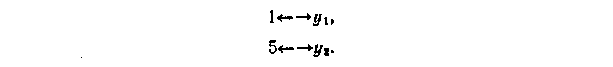

Пример 3. Для логической сети рис. 3-1,б определено множество

![]()

и взаимно однозначное отображение

Соответствующая схема логической сети приведена на рис. 3-1,в.

После отображения некоторых вершин графа на множество Y в графе могут остаться вершины, из которых не выходит ни одно ребро. Такие вершины назовем тупиковыми и исключим их, а также ребра, идущие к ним. Оставшуюся после этого схему логической сети будем называть логическим многополюсником. Если множествоXсодержитпэлементов, а множество У —kэлементов, то такой логический многополюсник будем называть логическим (п, k) - полюсником.

Пример 4. Для регулярной логической схемы, данной на рис. 3-1,в, вершина 6 является тупиковой. После ее удаления остается логический (5,2)-полюсник, входх4у которого является фиктивным, и поэтому он опущен на схеме логической сети (рис. 3-1,г).

Теория логических сетей включает в себя целый ряд различных разделов. В этих разделах изучаются вопросы, связанные с поисками методов эффективного преобразования информации, оптимальным кодированием, геометрией сетей, проблемами надежности сети и т. д. Из всего множества этих проблем мы рассмотрим только проблемы, связанные с анализом и синтезом логической сети.