[irt.od.ua]КонспектАПСПК / КонспектАПСПК

.pdf

|

|

|

│INTA# |

│ INT |

|

|

|

|

v |

^ |

|

┌────────┐ |

|

┌───┴──────────┴────┐ |

|||

D7..D0 │ Буфер |

│ |

║ |

│ Схема управления │ |

||

════════╡ шины |

╞═══╣ |

└─┬───┬──────┬──────┘ |

|||

│ данных │ ┌───────┘ v |

^ |

|

|||

└────────┘ │ ╠═════╦═══│══════│══╦═══ |

|||||

┌────────┐ │ ║ |

┌─╨───┴──┐ ┌─┴──╨───┐ |

||||

RD#────>┤ Логич. ├─┤ ║ |

│ Регистр│ │ Регистр├<──IRQ0 |

||||

WR#────>┤ схема |

│ │ ║ |

│ обслу- │ │запросов├<──IRQ1 |

|||

А0────>┤ чтение/│ │ ║ |

│ женных │ │ преры- ├<── ... |

||||

CS#────>┤ запись │ │ ║ |

│запросов│ │ вания |

├<──IRQ7 |

|||

└────────┘ │ ║ |

└───┬────┘ └───┬────┘ |

||||

┌────────┐ │ ║ |

^ |

^ |

|

||

CАS0<──>┤ Буферн.├─┘ ║ |

┌───┴──────────┴────┐ |

||||

CАS1<──>┤ схема |

│ |

╠═══╡ Схема маскирования│ |

|||

CАS2<──>┤ каскади- |

║ |

│ запросов и анализа│ |

|||

DE# ──>┤ рования│ |

|

│ их по приоритету |

│ |

||

└────────┘ |

|

└───────────────────┘ |

|||

Рис. 9.3. Структура 8259

Байты СКО2 и СКО3 записываются в порт 20h. СКО2 (А0=0, D4=0, D3=0) указывает вид установки дна и дно приоритетного кольца, а также вид конца прерывания. Например, в конце программы прерывания, как правило, заносится число 20h в порт 20h:

MOV AL, 20h

OUT 20h, AL

Это означает нормальный конец прерывания для 8259 и переход на обслуживание других входов IRQ.

Контрольные вопросы

1.Возможно ли функционирование ПЭВМ без прерываний?

2.Дайте классификацию типов прерываний.

3.Как организована система прерываний?

4.Приведите описание контроллера прерываний.

5.Зачем в программе прерывания в порт 20h заносится число 20h?

41

Лекция 10. Компоненты системной платы – сопроцессор, порты и таймер

10.1. Математический сопроцессор 8087

Микросхема 8087 представляет собой 80-битовый арифметический сопроцессор (FPU) и может быть использован только совместно с процессором 8086/88, так как в нем отсутствует механизм выборки команд. Сопроцессор предназначен для повышения производительности CPU до 100 раз при выполнении операций с многоразрядными целыми и вещественными числами.

Схема соединения 8088 и 8087 представлена на рис. 10.1.

┌─────────────────┐ |

|

┌─────────────────┐ |

|||

│ 8088 |

А8..А19╞═════════════╡ А8..А19 |

8087 │ |

|||

│ |

АD0..АD7╞═════════════╡ АD0..АD7 |

│ |

|||

│ |

RESET, |

│ |

|

│ RESET, |

│ |

│ |

READY,CLK╞═════════════╡ READY,CLK |

│ |

|||

│ |

S0..S2 |

╞═════════════╡ S0..S2 |

│ |

||

│ |

QS1,QS2 |

╞═════════════╡ QS1,QS2 |

│ |

||

│ |

S7 |

├─34───────34─┤ S7/BHE# |

│ |

||

│ |

RQ#/GT0#├─31 |

|

33─┤RQ#/GT1# |

│ |

|

│ |

RQ#/GT1#├─30───────31─┤RQ#/GT0# |

│ |

|||

│ |

NMI ├──<─схема──<─┤ INT |

│ |

|||

│ |

|

│ |

|

│ |

│ |

│ |

MN/MX#,GND├──────┬──────┤ GND |

│ |

|||

│ |

|

│ |

┴ |

│ |

│ |

│ |

TEST#├─23─<─┬───23─┤BUSY# |

│ |

|||

│ |

Ucc │ |

┌┴┐ |

│ Ucc |

│ |

|

└─────────────┬───┘ |

│ │ |

└───┬─────────────┘ |

|||

|

│ |

|

└┬┘ |

│ |

|

+5V────┴──────────┴──────────┘

Рис. 10.1. Схема соединения 8088 и 8087

Взаимодействие процессоров начинается по сигналу RESET (>4 тактов CLK). 8087 проверяет уровень сигнала на выводе 34. CPU 8086 формирует 0, а 8088 - 1. Таким образом, устанавливается тип МП. Кроме того, в процессорах запоминается значение сигнала на входе 23 (TEST#=BUSY#=1).

Далее CPU производит выборку команд из памяти, а сопроцессор следит за его работой, находись в пассивном режиме: как и 8088, принимает все команды в очередь и анализирует состояние очереди CPU QS1,QS0. Если QS1,QS0=01 (первый байт) и код команды равен 11011= ESC (префикс команды сопроцессора), 8087 переходит в активный режим, установив сигнал BUSY# =0. CPU и сопроцессор теперь работают параллельно. При этом процессоры "договариваются" по линии RQ#/GT1# (8088) – RQ#/GT0# (8087) о праве пользования локальной шиной. Это достигается путем двухсторонней передачи/приема нулевых импульсов с длительностью одного периода CLK. Процессор, которому требуется шина, передает сигнал запроса. Другой процессор, заканчивает цикл шины (если таковой был), отключается от шины и передает в ответ импульс разрешения на ее использование. Окончив цикл шины, первый процессор выдает сигнал ее освобождения RELEASE.

После выполнения своей команды сопроцессор устанавливает сигнал BUSY#=1 и переходит в пассивный режим.

42

10.2. Параллельный периферийный интерфейс

Параллельный периферийный интерфейс (PPI) выполнен на контроллере 8255. PPI формирует внутренние порты в диапазоне адресов 60…7F, имеющие следующее назначение.

Порт A используется для чтения данных с клавиатуры. Порт B выдает поразрядно сигналы управления:

PB0, PB1 - TIMSPK, SPKDATE - управление звуком; PB2 – вкл./выкл. Turbo режима; PB3 - чтения старшего (=1), либо младшего (=0) полубайта системного переключателя; PB4, PB5 – ERAMPCK#, ENIOCLK# - сброс маски NMI и запроса внешнего устройства IOCHCK#; PB6 =0 - сброс флагов клавиатуры; PB7 - 0/1 - разрешение чтения скан-кода клавиатуры/ снятие запроса на прерывание IRQ1.

Порт C принимает: PC0…PC3 - состояние системных переключателей; PC4 - SPK - сигнал с динамика; PC5 - T/C_ZOOT - сигнал звукового канала таймера; PC6 - сигнал IOCHCK c системной шины; PC7 - PCK - признак ошибки памяти по контролю четности.

Системные переключатели по номерам контактов дают следующие установки.

0 – имеется/отсутствует накопитель на диске;

1 – имеется/отсутствует математический сопроцессор;

3,2 - объем ROM-BIOS: 00 - 16K; 01 - 32K; 10 - 48K; 11 - 64K;

5,4 - тип видеоадаптера 00 - EGA; 01 - CGА-40; 10 - CGА-80; 11 - MDA; 7,6 - число накопителей на диске (1..4): 00 -> 1... 11 -> 4.

Функциональная схема чтения состояния системного переключателя и данных с клавиатуры приведена на рис. 10.2.

|

┌─────────────┬<──┐ PB3 |

PB6 |

┌─────┐ |

|||||

|

│ сист.перекл.╞═╗ │┌───────────────>─┤ Key ├─<──KB_CLOCK |

|||||||

|

└─────────────┘ ║ ││ |

|

|

└──┬──┘ |

||||

║ BX |

┌──┬───────┬──┐ ║ ││ |

┌─────────┐ |

┌──v──┐ |

|||||

║ |

│ |

│ PPI |

│ |

│ ║ ││ |

│ИР28 |

CLK├<┬─┤ ЛЗ |

│ |

|

╠═════╡ |

D│ |

│PC╞═╣ ││ |

│ |

│ │ ├─────┤ |

||||

║ |

│ |

│ |

│ |

│ ║ ││ |

│ |

│ └>┤ T |

│ |

|

╠═════╡ |

А│ |

│ |

│ ││PB7│ |

OH#├─>─┤ |

├─┬─> IRQ1 |

|||

║ |

│ |

│ |

│PB╞═══╧╧─┬>┤OE# |

│ |

└──^──┘ │ |

|||

|

│WR#,RD# |

│ |

│ |

│ │ |

G# ├<─────│────┘ |

|||

══════╡ RESET |

│ |

│ |

│ │ |

│ |

│PB7 |

|||

PPICS──┤CS# |

│PA╞════════╡D |

8 DI├<─────────────KB_DATE |

||||||

|

└──┴───────┴──┘ |

│ └─────────┘ |

│ |

|

||||

|

|

|

|

|

└──────────────────┘ |

|

||

Рис. 10.2. Схема чтения данных с клавиатуры

Чтение данных с клавиатуры происходит следующим образом.

В исходном состоянии PB6=1 (нет сброса по линии KB_CLOCK) и PB7=0 (разрешение выхода регистра ИР28).

При нажатии или отпускании клавиши в контроллере клавиатуры для PC/XT формируется однобайтовый скэн-код. Старший бит означает нажатие

(1) или отпускание (0) клавиши. Остальные 7 бит соответствуют номеру нажа-

43

той клавиши. Далее код побитно передается в компьютер по линии KB_DATE. Одновременно с каждым битом передаются нулевые стробы (им- пульсы-защелки) по линии KB_CLOCK, которые через ключ Key и линию задержки ЛЗ (около 1 мкс) поступают на тактовый вход CLK последовательнопараллельного регистра ИР28 (ИР24). В этот регистр последовательно загружаются биты данных KB_DATE. По прошествии восьми тактов на выходе – OH# появляется нулевой импульс, который защелкивается в триггере T. Положительный выходной сигнал триггера является запросом на прерывание IRQ1, которое поступает на контроллер PIC. Одновременно по входу G# запрещается прием битов в ИР28. Программа прерывания читает скан-код из порта A, а затем, передав единичный импульс по линии PB7, сбрасывает запрос на прерывание IQR1 и содержание регистра ИР28. Далее CPU сообщает контроллеру PIC о том, что запрос снят, анализирует скан-код и преобразует его в ASCII-код символа. Статус клавиши и ее код помещается в буфер памяти (до 15 значений) в области данных BIOS. После выхода из программы прерывания компьютер готов к приему следующего байта с клавиатуры.

10.3. Периферийный интегральный таймер

Периферийный интегральный таймер PIT содержит 3 канала и предназначен для формирования опорных временных интервалов и частот для часов реального времени (канал 0, порт 40h), регенерации ОЗУ (канал 1, порт 41h) и сигналов динамика (канал 2, порт 42h). Имеется также порт 43h для записи слов, задающих режимы работы каналов. Структурная схема окружения тай- мера-счетчика представлена на рис. 10.3.

2.38МГц |

1.1931817МГц |

|

|

|

|

||

┌─────┐PCLK ┌─────┐ TIMCLK ┌──────┐ |

|

|

|

||||

│ 8284├─────┤ ТМ8 ├────────┤C |

PPI│OUT0 |

55мС |

IRQ0 |

||||

│ : 6 │ |

│ : 2 │ |

T/CCS#┤ 8253├────────────────────── |

|||||

└──╥──┘ |

└─────┘ XА0,XА1┤ |

/54│ |

|

|

|

||

┌──╨──┐ |

┌─────┐ |

│ |

│OUT1┌────┐15мкС DRQ0 |

||||

│Кварц│ |

│ 8288├─XIOR#──┤R# |

├────┤ За-├──────────── |

|||||

└─────┘ |

│ |

├─XIOW#──┤W# |

│ |

│щел-│ |

|

||

14.31818МГц |

└─────┘ |

│ |

│ |

│ £А │ |

|

||

|

┌─────┐ TIMSPK │ |

│ |

└────┘ |

|

|||

|

│ 8255├────────┤S2 |

│OUT2┌────┐ |

/│ |

||||

|

│ |

│ |

│ |

├────┤Вен-├───┤│ │ Звук |

|||

BS |

└─────┘ |

│ |

│ |

│тиль│ |

\│ |

||

║┌─────┐XD0..XD7│ │ └──┬─┘

╠══════╡Буфер╞════════╡D |

│ |

│ |

||

║ |

└─────┘ |

└──────┘ |

SPKRDATA |

|

Рис.10.3. Схема окружения таймера

Основу таймера-счетчика составляет 3-канальный программируемый интервальный таймер 8253 (в XT) или 8254 (в AT). Таймеры аналогичны по функциональным возможностям и отличаются максимальной тактовой частотой (2 Мгц для 8253 и 8 Мгц для 8254 ).

В компьютере IBM каналы 0 и 1 настраиваются на режим 2. В этом режиме сигнал опорной частоты TIMCLK делится в n раз, где n – двухбайтовое число,

44

загруженное в счетчик. Выходной сигнал представляет собой нулевые импульсы длительностью одного периода опорной частоты. К примеру, при старте BIOS в порт 43h заносится управляющее слово 54h = 01010100, означающее, что канал 1 будет находится в режиме 2 и коэффициент деления задается младшим байтом (старший равен 0) в двоичном коде. Затем после тестирования первого канала таймера 8253 в него окончательно записывают код 12h, обеспечивающий период выходных импульсов первого канала 15 мкс. Это период регенерация памяти динамического ОЗУ.

Контрольные вопросы

1.Что дает применение математического сопроцессора?

2.Почему сопроцессор не может функционировать отдельно от CPU?

3.Каковы назначения портов параллельного периферийного интерфейса?

4.Опишите процесс чтения данных с клавиатуры.

5.Каково функциональное назначение интегрального таймера?

45

Лекция 11. Система прямого доступа в память

11.1. Организация прямого доступа в память

Если использовать центральный процессор 8088/86 для передачи данных внешнее устройство – память, то для этого потребуется около 40 процессорных тактов.

Режим прямого доступа в память (ПДП) обеспечивает передачу за 4 такта, резко увеличивая быстродействие всей системы. Возможен также обмен типа "память-память", что реализовано в AT. Процесс ПДП обеспечивается аппаратно с помощью контроллеров DMA без участия микропроцессора. В компьютерах IBM PC/XT используется БИС 8237, которая содержит 4 независимых 8-битовых канала данных с 16-битовой адресацией. При этом старший байт защелкивается на внешнем регистре ИР22. Кроме того, имеется дополнительный так называемый страничный регистр 4х4 бит ИР26, в котором фиксируются старшие разряды А16..А19 20-битового адреса.

Канал 0, имеющий наивысший приоритет, обеспечивает регенерацию динамической памяти. Канал 1 свободен и может применяться для нужд пользователя. Каналы 2 и 3 поддерживают обмен с накопителями, соответственно, на гибких и жестких дисках.

Структурная схема процесса ПДП представлена на рис 11.1.

┌─────────┐ |

┌───────┐ |

||

│ |

CPU ╞═BA════════════╦═════════════════════╡ |

RAM │ |

|

│ |

╞═BD════════════║═════════════════╦═══╡ |

│ |

|

│╞═BC══════╦═════║══════════════╦══║═══╡-WR │

└─┬───┬─┬─┘ |

IOW# ║ А16 ║ |

┌───┐ |

║ |

║ |

│-RD |

│ |

||

^ |

│ │ |

MEMR#║..А19╠═══╡RG2│ |

║ |

║ |

│ |

│ |

||

│ |

│ │ |

IOR# ║ А8..║ |

├───┤ |

IOW#║ |

║ |

└───────┘ |

||

READY# |

│ │ |

MEMW#║ |

А15╠═══╡RG1│ |

IOR#║ |

║ |

|

|

|

│ |

│ │ |

┌─╨─────╨─┐ └─┬─┘ |

┌─v──╨─┐ |

|

|

|||

┌─┴─┐ |

│ │ |

│ |

|

├>─ADSTB |

│ |

│ |

|

|

│ ЛС│ |

│ └─<HRQDMA#┤ |

DMA |

├<──DRQi───┤DEVICE│ |

|

|

|||

└─┬─┘ └───>HOLDA#─┤ |

|

├>──DACKi──┤ |

│ |

|

|

|||

└───────<AEN#───┤ |

|

├>──T/C────┤ |

│ |

|

|

|||

|

|

│ |

|

├<──RDYDMA─┤ |

│ |

|

|

|

└─────────┘ └──────┘

Рис 11.1. Структурная схема процесса ПДП

Циклы ПДП выполняются для последовательно расположенных ячеек RAM. Для осуществления ПДП контроллер DMA выполняет такую последовательность операций:

1)Принимает запрос DRQi по i входу на ПДП от DEVICE, либо получает команду от CPU на выполнение ПДП.

2)Формирует запрос HRQDMА# на то, чтобы CPU перешел в состояние захвата шин ( шины А, D и C CPU переводятся в Z-состояние ).

3)Принимает сигнал HLDA# подтверждения захвата шин центральным процессором.

46

4)Формирует сигнал пользования шиной AEN=1, который в логической схеме ЛС преобразуется в сигнал приостановки CPU –READY#.

5)С помощью сигналов DACKi и T/C=0 информирует внешнее устройство о начале выполнения циклов ПДП.

6)Ожидает состояние готовности RDYDMA# от внешнего устройства.

7)Выполняет цикл шины. В первом такте на шине DB0..DB7 устанавливается старший байт адреса А8..А15, который защелкивается на внешнем регистре RG1 сигналом ADSTB. Во втором такте устанавливается адрес ячейки памяти RAM: А0..А7 на выходах DMА, А8..А15 из регистра RG1 и А16..А19 из страничного регистра RG2, который загружается на этапе программирования ПДП. Далее DMA вырабатывает сигналы MEMR#,IOW# или MEMW#, IOR# для управления обменом внешнее устройство-память, либо памятьпамять. В третьем такте состояние шин не изменяется, а в четвертом такте снимаются сигналы управления.

8)По окончании ПДП либо, изменив адрес, DMA повторяет цикл по п.п. 6, 7, либо прекращает обмен. В последнем случае DMA отключается от шин, снимает сигналы AEN и приостановки центрального процессора READY#, а также вырабатывает признак конца ПДП T/C=1.

Подготовка к ПДП состоит в записи адресов в страничные регистры и программировании соответствующих каналов контроллера DMA.

Страничные регистры доступны через порты 81h - канал 2, 82h -

канал 3 и 83h - канал 1. Страничный регистр канала 0 не используется. Далее рассматривается построение и программирование контроллера DMA.

11.2.Контроллер DMA 8237

Контроллер предназначен для ПДП по 4-м независимым каналам с положительным или отрицательным приращением адреса и с объемом передачи до 64К циклов. Один цикл ПДП в обычном режиме выполняется за 4 такта CLK микропроцессора, что для PC/XT составляет 1.5 Мбайт/с. Имеется возможность удвоения скорости обмена, а также увеличения числа каналов путем каскадирования контроллеров. В системах AT и старше используются два контроллера и, соответственно, 7 каналов ПДП.

Регистры и команды контроллера ПДП

Каждый канал контроллера содержит 4 16-разрядных регистра.

Регистр текущего адреса CAR (current address register) хранит текущее значение адреса ячейки памяти в цикле ПДП, которое увеличивается или уменьшается на единицу после выполнения цикла.

Регистр циклов ПДП CWR (current word register) хранит число слов, предназначенных для передачи, плюс единица.

Регистры хранения базового адреса BAR и базового числа циклов ПДП WCR. Данные в эти регистры записываются только при начальной загрузке.

47

Регистры для чтения недоступны. Каждый канал имеет также 6-разрядный регистр MR режима работы DMA.

Контроллер содержит один 8-разрядный регистр TR временного хранения данных при передаче память-память. Такая передача требует осуществляется с помощью каналов 0 и 1. PC/XT передача память-память невозможна, поскольку канал 0 занят регенерацией ОЗУ.

В контроллере содержится блок управления, вырабатывающий сигналы управления в циклах ПДП. Блок включает в себя два 8-разрядных (CR и SR), а также два 4-разрядных регистра (RR и MASK).

Режимы работы контроллера ПДП

Контроллер имеет два основных режима: пассивный при работе с CPU и активный при выполнении циклов ПДП. В пассивном режиме производится программирование контроллера (в частности, его инициализация), а также анализ состояния его регистров. Контроллер может быть запрограммирован на одиночную передачу, блочную передачу, передачу по требованию, а также на режим "память-память". При этом возможны три типа передачи: запись данных в ОЗУ, чтение данных из ОЗУ и псевдопередача ("проверка"). Кроме того, имеется несколько дополнительных функций: автоинициализация, обслуживание по заданным приоритетам или с их циклическим изменением и операция "сжатие во времени". В последнем случае выполняется двухтактный цикл шины благодаря формированию адреса старших разрядов только при его изменении.

BIOS при старте в регистры ПДП посылает следующие данные. 0 в порт 83h - обнуление страничного регистра канала 1.

4 в порт 08h - запрет ПДП.

12h в порт 0Dh - общий сброс (регистр команд в 0, регистр масок - в FFh). FFFFh в порты 0 и 1 - загрузка для канала 0 младшего + старшего байта в

регистры BAR и CAR (порт 0), а также в регистры WCR и CWR (порт 1). 58h в порт 0Bh - канал 0, чтение, автоинициализация, отрицательное при-

ращение адреса, одиночная передача.

0 в порт 0Аh - снять маску ПДП для канала 0.

Таким образом, программируется 0-й канал ПДП на регенерацию памяти.

Контрольные вопросы

1.Может ли функционировать компьютер без прямого доступа в память?

2.Что дает применение ПДП?

3.Опишите процесс прямого доступа в память.

4.Каково назначение контроллера DMA.

5.Как программируется контроллер DMA?

48

Часть 3. Развитие архитектуры стандарта PC

Лекция 12-13. Структура и режимы работы современного процессора. Системные технологии кэширования и Plug & Play

12.1. Требования к современным процессорам

В обобщенном виде центральный процессор представляется так:

Core |

|

L0 |

|

L1 |

|

L2 |

|

IO |

|

Mem |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Port |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 12.1. Обобщенная структура одноядерного процессора

Пользователь ожидает от процессора следующие характеристики.

1.Высокое быстродействие – количество инструкций в единицу времени. Эта характеристика достигается повышением тактовой частоты и распараллеливанием вычислений. Повышение тактовой частоты ограничивается предельно допустимым тепловыделением. Современные системы отвода тепла ограничены величиной 150-200 Вт и имеют высокую стоимость. При этом неизбежно возрастают рабочие температуры и резко снижается надежность системы. Известно, что при повышении температуры на 15 градусов время наработки на отказ уменьшается вдвое. В кристаллах на основании кремния вряд ли возможна тактовая частота свыше 10 ГГц.

Распараллеливание вычислений достигается суперскалярной архитектурой, т.е. многоконвейерной обработкой. Например, одноядерные процессоры Core 2 и Athlon содержат 3-4 конвейера, что позволяет выполнять до 8 инструкций одновременно. Дополнительная возможность распараллеливания появляется при многоядерной архитектуре. Так, при двух ядрах производительность процессора увеличивается в 1.3-1.8 раз.

2.Снижение тепловыделения. В мире функционируют сотни миллионов компьютеров, каждый из которых потребляет сотни ватт. Это составляет значительную часть общего энергопотребления. Современные процессоры расходуют до 130 Вт. Intel и AMD ограничивают мощность настольных процессоров величиной 65 Вт. Мощность на процессоре пропорциональна частоте и квадрату напряжения питания: P=αFU2. При этом, уменьшая технологический шаг, можно уменьшить как потери по частоте, так и рабочее напряжение на процессоре. В 2006-м году начато освоение технологического шага 45 нм при питании ядра 1.2-1.4 В. Уменьшение технологического шага происходит по закону Мура. Разрабатываются технологии 22 нм. Возможно, будет снижение технологического шага до 6 нм (размер атома кремния 3 нм). Дополни-

49

тельной проблемой тепловыделения является ток утечки. Его снижение дает технология SOI (кремний на изоляторе), которая используется в CPU AMD.

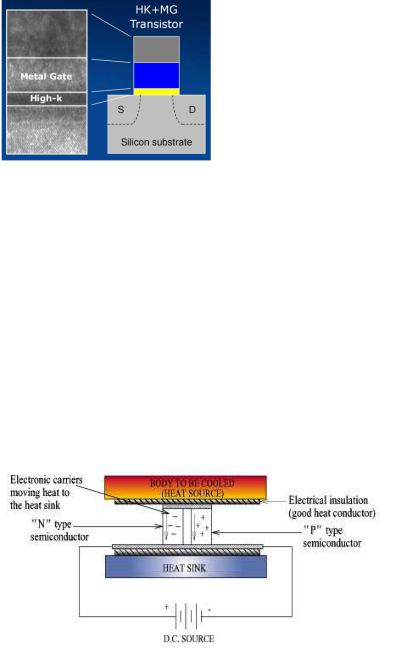

Рис. 12.2. Технология High-K (диэлектрик на основе

гафния с высоким коэффициентом диэлектрической проницаемости – hi-k, металлический затвор)

Intel в каждом транзисторе заменила два слоя (показаны на иллюстрации синим и жёлтым) другими материалами. Жёлтый слой диэлектрика,

влияющий на скорость переключения между истоком и стоком MOSFET, раньше состоял из диоксида кремния, а теперь его заменил диэлектрик High- K. Кроме того, бывший слой кремния в затворе над диэлектриком (синий) теперь стал металлическим. При этом токи утечки снизились в 10 раз.

Переход на более тонкий технологический процесс также снижает тепловыделение и повышает быстродействие из-за уменьшения емкости затвора. Так, переход с 65 нм на 45 нм уменьшает пепловыделение на 30%. Кроме этого уменьшается площадь кристалла в 2 раза.

Проблемы отвода тепла в ПЭВМ. Конвекция и излучение. Алюминий и медь. Пассивное и принудительное охлаждение. Радиаторы: материал, площадь, ребра (шаг). Тепловые трубки. Вентиляторы (форма лопасти, направление потока) и шум. Воздушное, жидкостное, криогенное (фреон, сухой лед, жидкий азот) и полупроводниковое охлаждение.

Рис. 12.3. Элемент Пельтье

КПД у элемента Пельтье ниже 10%. Основная задача таких элементов – получение температур ниже температуры окружающей среды.

3. Снижение стоимости. Этот процесс происходит по закону Мура вследствие массового потребления и законов конкуренции. Так, в 1997 году процессор Pentium 166 MMX стоил около 100 долларов. В 2006 году по этой стоимости продавался двуядерный процессор Pentium D 805, который в 30 раз быстрее. Правда, энергопотребление при этом также выросло почти на порядок.

50