- •Основные подсистемы компьютера

- •На подсистему возлагается задача обеспечения выполнения следующих видов операций передачи данных.

- •Основные компоненты компьютера

- •СВЯЗЬ МЕЖДУ КОМПОНЕНТАМИ ЧЕРЕЗ МАГИСТРАЛЬ

- •Структура магистрали

- •Типовой набор управляющих сигналов следующий:

- •Типовой набор управляющих сигналов следующий:

- •Функционирует магистраль следующим образом

- •Иерархия магистралей

- •Структура компьютерной системы с несколькими магистралями: а

- •Функциональные характеристики конструкции магистрали

- •Типы магистралей

- •Арбитраж магистрали

- •Синхронизация

- •Временная диаграмма операции чтения: а — синхронная магистраль; б — асинхронная магистраль

- •Разрядность магистрали

- •Виды операций передачи данных

- •Магистраль PCI

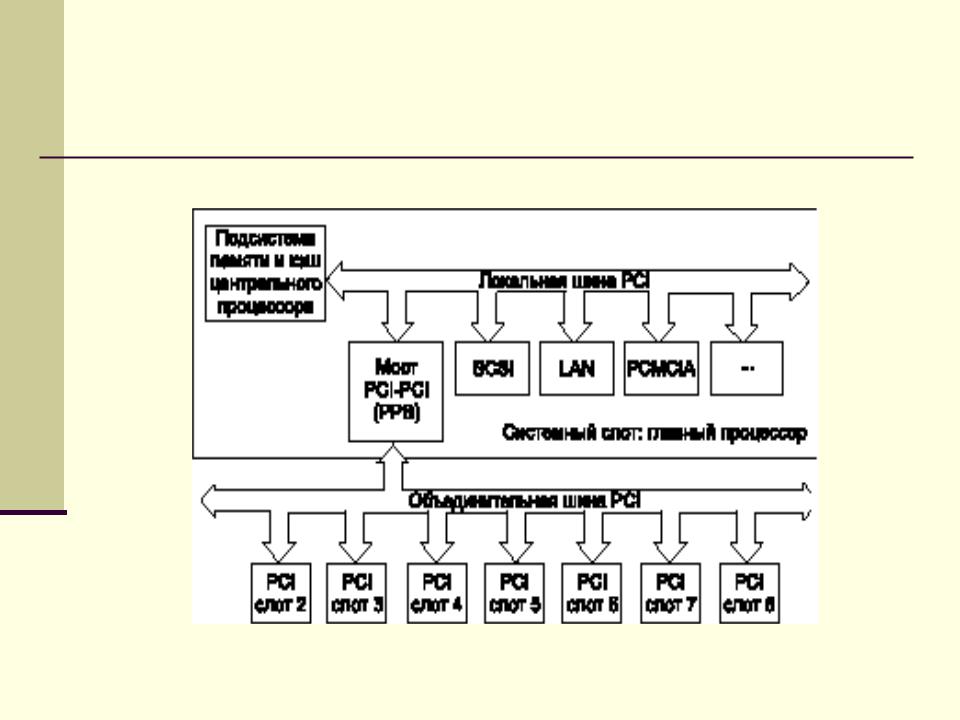

- •Конфигурации компьютерных систем на базе магистрали PCI: a

- •Конфигурации компьютерных систем на базе

- •СТРУКТУРА ЛИНИЙ МАГИСТРАЛИ

- •Основные линии магистрали PCI.

- •Основные линии магистрали PCI

- •Основные линии магистрали PCI

- •Основные линии магистрали PCI

- •Необязательные линии

- •Интерпретация команд чтения магистрали PCI.

- •Синхронный обмен по шине PCI.

- •Сеанс передачи данных.

- •Асинхронный обмен по шине PCI.

- •Сеанс передачи данных

- •Арбитраж магистрали.

- •Работа арбитра

- •Работа арбитра

- •Базовая конфигурация шины PCI или CompactPCI реализует пользовательский интерфейс и сетевую часть системы

- •В базовой PCI архитектуре процессор вырабатывает синхросигналы на локальную шину PCI через мост

- •В базовой CompactPCI архитектуре определяются как "прозрачные", или "стандартные"

- •При использовании прозрачных мостов РРВ в слот 1 стандартной архитектуры системы CompactPCI обычно

- •При ассиметричной мультиобработке с использованием на интеллектуальной плате ввода/вывода встроенного "непрозрачного" моста РРВ,

- •Рекомендуемая схема соединений линий прерывания на объединительной плате и их связь с линиями

- •Если системный контроллер желает уведомить интеллектуальную плату ввода/вывода о том, что он зопомнил

Сеанс передачи данных

С5. В начале такта CLK 4 задатчик считывает данные и при необходимости изменяет код на линиях C/BE , подготавливаясь к следующей фазе передачи данных.

С6. При выполнении этой операции исполнителю нужно некоторое время на подготовку

передачи второго блока данных. Поэтому он снимает сигнал с линии TRDY и дает знать задатчику, что он не успевает выставить данные к началу следующего такта и нужно немного подождать. Поэтому задатчик в следующем , пятом ,такте не считывает код с линий AD и не меняет код на линиях C/BE. Данные считываются только в начале шестого такта, когда исполнитель вновь выставит сигнал на линии TRDY.

С7. Во время такта CLK 6 исполнитель выставляет на линии AD третий элемент данных , но задатчик не готов его прочесть ( например, оказалось, что его внутренний буфер уже заполнен и требуется некоторое время на его освобождение). В таком случае задатчик снимает сигнал с линии IRDY, а исполнитель не меняет выставленный на линии AD код данных и удерживает его в течение еще одного такта.

С8. Задатчику известно, что третий элемент данных является последним, а потому он снимает сигнал с линии FRAME. Это служит для исполнителя сигналом, что больше не нужно обращаться за новыми данными. Задатчик также устанавливает сигнал на линии IRDY , извещая, что он готов считать текущий элемент данных и завершить сеанс.

С9. Задатчик завершает чтение последнего элемента и снимает сигнал с линии IRDY, а исполнитель снимает сигналы с линий TRDY и DEVSEL.

Арбитраж магистрали.

Арбитр |

GNT# |

GNT# |

GNT# |

GNT# |

|

магистрали |

|||||

REQ# |

REQ# |

REQ# |

REQ# |

||

|

|||||

|

Контроллер |

Контроллер |

Контроллер |

Контроллер |

|

|

устройства |

устройства |

устройства |

устройства |

|

Рисунок 2. Подключение арбитра магистрали PCI к устройству. |

|

||||

Работа арбитра

С1. Еще до начала 1-го такта устройство А выставляет сигнал запроса захвата магистрали на свою линию REQ-A ( сигналв на линии REQ выставляются низким уровнем). Арбитр считывает этот сигнал по переднему фронту тактового импульса CLK 1.

С2. В середине первого такта устройство В также выставляет сигнал запроса на свою линию REQ-B.

С3. Примерно в то же время- а именно, по заднему фронту тактового импульса CLK 1 - арбитр выставляет сигнал низкого уровня на линию GNT-А, подключенную к устройству А, предоставляя ему право контроля над магистралью.

С4. Устройство А считывает сигнал GNT-A по переднему фронту тактового импульса CLK 2 и узнает, что оно получило статус задатчика транзакции. Одновременно устройство А анализирует состояние линий IRDY и TRDY и вясняет, что на них сигналы отсутствуют, т.е. магистраль не занята (находится в состоянии простоя). Получив от арбитра право контроля над магистралью и выяснив, что она свободна, задатчик начинает транзакцию. Он выставляет сигнал на линию FRAME

, код адреса начального элемента передаваемой порции данных - на линии AD и код команды - на линии C/BE (на временной диаграмме эта группа линий не показана). Обратите внимание - свой сигнал запроса REQ-A устройство А не снимает , поскольку планирует сразу после этой транзакции выполнить еще одну.

Работа арбитра

С5. По переднему фронту тактового импульса CLK 3 арбитр анализирует все подключенные к нему линии REQ и обнаруживает , что устройство В также выставило запрос. Предположим, что арбитр реализует такой алгоритм принятия решения, который в данной ситуации позволяет предоставить устройству В право контроля над магистралью для выполнения следующей транзакции. Поэтому арбитр снимает сигнал с линии GNT - А и выставляет сигнал на линию GNT - B . Это означает, что как только магистраль освободится , устройство В получит статус задатчика.

С6. Устройство А снимает сигнал с линии FRAME и тем самым дает знать , что начинается последняя фаза передачи данных текущей транзакции ( в данном случае транзакция включает всего одну фазу передачи данных). Одновременно оно выставляет данные на линии AD и сигнал на линию IRDY . Исполнитель считывает данные по переднему фронту следующего тактового импульса.

С7. В начале 5 такта устройство В обнаруживает , что сигналы на линиях IRDY и FRAME отсутствуют и , следовательно, магистраль свободна. Теперь это устройство получает статус задатчика и выставляет свой сигнал на линию FRAME , а сигнал с линии REQ- B снимает, поскольку планирует выполнить только одну транзакцию.

В дальнейшем устройство А снова получит статус задатчика для выполнения следующей транзакции, поскольку оно не сняло сигнал со своей линии REQ.

Базовая конфигурация шины PCI или CompactPCI реализует пользовательский интерфейс и сетевую часть системы из системного контроллера и дополнительных модулей ввода/вывода, обеспечивающих дополнительную обработку в реальном масштабе времени

В базовой PCI архитектуре процессор вырабатывает синхросигналы на локальную шину PCI через мост процессор-PCI

В базовой CompactPCI архитектуре определяются как "прозрачные", или "стандартные"

При использовании прозрачных мостов РРВ в слот 1 стандартной архитектуры системы CompactPCI обычно вставляется плата системного контроллера, а интеллектуальные платы ввода/вывода вставляются в слоты, начиная со второго

При ассиметричной мультиобработке с использованием на интеллектуальной плате ввода/вывода встроенного "непрозрачного" моста РРВ, диапазон конфигурации локальных процессоров ограничивается встроенным мостом, и поиск устройств на объединительной шине PCI не производится

Рекомендуемая схема соединений линий прерывания на объединительной плате и их связь с линиями прерывания индивидуальных слотов подразумевает, что линия INTA системного слота соединяется с линией INTB слота 2, линией INTC слота 3, линией INTD слота 4, линией INTA слота 5 и т.д.