- •Основные подсистемы компьютера

- •Концепции фон Неймана

- •Реализация вычислительного процесса.

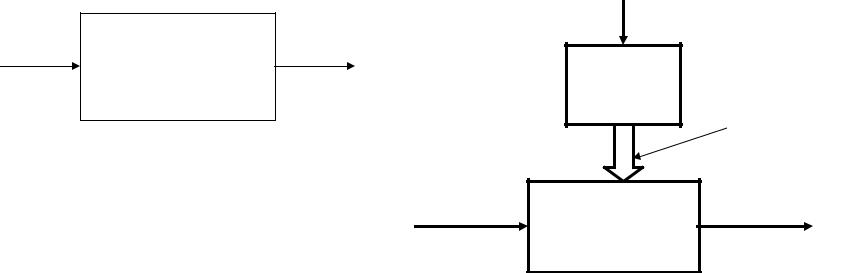

- •Блок схема основных компонентов

- •Схема основного цикла обработки команды

- •Элементарные действия, которые выполняет процессор:

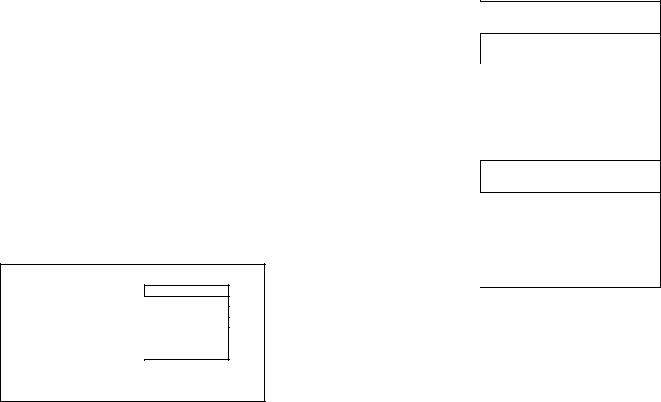

- •Формат команд и данных гипотетического

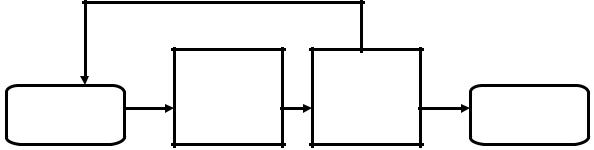

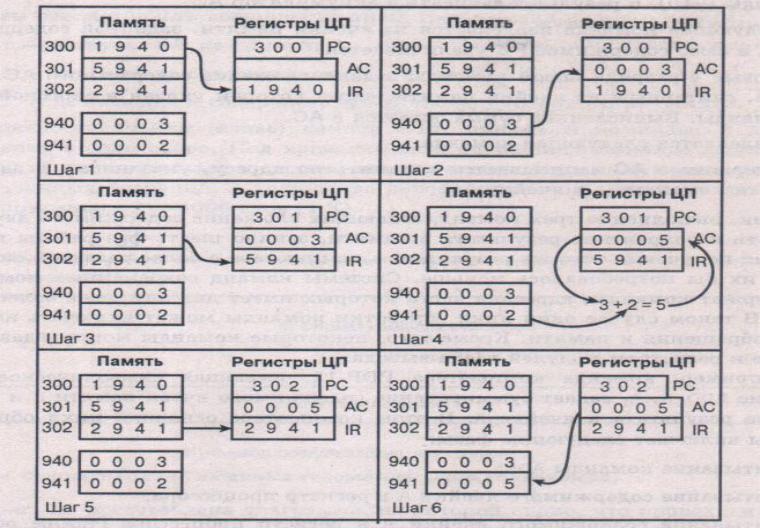

- •Диаграмма выполнения фрагмента программы гипотетического компьютера

- ••Вычисления адреса команды (IAC — Instruction Address Calculation). При естественном порядке выполнения команд

- •Укрупненная диаграмма состояний основного цикла

- •Основные компоненты компьютера

- •СВЯЗЬ МЕЖДУ КОМПОНЕНТАМИ ЧЕРЕЗ МАГИСТРАЛЬ

- •Структура линий системной магистрали

- •Типовой набор управляющих сигналов :

- •Функции магистрали

- •Структура компьютерной системы с несколькими магистралями: а — традиционная; б — обладающая повышенной

- •Функциональные характеристики конструкции магистрали

- •Характеристика

- •Временная диаграмма операции чтения: а — синхронная магистраль; б — асинхронная магистраль

- •Виды операций передачи данных по

- •Магистраль PCI

- •Конфигурации компьютерных систем на базе магистрали PCI:

- •Конфигурации компьютерных систем на базе магистрали PCI:

- •СТРУКТУРА ЛИНИЙ МАГИСТРАЛИ

- •Системные линии

- •Информационные линии

- •Линии управления интерфейсом

- •Линии арбитража

- •Асинхронный обмен по шине PCI.

- •Синхронный обмен по шине PCI.

- •Линии индикации ошибок

- •Необязательные линии

Основные подсистемы компьютера

Оперативная

память

|

|

|

|

|

|

|

|

Процессор |

|

Кэш/Согласователь |

|

|

|

|

|

|

|

Системная шина |

|||||

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Интерфейс |

|

Интерфейс |

|

Графическая |

|

Видеокарта |

|

Модуль ЛВС |

|

||||||||||

SCSI |

|

FireWire |

|

|

карта |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Высокоскоростная шина

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Интерфейс |

|

|

|

|

|

Последовательный канал |

||||

|

Факс |

||||||||||||||

|

|

расширения |

|

|

|

|

|

|

|

|

|||||

|

|

|

Модем |

|

|

|

|

||||||||

|

|

|

|

|

шины |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Расширение шины

Концепции фон Неймана

•данные и команды хранятся совместно в единой подсистеме памяти, способной выполнять операции чтения и записи;

•к отдельным элементам информации, хранящейся в памяти, можно обратиться по адресу;

•заданный алгоритм решения задачи реализуется последовательным выполнением элементарных команд в порядке их расположения в памяти.

Реализация вычислительного процесса.

• Система с жесткой логикой |

• Программное управление |

Результат

Данные Последовательность

логических и арифметических

преобразований

Интерпретат

ор

команд

Данные

Универсальный

модуль

выполнения арифметических и логических операций

Управляющ ие сигналы

Результат

Блок схема основных компонентов

компьютера

|

|

ЦП |

||

|

|

|

|

|

|

|

|

|

|

|

PC |

|

MAP |

|

|

|

|

|

|

|

|

|

|

|

|

IR |

|

MBR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O AR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O BR |

|

|

|

|

|

|

|

|

|

|

|

Модуль ввода/вывода

…

Буферы

Оперативная память

…

Команды

Команды

Команды

…

Данные

Данные

Данные

…

Условные обозначения:

PC- счетчик команд программы IR - регистр команд

MAR - регистр адреса в памяти

MBR- регистр данных памяти

I/O AR - регистр адреса устройства ввода/вывода I/O BR- регистр данны ввода/вывода

Схема основного цикла обработки команды

Фаза |

Фаза выполнения |

извлечения |

|

|

Извлечение |

Выполнени |

|

следующей |

е команды |

ПУСК |

команды |

СТОП |

Элементарные действия, которые выполняет процессор:

1.передача "процессор — память": данные передаются из процессора в память или из памяти в процессор;

2.передача "процессор — модуль ввода-вывода": данные передаются из процессора в один из модулей ввода-вывода или наоборот;

3.обработка данных: процессор выполняет заданную арифметическую или логическую операцию над данными;

4. управление: команда изменяет естественный порядок выполнения команд программы.

Формат команд и данных гипотетического

компьютера

0 |

3 |

4 |

15 |

|

|

|

|

Код операции |

|

|

Адрес |

|

|

|

|

0 |

|

1 |

Формат команды |

|

|

15 |

|||

|

|

|

|

|

|

|

|

|

|

|

S |

|

|

Абсолютная величина |

|

|

|

|

|

Формат представления целого числа

Диаграмма выполнения фрагмента программы гипотетического компьютера

•Вычисления адреса команды (IAC — Instruction Address Calculation). При естественном порядке выполнения команд программы адрес следующей команды образуется в результате прибавления константы к адресу текущей команды.

•Извлечение команды (IF — Instruction Fetch). Считывание команды из ячейки памяти по адресу, заданному в PC, в регистр процессора.

•Расшифровка кода операции (IOD —Instruction Operation Decoding). Анализ кода операции и выяснение типа затребованной операции, количества и типов участвующих в ней операндов (или операнда).

•Вычисления адреса операнда (ОАС — Operand Address Calculation). Если в операции используются операнды, хранящиеся в памяти или передаваемые через подсистему ввода-вывода, то на этой фазе определяются их "физические" адреса.

•Извлечение операнда (OF — Operand Fetch). Считывание операнда из заданной ячейки памяти или из модуля ввода- вывода.

•Обработка данных (DO — Data Operation). Выполнение операции, предусмотренной кодом операции.

•Сохранение результата (OS — Operand Store). Запись результата операции в заданную ячейку памяти или передача в модуль ввода-вывода.

Укрупненная диаграмма состояний основного цикла

обработки команды