- •Конспект лекций по курсу "аналоговая схемотехника"

- •Конспект лекций по курсу "аналоговая схемотехника"

- •1. Аналоговые ключи и коммутаторы

- •1.1. Ключ на полевом транзисторе с управляющим p-n - переходом

- •1.2. Аналоговые ключи на кмоп – транзисторах

- •1.3. Диодный коммутатор

- •1.4. Мультиплексоры аналоговых сигналов

- •1.5. Аналоговые коммутаторы на базе операционного усилителя

- •1.6. Контрольные вопросы

- •2. Компараторы сигналов

- •2.1. Простейшие компараторы

- •2.2. Компаратор с пос (триггер Шмидта)

- •2.3. Ограничение выходного напряжения

- •2.4. Компаратор с окном

- •2.5. Интегральные схемы компараторов

- •2.6. Контрольные вопросы

- •3. Схемы для измерительных систем

- •3.1. Схемы выборки - хранения

- •3.2. Точный выпрямитель

- •3.3. Увеличение выходного тока оу

- •3.4. Источники тока на оу

- •3.5. Источник тока на интегральной микросхеме lm117

- •3.6. Контрольные вопросы

- •4. Источники питания

- •4.1. Структурная схема источника питания

- •4.2. Стабилизаторы напряжения

- •4.3. Параметрические стабилизаторы

- •Контрольные вопросы

- •5. Компенсационные стабилизаторы с непрерывным регулированием

- •5.1. Общие положения

- •5.2. Работа компенсационного стабилизатора непрерывного действия

- •5.3. Составной транзистор

- •5.4. Расчет компенсационного стабилизатора напряжений непрерывного действия

- •5.5. Ограничение выходного тока стабилизатора

- •5.6. Контрольные вопросы

- •6. Схемы стабилизаторов компенсационного типа на интегральных схемах

- •6.1. Трехвыводные схемы стабилизаторов

- •6.2. Увеличение выходного тока стабилизатора.

- •6.3. Некоторые схемы стабилизаторов на интегральных схемах

- •Контрольные вопросы

- •Модуль № 2

- •7. Импульсные стабилизаторы

- •7.1. Общие положения

- •7.2. Вторичные импульсные стабилизаторы

- •7.3. Понижающий импульсный стабилизатор

- •7.4. Повышающий импульсный стабилизатор

- •7.5. Первичные импульсные стабилизаторы

- •7.6. Контрольные вопросы

- •8. Цифро-аналоговые преобразователи

- •8.1. Классификация цап

- •8.2. Последовательный цап с широтно-импульсной модуляцией

- •8.3. Последовательный цап на переключаемых конденсаторах

- •8.5. Цап на основе матрицы типа r – 2r

- •8.6. Построение цап с электронными ключами

- •8.7. Интерфейсы цап

- •8.8. Цап с последовательным интерфейсом входных данных

- •8.9. Цап с параллельным интерфейсом входных данных

- •Контрольные вопросы

- •9. Аналого-цифровые преобразователи

- •9.1. Общие сведения

- •9.2. Параллельные ацп

- •9.3. Последовательно – параллельный ацп

- •9.4. Ацп последовательного приближения

- •Интегрирующий ацп

- •9.6. Преобразователь напряжения - частота

- •9.7. Контрольные вопросы

- •10. Интерфейсы ацп

- •10.1. Способы организации ввода данных ацп в вычислительных системах

- •10.2. Ацп с параллельным интерфейсом выходных данных

- •10.3. Ацп с последовательным интерфейсом выходных данных

- •10.4. Системы ввода аналоговых сигналов и микроконверторы

- •10.5. Контрольные вопросы

- •11. Генераторы сигналов на оу

- •11.2. Генераторы колебаний прямоугольной формы

- •11.2. Генератор сигналов треугольной формы

- •11.3. Генератор синусоидальных сигналов с мостом Вина

- •11.4. Контрольные вопросы

- •Список использованной литературы

Интегрирующий ацп

Недостатком рассмотренных выше последовательных АЦП является низкая помехоустойчивость результатов преобразования. Действительно, выборка мгновенного значения входного напряжения, обычно включает слагаемое в виде мгновенного значения помехи. Впоследствии при цифровой обработке последовательности выборок эта составляющая может быть подавлена, однако на это требуется время и вычислительные ресурсы. В АЦП, рассмотренных ниже, входной сигнал интегрируется либо непрерывно, либо на определенном временном интервале, длительность которого обычно выбирается кратной периоду помехи. Это позволяет во многих случаях подавить помеху еще на этапе преобразования. Платой за это является пониженное быстродействие интегрирующих АЦП. Структурная схема АЦП двухтактного интегрирования приведена на рис.9.6.

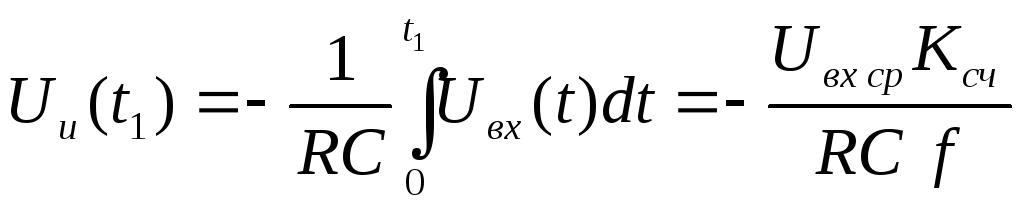

Преобразование проходит две стадии: стадию интегрирования и стадию счета. В начале первой стадии ключ S1замкнут, а ключ S2разомкнут. Интегратор И интегрирует входное напряжение Uвх. Время интегрирования входного напряжения t1постоянно; в качестве таймера используется счетчик с коэффициентом пересчета Kсч, так что

t1=Kсч /f.

К моменту окончания интегрирования

выходное напряжение интегратора

составляет

,

,

где Uвх.ср.- среднее за время t1входное напряжение. После окончания стадии интегрирования ключ S1размыкается, а ключ S2замыкается и опорное напряжение Uоппоступает на вход интегратора. При этом выбирается опорное напряжение, противоположное по знаку входному напряжению. На стадии счета выходное напряжение интегратора линейно уменьшается по абсолютной величине, как показано на рис.9.7.

Стадия счета заканчивается, когда выходное напряжение интегратора переходит через нуль. При этом компаратор К переключается и счет останавливается. Интервал времени, в котором проходит стадия счета, определяется уравнением

.

.

Подставив в это уравнение значение Uи(t1) с учетом того, что

![]() ,

,

где n2- содержимое счетчика после окончания стадии счета, получим результат

![]() .

.

Из этой формулы следует, что отличительной особенностью метода многотактного интегрирования является то, что ни тактовая частота, ни постоянная интегрирования RC не влияют на результат. Необходимо только потребовать, чтобы тактовая частота в течение времени t1+t2оставалась постоянной. Это можно обеспечить при использовании простого тактового генератора, поскольку существенные временные или температурные дрейфы частоты происходят за время несопоставимо большее, чем время преобразования.

В окончательный результат входят не мгновенные значения преобразуемого напряжения, а только значения, усредненные за время t1. Поэтому переменное напряжение ослабляется тем сильнее, чем выше его частота.

9.6. Преобразователь напряжения - частота

На базе преобразователей напряжение-частота (ПНЧ) могут быть построены интегрирующие АЦП, обеспечивающие относительно высокую точность преобразования при низкой стоимости. Существует несколько видов ПНЧ. Наибольшее применение нашли ПНЧ с заданной длительностью выходного импульса. Структурная схема такого ПНЧ приведена на рис.9.8. По этой схеме построена ИМС VFC-32 (отечественный аналог - 1108ПП1).

Р аботает

ПНЧ следующим образом. Под действием

положительного входного сигнала Uвхнапряжение Uина выходе интегратора

И уменьшается. При этом ключ S разомкнут.

Когда напряжение Uиуменьшится

до нуля, компаратор К переключается,

запуская тем самым одновибратор.

Одновибратор формирует импульс стабильной

длительности Ти, который управляет

ключем. Последовательность этих импульсов

является выходным сигналом ПНЧ. Ключ

замыкается и ток Iопв течение Типоступает на вход интегратора, вызывая

увеличение выходного напряжения

интегратора. Далее описанный процесс

снова повторяется.

аботает

ПНЧ следующим образом. Под действием

положительного входного сигнала Uвхнапряжение Uина выходе интегратора

И уменьшается. При этом ключ S разомкнут.

Когда напряжение Uиуменьшится

до нуля, компаратор К переключается,

запуская тем самым одновибратор.

Одновибратор формирует импульс стабильной

длительности Ти, который управляет

ключем. Последовательность этих импульсов

является выходным сигналом ПНЧ. Ключ

замыкается и ток Iопв течение Типоступает на вход интегратора, вызывая

увеличение выходного напряжения

интегратора. Далее описанный процесс

снова повторяется.

Импульсы тока Iопуравновешивают ток, вызываемый входным напряжением Uвх. В установившемся режиме

![]()

Отсюда следует

![]() ,

,

г де

Uвх.ср- среднее значение входного

напряжения за период Т. Это выражение

показывает, что точность преобразования

определяется точностью установки

опорного тока Iоп, точностью

выдержки длительности импульса

одновибратора Ти, а также точностью

резистора R. Емкость конденсатора

интегратора не оказывает влияния на

частоту ПНЧ.

де

Uвх.ср- среднее значение входного

напряжения за период Т. Это выражение

показывает, что точность преобразования

определяется точностью установки

опорного тока Iоп, точностью

выдержки длительности импульса

одновибратора Ти, а также точностью

резистора R. Емкость конденсатора

интегратора не оказывает влияния на

частоту ПНЧ.

Таким образом, по существу ПНЧ преобразует входное напряжение в унитарный код. Для его преобразования в двоичный позиционный можно использовать счетчик. Схема интегрирующего АЦП на базе ПНЧ приведена на рис.9.9. Двоичный счетчик подсчитывает число импульсов, поступивших от ПНЧ за период Тотсч=1/fотсч, задаваемый отсчетными импульсами, которыми содержимое счетчика заносится в выходной регистр-защелку. Вслед за этим происходит обнуление счетчика. Число импульсов n, подсчитанных счетчиком за время Тотсч,

![]()

Здесь Uвх.ср- среднее значение входного напряжения за весь период Тотсч.

Можно заметно повысить точность ПНЧ, если вместо одновибратора включить тактируемый импульсами стабильной частоты D-триггер.