Микропроцессорная техника / Семейство микроконтроллеров MSP430x2xx_

.pdf

352Глава 14. Универсальный последовательный интерфейс

Вкачестве источника тактового сигнала модуля USI могут использоваться системные тактовые сигналы ACLK или SMCLK, внешний сигнал синхрониза ции SCLK или же выходной сигнал любого из блоков захвата/сравнения Таймера А. Кроме того, тактовый сигнал модуля может формироваться програм мно с помощью бита USISWCLK при USISELx = 100.

Биты USIDIVx определяют коэффициент деления (от 2 до 128, кратный сте пени двойки) тактового сигнала. Формирование тактового сигнала USICLK пре кращается при USIIFG = 1 или же при работе модуля в режиме ведомого.

Бит USICKPL используется для выбора полярности сигнала USICLK. При USICKPL = 0 неактивному состоянию сигнала USICLK соответствует ВЫСО КИЙ уровень, а при USICKPL = 1 — НИЗКИЙ уровень.

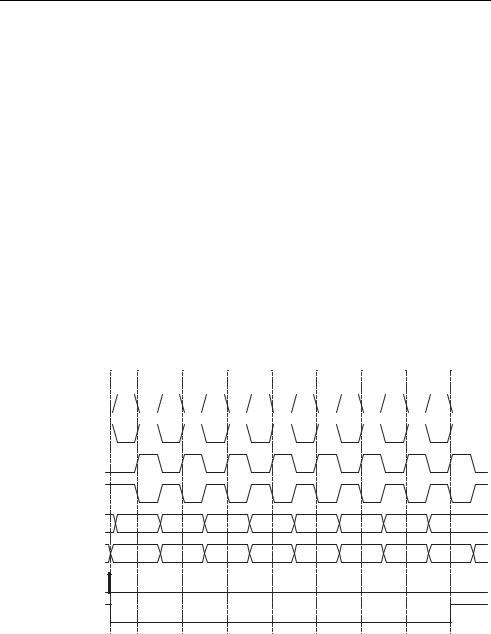

14.2.3. Режим SPI

Модуль USI переключается в режим SPI при USII2C = 0. Бит USICKPL опре деляет неактивный уровень тактового сигнала SPI, в то время как бит USICKPH определяет фронт тактового сигнала, по которому будет выставляться сигнал на вывод SDO и считываться состояние вывода SDI. Временные диаграммы для всех возможных вариантов режима SPI (8 битные данные, MSB передаётся первым) приведены на Рис. 14.3. Для активации линий SCLK, SDO и SDI порта должны быть установлены биты USIPE5, USIPE6 и USIPE7.

USI |

USI |

USICNTx0 8 |

7 |

6 |

5 |

4 |

3 |

|

2 |

1 |

0 |

||||||||||||||||||||||||

CKPH CKPL |

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

SCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 1 SCLK

1 0 SCLK

1 1 SCLK

0 |

X |

SDO/SDI |

MSB |

LSB |

1 |

X |

SDO/SDI |

MSB |

LSB |

|

Загрузка USICNTx |

|

|

|

|

|

USIIFG |

|

|

Рис. 14.3. Временные диаграммы для режима SPI.

Режим ведущего SPI

Модуль USI переводится в режим ведущего SPI установкой бита режима веду щего USIMST с одновременным сбросом бита USII2C, отвечающим за включе ние режима I2C. Поскольку ведущее устройство генерирует тактовый сигнал для ведомых, необходимо также выбрать соответствующий источник тактового сиг

14.2. Функционирование модуля USI 353

нала и сконфигурировать вывод SCLK в качестве выхода. При USIPE5 = 1 вывод SCLK конфигурируется в качестве выхода автоматически.

При USIIFG = 0 и USICNTx > 0 разрешается генерация тактового сигнала и ведущий начинает принимать/передавать данные с использованием регистра USISR.

Полученные данные необходимо считать из сдвигового регистра до того, как в него будут загружены новые передаваемые данные. Как правило, программа счи тывает полученные данные из сдвигового регистра USISR, загружает в него но вые данные и разрешает их передачу, загружая в USICNTx число битов передава емого слова.

Режим ведомого SPI

Модуль USI переводится в режим ведомого SPI сбросом битов USIMST и USII2C. В этом режиме при USIPE5 = 1 вывод SCLK автоматически конфигури руется как вход, и модуль USI принимает тактовый сигнал от ведущего устройства.

Если модулю требуется передать данные, то их необходимо загрузить в сдви говый регистр до появления первого фронта тактового сигнала, генерируемого ведущим. Выход модуля должен быть разрешён установкой бита USIOE. При USICKPH = 1 старший бит передаваемого слова данных появится на выводе SDO сразу же после загрузки слова в сдвиговый регистр.

Вывод SDO может быть отключён сбросом бита USIOE. Эта возможность ис пользуется неадресованными ведомыми при наличии на шине нескольких ведо мых устройств.

После того как все биты будут приняты, полученные данные необходимо счи тать из сдвигового регистра USISR, а новые данные загрузить в него до появления следующего фронта тактового сигнала от ведущего устройства. Обычно после приёма очередного слова данных программа считывает содержимое регистра USISR, загружает в него новые данные и разрешает модулю передачу новых дан ных, загружая в USICNTx число битов передаваемого слова.

Сдвиговый регистр USISR

16 битный сдвиговый регистр USISR образован из двух 8 битных регистров USISRL и USISRH. Число битов регистра USISR, используемых для приёма и пе редачи данных, определяется битом USI16B. При USI16B = 0 используются толь ко 8 младших битов, USISRL.

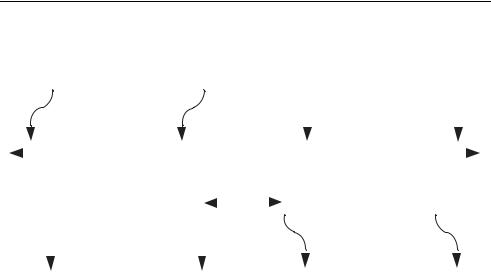

Если размер передаваемого слова меньше 8 бит, то данные необходимо загру жать в регистр USISRL таким образом, чтобы неиспользуемые биты не выдвига лись из сдвигового регистра. В зависимости от состояния бита USILSB данные должны быть выровнены по старшему или по младшему биту. В качестве примера на Рис. 14.4 показана обработка 7 битных данных.

При USI16B = 1 для хранения данных используются все 16 бит регистра USISR. Если размер передаваемого слова меньше 16 бит, то данные должны быть выровнены аналогично тому, как показано на Рис. 14.4.

354 Глава 14. Универсальный последовательный интерфейс

|

7Cбитный режим SPI, первый – MSB |

|

|

|

|

7Cбитный режим SPI, первый – LSB |

|||||||||||

|

|

|

|

|

|||||||||||||

|

|

Передаваемые данные в памяти |

|

|

|

|

Передаваемые данные в памяти |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 битное слово |

|

|

|

|

|

|

|

|

7 битное слово |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Программный сдвиг |

|

|

|

|

|

Копирование |

|

|||||||

TX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

USISRL |

|

|

RX |

RX |

|

|

USISRL |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

USISRL |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

USISRL |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Копирование |

|

|

|

|

|

|

|

|

Программный сдвиг |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 битное слово |

|

|

|

|

|

|

|

|

7 битное слово |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Полученные данные в памяти |

|

|||

|

|

Полученные данные в памяти |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 14.4. Выравнивание данных при использовании 7 битных слов.

Прерывания в режиме SPI

Модулю USI выделен один вектор прерывания, с которым в режиме SPI свя зан единственный флаг прерывания USIIFG. При установленных битах USIIE и GIE установка этого флага генерирует запрос прерывания.

Флаг USIIFG устанавливается, когда содержимое счётчика USICNTx стано вится равным нулю в результате декрементирования либо в результате непосред ственной загрузки нулевого значения. Флаг USIIFG сбрасывается при записи в биты USICNTx значения, отличного от нуля (если бит USIIFGCC = 0), или же непосредственно.

14.2.4. Режим I2C

Модуль USI переключается в режим I2C при USII2C = 1, USICKPL = 1 и USICKPH = 0. Для обеспечения совместимости со спецификацией I2C биты USILSB и USI16B должны быть сброшены. Для активации выводов SCL и SDA модуля должны быть установлены биты USIPE6 и USIPE7.

Режим ведущего I2C

Для перевода модуля USI в режим ведущего I2C необходимо установить бит USIMST. В режиме ведущего тактовый сигнал формируется модулем и выдаётся на линию SCL при USIIFG = 0. При USIIFG = 1 на линии SCL постоянно при сутствует ВЫСОКИЙ уровень. Поддерживается работа при наличии на шине не скольких ведущих (см. подраздел «Арбитраж» далее).

Поддержка ведомых устройств, способных удерживать на линии SCL НИЗ КИЙ уровень, обеспечивается только при USIDIVx > 0. Если коэффициент деле

14.2. Функционирование модуля USI 355

ния делителя тактового сигнала модуля USI равен единице (USIDIVx = 0), то подключённые к шине ведомые устройства не должны удерживать линию SCL в состоянии НИЗКОГО уровня во время передачи данных. В противном случае связь может быть нарушена.

Режим ведомого I2C

Для перевода модуля USI в режим ведущего I2C бит USIMST должен быть сброшен. В режиме ведомого на линии SCL удерживается НИЗКИЙ уровень при USIIFG = 1 и USISTTIFG = 1 или если USICNTx = 0. Бит USISTTIFG должен сбрасываться программно после инициализации ведомого устройства, когда мо дуль будет готов к получению адреса ведомого, передаваемого ведущим устрой ством.

Передача данных в режиме I2C

В режиме передачи данные сначала загружаются в регистр USISRL. Выход модуля активируется установкой бита USIOE, а процесс передачи данных запус кается записью в счётчик USICNTx числа 8. При этом сбрасывается бит USIIFG и на линии SCL начинают формироваться импульсы тактового сигнала (в режиме ведущего) или перестаёт удерживаться НИЗКИЙ уровень (в режиме ведомого). После передачи всех восьми битов флаг USIIFG устанавливается. При этом в ре жиме ведущего прекращается генерация тактового сигнала, а в режиме ведомого вывод SCL переводится в состояние НИЗКОГО уровня.

Для приёма бита квитирования I2C бит USIOE сбрасывается программой, а в USICNTx загружается 1. При этом сбрасывается флаг USIIFG и принимается один бит. После повторной установки флага USIIFG в младшем бите регистра USSRL содержится принятый бит квитирования, который может быть обработан в программе.

; Приём ACK/NACK |

|

|

BIC.B |

#USIOE,&USICTL0 |

; SDA $ вход |

MOV.B |

#01h,&USICNT |

; USICNTx = 1 |

TEST_USIIFG |

|

|

BIT.B |

#USIIFG,&USICTL1 |

; Проверяем USIIFG |

JZ |

TEST_USIIFG |

|

BIT.B |

#01h,&USISRL |

; Проверяем полученный бит квитирования |

JNZ |

HANDLE_NACK |

; Обрабатываем NACK |

...Иначе |

обрабатываем ACK |

|

Приём данных в режиме I2C

Врежиме приёма выход модуля должен быть отключён сбросом бита USIOE,

амодуль USI должен быть подготовлен к приёму данных загрузкой в счётчик USICNTx числа 8. При этом сбрасывается флаг USIIFG и на линии SCL начина ют формироваться импульсы тактового сигнала (в режиме ведущего) или пере стаёт удерживаться НИЗКИЙ уровень (в режиме ведомого). После восьми им пульсов тактового сигнала флаг USIIFG устанавливается. При этом в режиме ве дущего прекращается генерация тактового сигнала, а в режиме ведомого вывод SCL переводится в состояние НИЗКОГО уровня.

356 Глава 14. Универсальный последовательный интерфейс

Для передачи бита квитирования (ACK/NACK) в старший бит сдвигового ре гистра загружается 0 или 1, программной установкой бита USIOE активируется выход модуля USI, а в счётчик USICNTx загружается 1. После выдачи старшего бита сдвигового регистра устанавливается флаг USIIFG, после чего можно гото вить модуль к приёму следующего байта данных по шине I2C.

; Генерация ACK |

|

|

BIS.B |

#USIOE,&USICTL0 |

; SDA – выход |

MOV.B |

#00h,&USISRL |

; MSB = 0 |

MOV.B |

#01h,&USICNT |

; USICNTx = 1 |

TEST_USIIFG |

|

|

BIT.B |

#USIIFG,&USICTL1 |

; Проверяем USIIFG |

JZ |

TEST_USIIFG |

|

...продолжение... |

|

|

; Генерация NACK |

|

|

BIS.B |

#USIOE,&USICTL0 |

; SDA $ выход |

MOV.B |

#0FFh,&USISRL |

; MSB = 1 |

MOV.B |

#01h,&USICNT |

; USICNTx = 1 |

TEST_USIIFG |

|

|

BIT.B |

#USIIFG,&USICTL1 |

; Проверяем USIIFG |

JZ |

TEST_USIIFG |

|

... продолжение...

Состояние СТАРТ

Состоянию СТАРТ соответствует изменение уровня на линии SDA с ВЫСО КОГО на НИЗКИЙ при ВЫСОКОМ уровне на линии SCL. Для формирования состояния СТАРТ необходимо записать 0 в старший бит сдвигового регистра и установить биты USIGE и USIOE для отключения защёлки на выходе сдвигового регистра. При этом старший бит сдвигового регистра сразу же появляется на вы воде SDA, формируя на линии НИЗКИЙ уровень. После сброса бита USIGE ра бота защёлки возобновляется, а НИЗКИЙ уровень удерживается на линии SDA до выдачи следующего бита данных синхронно с сигналом на линии SCL.

; Формирование состояния СТАРТ |

|

|

|

MOV.B |

#000h,&USISRL |

; MSB = 0 |

|

BIS.B |

#USIGE+USIOE,&USICTL0 |

; |

Отключаем защёлку и активируем выход SDA |

BIC.B |

#USIGE,&USICTL0 |

; |

Включаем защёлку |

... продолжение...

Состояние СТОП

Состоянию СТОП соответствует изменение уровня на линии SDA с НИЗКО ГО на ВЫСОКИЙ при ВЫСОКОМ уровне на линии SCL. Для завершения пере дачи бита квитирования и выдачи на линию SDA НИЗКОГО уровня, т.е. для под готовки к формированию состояния СТОП, необходимо сбросить старший бит сдвигового регистра и загрузить 1 в счётчик USICNTx. При этом на линии SCL будет сформирован отрицательный импульс, по спадающему фронту которого на линию SDA будет выставлен НИЗКИЙ уровень. Поскольку модуль работает в ре жиме ведущего, на линии SCL останется ВЫСОКИЙ уровень. Для формирова ния состояния СТОП необходимо установить старший бит сдвигового регистра,

14.2. Функционирование модуля USI 357

загрузить 1 в счётчик USICNTx и установить биты USIGE и USIOE для отключе ния защёлки. В результате старший бит сдвигового регистра сразу же появится на выводе SDA, формируя на линии ВЫСОКИЙ уровень. Последующий сброс бита USIGE сохранит старший бит сдвигового регистра в защёлке, а сброс бита USIOE отключит выход модуля. За счёт использования внешних подтягивающих резис торов ВЫСОКИЙ уровень на линии SDA будет удерживаться до формирования состояния СТАРТ.

; Формирование состояния СТОП |

|

|

BIS.B |

#USIOE,&USICTL0 |

; SDA – выход |

MOV.B |

#000H,&USISRL |

; MSB = 0 |

MOV.B |

#001H,&USICNT |

; USICNT = 1 для 1 такта |

TEST_USIIFG |

|

|

BIT.B |

#USIIFG,&USICTL1 |

; Проверяем USIIFG |

JZ |

TEST_USIIFG |

; |

MOV.B |

#0FFH,&USISRL |

; USISRL = 1 для выдачи на SDA ВЫСОКОГО уровня |

BIS.B |

#USIGE,&USICTL0 |

; Отключаем защёлку |

BIC.B |

#USIGE+USIOE,&USICTL |

; Включаем защёлку и отключаем выход SDA |

... продолжение...

Освобождение линии SCL

Если модуль USI удерживает на линии SCL НИЗКИЙ уровень, то её можно освободить, не сбрасывая флага USIIFG, путём установки бита USISCLREL. Бит USISCLREL будет сброшен автоматически при обнаружении состояния СТАРТ, после чего, начиная со следующего тактового импульса, на линии SCL будет удерживаться НИЗКИЙ уровень.

В режиме ведомого этот бит используется для того, чтобы предотвратить удер жание НИЗКОГО уровня на линии SCL в том случае, если устройство не адресо вано ведущим. При обнаружении следующего состояния СТАРТ бит USISCLREL будет сброшен, а флаг USISTTIFG — установлен.

Арбитраж

Модуль USI может обнаруживать ситуацию потери арбитража в системах с несколькими ведущими. В процессе арбитража на шине I2C используются дан ные, выставляемые на шину SDA «конкурирующими» передатчиками. Ведущий передатчик, выставляющий на линию SDA ВЫСОКИЙ уровень, теряет арбит раж, если другой передатчик одновременно выставит на линию SDA НИЗКИЙ уровень. Потеря арбитража обнаруживается модулем USI путём сравнения значе ния, выставляемого на шину, и значения, считываемого с шины. Если эти значе ния не равны, то фиксируется потеря арбитража и устанавливается флаг USIAL. Одновременно с этим сбрасывается бит USIOE, отключая модуль от шины. Та ким образом, пользовательская программа должна контролировать состояние флагов USIAL и USIIFG, переключая модуль в режим ведомого приёмника в случае потери арбитража. Флаг USIAL должен сбрасываться программно.

Чтобы предотвратить во время арбитража генерацию тактовых сигналов более быстрыми ведущими, на линии SCL удерживается НИЗКИЙ уровень в том слу чае, если другой ведущий, присутствующий на шине, выставляет на линию НИЗ

358 Глава 14. Универсальный последовательный интерфейс

КИЙ уровень и установлен флаг USIIG или USISTTIFG или же если USICNTx = 0.

Прерывания в режиме I2C

Модулю USI выделен один вектор прерывания, с которым в режиме I2C свя заны два флага прерывания — USIIFG и USISTTIFG. Каждый флаг имеет соб ственный бит разрешения прерывания USIIE и USISTTIE соответственно. При разрешённом прерывании и установленном бите GIE установка любого флага прерывания генерирует запрос прерывания.

Флаг USIIFG устанавливается, когда содержимое счётчика USICNTx стано вится равным нулю в результате декрементирования либо в результате непосред ственной загрузки нулевого значения. Флаг USIIFG сбрасывается при записи в биты USICNTx значения, отличного от нуля (если бит USIIFGCC = 0), или же непосредственно.

Флаг USISTTIFG устанавливается при обнаружении состояния СТАРТ. Флаг USISTTIFG должен сбрасываться программно.

Обнаружение состояния СТОП сопровождается установкой флага USISTP, однако этот флаг не вызывает генерации прерывания. Флаг USISTP сбрасывается при записи в биты USICNTx значения, отличного от нуля (если бит USIIFGCC = 0), или же непосредственно.

14.3. Регистры модуля USI

Список регистров модуля USI приведён в Табл. 14.1.

Таблица 14.1. Регистры модуля USI

Регистр |

Обозначение |

Тип регистра |

Адрес |

Исходное состояние |

|

|

|

|

|

Регистр управления 0 модуля USI |

USICTL0 |

Чтение/запись |

078h |

01h после PUC |

|

|

|

|

|

Регистр управления 1 модуля USI |

USICTL1 |

Чтение/запись |

079h |

01h после PUC |

|

|

|

|

|

Регистр управления системой |

USICKCTL |

Чтение/запись |

07Ah |

Сбрасывается после PUC |

синхронизации модуля USI |

|

|

|

|

|

|

|

|

|

Регистр счётчика битов модуля USI |

USICNT |

Чтение/запись |

07Bh |

Сбрасывается после PUC |

|

|

|

|

|

Сдвиговый регистр модуля USI, |

USISRL |

Чтение/запись |

07Ch |

Не изменяется |

младший байт |

|

|

|

|

|

|

|

|

|

Сдвиговый регистр модуля USI, |

USISRH |

Чтение/запись |

07Dh |

Не изменяется |

старший байт |

|

|

|

|

Ко всем регистрам модуля USI можно обращаться с использованием двухбайтных команд, как показано в Табл. 14.2.

Таблица 14.2. Обращение к регистрам модуля USI с использованием двухбайтных команд

Регистр |

Обозначение |

Старший байт |

Младший байт |

Адрес |

|

|

|

|

|

Регистр управления модуля USI |

USICTL |

USICTL1 |

USICTL0 |

078h |

|

|

|

|

|

Регистр управления системой синх |

USICCTL |

USICNT |

USICKCTL |

07Ah |

ронизации и счётчиком модуля USI |

|

|

|

|

|

|

|

|

|

Сдвиговый регистр модуля USI |

USISR |

USISRH |

USISRL |

07Ch |

|

|

|

|

|

360 Глава 14. Универсальный последовательный интерфейс

USISTTIE Бит 5 Разрешение прерывания при обнаружении состояния СТАРТ. 0 Прерывание запрещено

|

|

1 |

Прерывание разрешено |

USIIE |

Бит 4 |

Разрешение прерывания от счётчика битов. |

|

|

|

0 |

Прерывание запрещено |

|

|

1 |

Прерывание разрешено |

USIAL |

Бит 3 |

Потеря арбитража. |

|

|

|

0 |

Не было потери арбитража |

|

|

1 |

Арбитраж потерян |

USISTP |

Бит 2 |

Обнаружено состояние СТОП. Бит USISTP автоматически сбрасы |

|

|

|

вается при записи в биты USICNTx значения, отличного от нуля, ес |

|

|

|

ли USIIFGCC = 0. |

|

|

|

0 |

Состояние СТОП не обнаружено |

|

|

1 |

Состояние СТОП обнаружено |

USISTTIFG Бит 1 Флаг прерывания при обнаружении состояния СТАРТ.

0 Состояние СТАРТ не обнаружено. Прерывания не было

1Состояние СТАРТ обнаружено. Прерывание было

USIIFG |

Бит 0 Флаг прерывания от счётчика битов. |

Устанавливается |

при |

|

|

USICNTx = 0. Автоматически сбрасывается |

при записи в |

биты |

|

|

USICNTx значения, отличного от нуля, если USIIFGCC = 0. |

|

||

|

0 |

Прерывания не было |

|

|

|

1 |

Прерывание было |

|

|

USICKCTL, регистр управления системой синхронизации модуля USI

7 |

6 |

|

5 |

|

4 |

3 |

2 |

1 |

0 |

|

USIDIVx |

|

|

|

|

USISSELx |

|

USICKPL |

USISWCLK |

|

|

|

|

|

|

|

|

|

|

rw–0 |

rw–0 |

|

rw–0 |

|

rw–0 |

rw–0 |

rw–0 |

rw–0 |

rw–0 |

USIDIVx |

Биты |

Коэффициент деления тактового сигнала. |

|

|

|||||

|

7…5 |

000 |

1 |

|

|

|

|

|

|

|

|

001 |

2 |

|

|

|

|

|

|

|

|

010 |

4 |

|

|

|

|

|

|

|

|

011 |

8 |

|

|

|

|

|

|

|

|

100 |

16 |

|

|

|

|

|

|

|

|

101 |

32 |

|

|

|

|

|

|

|

|

110 |

64 |

|

|

|

|

|

|

|

|

111 |

128 |

|

|

|

|

|

|

USISSELx |

Биты |

Выбор источника тактового сигнала. |

|

|

|

||||

|

4…2 |

000 |

SCLK (не используется в режиме SPI) |

|

|

||||

|

|

001 |

ACLK |

|

|

|

|

|

|

|

|

010 |

SMCLK |

|

|

|

|

|

|

|

|

011 |

SMCLK |

|

|

|

|

|

|

|

|

100 |

Бит USISWCLK |

|

|

|

|

||

|

|

101 |

TACCR0 |

|

|

|

|

|

|

|

|

110 |

TACCR1 |

|

|

|

|

|

|

|

|

111 |

TACCR2 (зарезервировано в моделях MSP430F20xx) |

|

|||||

USICKPL Бит 1 Полярность тактового сигнала.

0 Неактивное состояние — НИЗКИЙ уровень

1Неактивное состояние — ВЫСОКИЙ уровень