Микропроцессорная техника / Семейство микроконтроллеров MSP430x2xx_

.pdf

5.2. Функционирование модуля синхронизации 231

DCOCLK. Посредством делителя частота сигнала от выбранного источника уменьшается в 1, 2, 4 или 8 раз. Сигнал MCLK используется для тактирова ния ЦПУ и системы.

SMCLK — дополнительный тактовый сигнал. Источник выбирается про граммно: LFXT1CLK, VLOCLK, XT2CLK (если имеется в конкретной мо дели) или DCOCLK. Посредством делителя частота сигнала от выбранного источника уменьшается в 1, 2, 4 или 8 раз. Сигнал SMCLK может програм

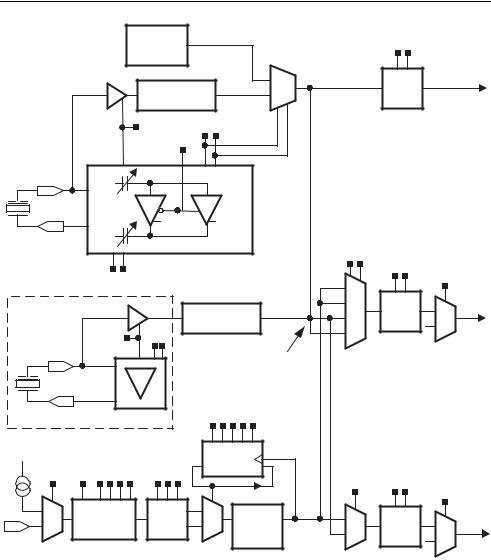

мно назначаться для отдельных периферийных модулей. Блок схема модуля синхронизации приведена на Рис. 5.1.

5.2.Функционирование модуля синхронизации

После сигнала PUC (очистка при включении питания) тактовые сигналы MCLK и SMCLK формируются из DCOCLK, имеющем частоту около 1.1 МГц (точное значение приводится в документации на конкретные модели). Сигнал ACLK формируется из LFXT1CLK, при этом генератор LFXT1 работает в режиме LF с использованием встроенных конденсаторов (нагрузочная ёмкость — 6 пФ).

Биты управления SCG0, SCG1, OSCOFF и CPUOFF регистра состояния оп ределяют режимы работы ядра MSP430 и включают или отключают отдельные уз лы модуля синхронизации (см. главу 2 «Сброс, прерывания и режимы работы»). Конфигурирование модуля осуществляется с помощью регистров DCOCTL, BCSCTL1, BCSCTL2 и BCSCTL3.

Изменение конфигурации модуля Base Clock Module+ может быть выполнено программно в любой момент времени:

BIS.B #RSEL2+RSEL1+RSEL0,&BCSCTL1 ; Выбираем 7$й диапазон

BIS.B #DCO2+DCO1+DCO0,&DCOCTL |

; Выбираем максимальную частоту DCO |

5.2.1.Возможности модуля синхронизации и приложения с низким энергопотреблением

К системе синхронизации устройств с батарейным питанием часто предъяв ляются противоречивые требования:

наличие тактового сигнала низкой частоты для снижения энергопотребле ния и реализации функций отсчёта времени;

наличие тактового сигнала высокой частоты для обеспечения быстрой ре акции на события и быстрой обработки данных;

обеспечение стабильности частоты тактового сигнала при изменении тем пературы и напряжения питания.

Модуль синхронизации Basic Clock Module+ разработан с учётом перечислен ных требований и позволяет пользователю выбирать любой из трёх доступных так товых сигналов: ACLK, MCLK и SMCLK. Для достижения оптимальной произво дительности при незначительном потреблении в качестве источника сигнала ACLK может использоваться экономичный «часовой» кварц частотой 32 768 Гц, при этом обеспечивается стабильный синхросигнал и малое потребление в режиме ожидания. Если точность формирования временных интервалов не критична, то в качестве источника сигнала ACLK может использоваться встроенный низкочас

232 Глава 5. Модуль синхронизации Basic Clock Module+ |

|

|

|

|

|

|||||

|

|

Встроенный |

VLOCLK |

|

|

|

DIVAx |

|

|

|

|

|

НЧ генератор* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LFXT1CLK |

10 |

|

|

Делитель |

|

|

|

|

Фильтр импульсов |

ост. |

|

|

на |

|

|

||

|

|

мин. длительности |

|

|

|

1/2/4/8 |

ACLK |

|||

|

|

|

|

|

|

|||||

|

|

|

LFXT1Sx |

|

|

|

|

Вспомогательный |

||

|

|

OSCOFF |

|

|

|

|

тактовый сигнал |

|||

|

|

XTS |

|

|

|

|

|

|

|

|

XIN |

0 В |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LF |

XT* |

|

|

|

|

|

|

|

|

|

LFOff |

|

XT1Off |

|

|

|

|

|

|

XOUT |

0 В |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SELMx |

|

|

|

|

|

Генератор LFXT1 |

|

|

|

|

DIVMx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XCAPx |

|

|

|

|

|

|

|

CPUOFF |

|

|

|

|

|

|

|

00 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XT2CLK |

01 |

Делитель |

0 |

|

|

|

|

|

Фильтр импульсов |

10 |

на |

|

||||

|

|

|

мин. длительности |

|

|

1/2/4/8 |

1 |

|

||

|

|

|

|

|

|

|

MCLK |

|||

|

|

|

|

|

|

|

11 |

|

||

|

XT2OFF |

XT2S |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

XT2IN |

|

|

|

|

|

|

|

|

Основной |

|

|

|

Соединено только тогда, |

|

|

тактовый сигнал |

|||||

|

|

|

|

|

||||||

|

|

XT |

когда XT2 отсутствует |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

XT2OUT |

Генератор XT2* |

|

MODx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

VCC |

|

|

Модулятор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

DCOR |

SCG0 RSELx |

DCOx |

|

|

|

|

SELS |

DIVSx |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

SCG1 |

|

0 |

off |

n |

0 |

Фильтр |

|

|

|

|

|

|

Генератор |

|

|

Делитель |

|

|

|||||

DCO |

|

0 |

|

|

||||||

1 |

1 |

импульсов |

|

0 |

|

|||||

пост. тока |

n+1 |

DCOCLK |

|

на |

|

|||||

мин. дли |

1 |

|

||||||||

Rosc * |

|

|

|

|

1/2/4/8 |

1 |

|

|||

|

|

|

тельности |

|

|

SMCLK |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Дополнительный |

|

|

|

|

|

|

|

|

|

|

тактовый сигнал |

|

*Различные исполнения модуля синхронизации |

|

|

|

|

|

|

||||

Не во всех моделях семейства MSP430x2xx модуль синхронизации реализован полностью. |

||||||||||

MSP430x20xx — LFXT1 не поддерживает режим HS, XT2 отсутствует, использование вне |

||||||||||

шнего ROSC не поддерживается. |

|

|

|

|

|

|

|

|

||

MSP430x21x1 — встроенный НЧ генератор отсутствует, XT2 отсутствует, использование |

||||||||||

внешнего ROSC не поддерживается. |

|

|

|

|

|

|

|

|||

MSP430x21x2 — XT2 отсутствует. |

|

|

|

|

|

|

|

|

||

MSP430x22xx, MSP430x23x0 — XT2 отсутствует. |

|

|

|

|

|

|

||||

Рис. 5.1. Блок схема модуля синхронизации Basic Clock Module+.

5.2. Функционирование модуля синхронизации 233

тотный генератор. Сигнал MCLK может формироваться встроенным DCO, кото рый в случае необходимости активируется обработчиками прерываний при наступ лении соответствующих событий. Сигнал SMCLK может формироваться кварце вым генератором с внешним резонатором либо DCO в зависимости от требований, предъявляемых периферийными модулями. Гибкая система тактирования и нали чие делителей тактовых сигналов обеспечивают возможность точной настройки модуля синхронизации в соответствии с требованиями конкретного приложения.

5.2.2.Встроенный низкочастотный генератор со сверхнизким потреблением

Встроенный НЧ генератор со сверхнизким потреблением (VLO) работает на частоте 12 кГц (прочие параметры приводятся в документации на конкретные мо дели) без внешнего кварцевого резонатора. Использование VCOCLK в качестве источника тактового сигнала задаётся битами LFXT1Sx = 10 при XTS = 0. Бит OSCOFF отключает генератор для перехода в режим пониженного энергопотреб ления LPM4. При использовании генератора VLO кварцевый генератор LFXT1 отключается, снижая тем самым потребление микроконтроллера. Если генератор VLO не используется, то его ток потребления равен нулю.

5.2.3. Генератор LFXT1

Генератор LFXT1 имеет очень малое потребление в режиме LF (XT = 0) при использовании «часового» кварца частотой 32 768 Гц. Кварцевый резонатор под ключается к выводам XIN и XOUT микроконтроллера без использования допол нительных элементов. Величина нагрузочной ёмкости для кварцевого резонатора при работе генератора LFXT1 в режиме LF задаётся программно конфигурируе мыми битами XCAPx. Эта ёмкость может принимать значения из ряда: 1 пФ, 6 пФ, 10 пФ или 12.5 пФ. При необходимости допускается подключение внешних конденсаторов.

Врежиме HF (XTS = 1, XCAPx = 00) генератор LFXT1 поддерживает исполь зование высокочастотных кварцевых и керамических резонаторов. Высокочас тотный резонатор подключается к выводам XIN и XOUT, при этом на обоих вы водах должны присутствовать внешние нагрузочные конденсаторы. Ёмкость дан ных конденсаторов выбирается в соответствии со спецификацией используемого резонатора. Биты LFXT1Sx определяют рабочий диапазон частот при работе ге нератора LFXT1 в режиме HF.

Влюбом из режимов генератор LFXT1 может работать с внешним тактовым сигналом, подаваемым на вход XIN (LFXT1Sx = 11, OSCOFF = 0, XCAPx = 00). При использовании внешнего сигнала его частота должна соответствовать специ фикации микроконтроллера для выбранного режима. Если частота внешнего сиг нала окажется ниже минимально допустимой величины, то может быть установ лен бит LFXT1OF, предотвращающий тактирование ЦПУ сигналом LFXT1CLK.

Если LFXT1CLK не используется в качестве источника тактового сигнала SMCLK или MCLK, то генератор LFXT1 может быть отключён установкой бита OSCOFF, как показано на Рис. 5.2.

234 Глава 5. Модуль синхронизации Basic Clock Module+ |

|

XTS |

|

Запрос ACLK |

|

OSCOFF |

|

Запрос MCLK |

LFOff |

CPUOFF |

|

SELM0 |

LFXT1Off |

|

|

XSELM1 |

|

XT2 |

XT1Off |

Запрос SMCLK |

XT2 — внутренний сигнал |

SCG1 |

XT2 = 0 — устройства без генератора XT2 |

SELS |

XT2 = 1 — устройства с генератором XT2 |

|

|

|

Рис. 5.2. Сигналы отключения генератора LFXT1. |

Примечание. Особенности генератора LFXT1

Время запуска низкочастотных кварцевых резонаторов часто составляет несколь ко сотен миллисекунд.

Генераторы с очень малым потреблением, такие как генератор LFXT1 в режиме LF, необходимо защищать от помех со стороны других источников. Резонатор должен быть размещён как можно ближе к микроконтроллеру, корпус резонатора

— заземлён, а дорожки, связывающие резонатор с микроконтроллером, — защи щены «земляными» цепями.

5.2.4. Генератор XT2

В некоторых моделях имеется второй кварцевый генератор, XT2. Этот генера тор формирует сигнал XT2CLK, а его параметры идентичны параметрам генера тора LFXT1 в режиме HF. Рабочий диапазон частот генератора XT2 задаётся би тами XT2Sx. Если сигнал XT2CLK не используется в качестве источника тактово го сигнала SMCLK или MCLK, то генератор XT2 может быть отключён установкой бита XT2OFF, как показано на Рис. 5.3.

Генератор XT2 может работать с внешним тактовым сигналом, подаваемым на вход XT2IN (XT2Sx = 11 и XT2OFF = 0). При использовании внешнего сигнала его частота должна соответствовать спецификации генератора для конкретной модели. Если частота внешнего сигнала окажется ниже минимально допустимой величины, то может быть установлен бит XT2OF, предотвращающий тактирова ние ЦПУ сигналом XT2CLK.

XT2OFF |

|

Запрос MCLK |

|

CPUOFF |

|

SELM0 |

XT2off (внутренний сигнал) |

XSELM1 |

|

Запрос SMCLK |

|

SCG1 |

|

SELS |

|

Рис. 5.3. Сигналы отключения генератора XT2.

5.2.Функционирование модуля синхронизации 235

5.2.5.Генератор с цифровым управлением (DCO)

Генератор DCO представляет собой встроенный генератор с цифровым уп равлением. Частота DCO может подстраиваться программно с помощью битов DCOx, MODx и RSELx.

Отключение DCO

Если DCO не используется для формирования тактового сигнала SMCLK или MCLK в активном режиме микроконтроллера, то он может быть отключён уста новкой бита SCG0, как показано на Рис. 5.4.

Запрос MCLK |

|

|

CPUOFF |

|

|

XSELM1 |

|

|

Запрос SMCLK |

D |

Q |

|

|

|

SCG1 |

|

|

SELS |

DCOCLK |

|

|

|

|

DCOCLK |

SYNC |

|

XT2CLK |

|

|

DCOCLK_on

1 — вкл.

0 — выкл.

DCO_Gen_on

SCG0 |

1 — вкл. |

|

0 — выкл. |

Рис. 5.4. Управление работой DCO.

Подстройка частоты DCO

После сигнала PUC в биты управления DCO загружаются такие значения (RSELx = 7, DCOx = 3), которые обеспечивают запуск DCO на средней частоте рабочего диапазона. При этом тактовые сигналы MCLK и SMCLK формируются из сигнала DCOCLK. Поскольку ЦПУ тактируется сигналом MCLK, а DCO име ет весьма малое время запуска, программа начинает выполняться менее чем через 2 мкс после появления сигнала PUC. Типовые значения диапазонов и дискрет ных интервалов для битов RSELx и DCOx показаны на Рис. 5.5.

Частота сигнала DCOCLK устанавливается следующим образом:

Четыре бита RSELx определяют один из шестнадцати рабочих диапазонов DCO. Значения частот для этих диапазонов приводятся в документации на конкретные модели.

Три бита DCOx делят выбранный диапазон на 8 дискретных значений, от личающихся друг от друга примерно на 10%.

Пять битов MODx определяют частоту переключений с текущей частоты, заданной битами DCOx, на следующую частоту, соответствующую значе нию DCOx+1. При DCOx = 07h содержимое битов MODx игнорируется, поскольку в этом случае DCO уже работает на максимально возможной для выбранного диапазона RSELx частоте.

236 Глава 5. Модуль синхронизации Basic Clock Module+

RSEL = 15

fDCO [кГц]

20 000

RSEL = 7

1000

RSEL= 0

100

DCO = 0 DCO = 1 DCO = 2 DCO = 3 DCO = 4 DCO = 5 DCO = 6 DCO = 7

Рис. 5.5. Частота DCO и значения битов DCOx и RSELx.

Все микроконтроллеры семейства MSP430F2xx содержат в сегменте А инфор мационной секции флэш памяти значения регистров DCOCTL и BCSCTL1, от калиброванные для конкретных частот. Чтобы использовать калиброванные зна чения, их копируют из флэш памяти в соответствующие регистры. Эти значения определяют состояния битов DCOx, MODx, RSELx и сбрасывают все прочие би ты регистров, за исключением бита XT2OFF, который устанавливается в 1. Ос тальные биты регистра BCSCTL1 могут быть индивидуально установлены или сброшены командами BIS.B или BIC.B.

; Установка DCO на частоту |

1 МГц: |

||

MOV.B &CALBC1_1MHZ,&BCSCTL1 |

; Устанавливаем диапазон |

||

MOV.B &CALDCO_1MHZ,&DCOCTL |

|

; |

Устанавливаем частоту DCO и параметры |

|

|

; |

модуляции |

Использование внешнего резистора (ROSC) с DCO

Некоторые модели микроконтроллеров MSP430F2xx позволяют задавать ток DCO при помощи внешнего резистора ROSC, подключённого к DVCC. Этот режим включается при DCOR = 1. В данном режиме DCO имеет такие же характеристи ки, как и в моделях семейства MSP430x1xx, при этом биты RSELx могут прини мать значения от 0 до 7 (бит RSEL3 игнорируется). Такая опция позволяет реали зовать дополнительный метод регулирования частоты DCO посредством измене ния сопротивления резистора. Параметры DCO для данного режима приводятся в документации на конкретные модели.

5.2.6. Модулятор DCO

Модулятор смешивает два сигнала DCO с частотами fDCO и fDCO+1, формируя сигнал с эффективной частотой, находящейся в диапазоне от fDCO до fDCO+1. При этом происходит распределение энергии тактового сигнала, что уменьшает уро вень электромагнитных помех. Модулятор смешивает сигналы на протяжении

|

5.2. Функционирование модуля синхронизации 237 |

32 тактов DCOCLK и конфигурируется при помощи битов MODx. При MODx = |

|

0 модулятор выключен. |

|

Смешивание сигналов осуществляется в соответствии с формулой: |

|

t =(32 − MODx)× tDCO + MODx × tDCO+1 . |

|

Поскольку fDCO меньше эффективной частоты, а fDCO — больше, погрешность |

|

эффективной частоты в сумме получается равной нулю. Накопления погрешнос |

|

ти не происходит. Работа модулятора иллюстрируется на Рис. 5.6. |

|

MODx |

|

31 |

|

24 |

|

16 |

|

15 |

|

5 |

|

4 |

|

3 |

|

2 |

Сигнал DCO высшей частоты fDCO+1 |

Сигнал DCO низшей частоты fDCO |

|

1 |

|

0 |

|

Рис. 5.6. Сигналы модулятора. |

|

Конфигурирование модулятора и управление DCO осуществляется програм мно. Сигнал DCOCLK можно сравнить со стабильным сигналом известной час тоты, после чего подстроить его частоту, корректируя значения битов DCOx, RSELx и MODx. Рекомендации по использованию DCO и примеры программно го кода доступны на сайте производителя http://www.msp430.com.

5.2.7. Отказоустойчивая работа модуля синхронизации

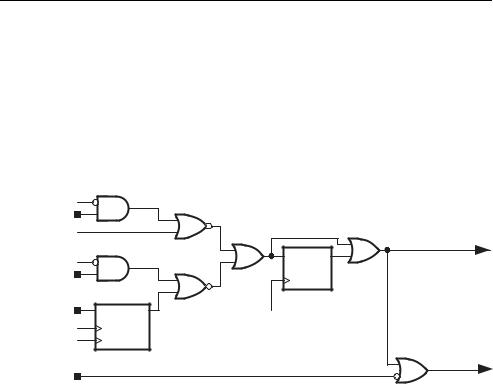

Модуль синхронизации Basic Clock Module+ позволяет обеспечить работо способность микроконтроллера при неисправности тактового генератора. При этом распознаются неисправности генераторов LFXT1 и XT2, как показано на

Рис. 5.7.

238 Глава 5. Модуль синхронизации Basic Clock Module+

LF_OscFault

XTS

LFXT1OF

Установка флага OFIFG

XT1_OscFault

XT2OF

XT2_OscFault

Рис. 5.7. Логика обработки сигналов о неисправности генераторов.

Отслеживаются следующие ситуации:

неисправность низкочастотного генератора LFXT1 в режиме LF (LFXT1OF);

неисправность низкочастотного генератора LFXT1 в режиме HF (LFXT1OF);

неисправность высокочастотного генератора XT2 (XT2OF).

Биты неисправности кварцевых генераторов LFXT1OF и XT2OF устанавлива ются, если соответствующий генератор включён, но работает некорректно. Эти биты остаются в установленном состоянии до устранения причины, вызвавшей отказ генератора, и автоматически сбрасываются, если включённый генератор работает нормально.

Флаг неисправности генератора OFIFG устанавливается и защёлкивается в момент сброса по включению питания или при обнаружении неисправности ге нератора (LFXT1OF или XT2OF). При установленном бите OFIFG тактовый сиг нал MCLK формируется из сигнала DCO и, если установлен бит OFIE, генериру ется запрос NMI прерывания. При переходе к обработчику прерывания бит OFIE сбрасывается автоматически. Флаг OFIFG необходимо сбрасывать про граммно. Конкретный источник неисправности можно определить, проверив со стояния отдельных битов неисправности.

Если обнаружена неисправность кварцевого генератора, использующегося для формирования тактового сигнала MCLK, то этот сигнал автоматически пере ключается на DCO. При этом состояние битов SELMx не изменяется — данная ситуация должна обрабатываться пользовательской программой.

Использование кварцевого генератора для формирования MCLK

После сброса по включению питания (PUC) тактовый сигнал MCLK форми руется из сигнала DCOCLK. При необходимости для формирования MCLK мож но использовать генератор LFXT1 или XT2.

Для переключения тактового сигнала MCLK с DCOCLK на сигнал от кварце вого генератора (LFXT1CLK или XT2CLK) необходимо выполнить следующие действия:

1.Включить генератор и выбрать требуемый режим работы.

2.Сбросить флаг OFIFG.

3.Подождать не менее 50 мкс.

4.Проверить флаг OFIFG — если он установлен, то повторить этапы 1…4.

|

|

|

5.3. Регистры модуля синхронизации 239 |

|

|||

; Выбираем для MCLK генератор LFXT1 (режим HF) |

|||

BIC.W |

#OSCOFF,SR |

; |

Включаем генератор |

BIS.B |

#XTS,&BCSCTL1 |

; |

Режим HF |

MOV.B |

#LFXT1S0,&BCSCTL3 |

; |

Резонатор 1–3 МГц |

L1 BIC.B |

#OFIFG,&IFG1 |

; |

Сбрасываем OFIFG |

MOV.W |

#0FFh,R15 |

; |

Формируем задержку |

L2 DEC.W |

R15 |

; |

|

JNZ |

L2 |

; |

|

BIT.B |

#OFIFG,&IFG1 |

; |

Проверяем OFIFG |

JNZ |

L1 |

; |

При необходимости проверку повторяем |

BIS.B |

#SELM1+SELM0,&BCSCTL2 ; |

Выбираем LFXT1CLK |

|

5.2.8. Синхронизация тактовых сигналов

При переключении тактового сигнала MCLK или SMCLK с одного источника на другой осуществляется синхронизация (Рис. 5.8), позволяющая избежать воз никновения состояний «гонки» сигналов:

1.Тактовый сигнал продолжает формироваться из текущего опорного сигнала до появления следующего нарастающего фронта.

2.Тактовый сигнал удерживается в состоянии ВЫСОКОГО уровня до появления нарастающего фронта сигнала от нового источника.

3.Выбирается новый источник, и формирование тактового сигнала продолжает ся в нормальном режиме.

Выбор

LFXT1CLK

DCOCLK

LFXT1CLK

MCLK

|

|

|

|

Ожидание |

|

|

|

|

|

|

|

|

|

|

LFXT1CLK |

||||||

DCOCLK |

|

|

|

|

||||||

|

|

|

LFXT1CLK |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

Рис. 5.8. Переключение тактового сигнала MCLK с DCOCLK на LFXT1CLK.

5.3.Регистры модуля синхронизации

Список регистров модуля Basic Clock Module+ приведён в Табл. 5.1.

240 Глава 5. Модуль синхронизации Basic Clock Module+

Таблица 5.1. Регистры модуля Basic Clock Module+

Регистр |

Обозначение |

Тип регистра |

Адрес |

Исходное состояние |

|

|

|

|

|

|

|

Регистр управления DCO |

DCOCTL |

Чтение/запись |

056h |

060h |

после PUC |

|

|

|

|

|

|

Регистр управления 1 модуля синх |

BCSCTL1 |

Чтение/запись |

057h |

087h |

после POR* |

ронизации |

|

|

|

|

|

|

|

|

|

|

|

Регистр управления 2 модуля синх |

BCSCTL2 |

Чтение/запись |

058h |

Сбрасывается после PUC |

|

ронизации |

|

|

|

|

|

|

|

|

|

|

|

Регистр управления 3 модуля синх |

BCSCTL3 |

Чтение/запись |

053h |

005h |

после PUC |

ронизации |

|

|

|

|

|

|

|

|

|

|

|

Регистр разрешения прерываний 1 |

IE1 |

Чтение/запись |

000h |

Сбрасывается после PUC |

|

|

|

|

|

|

|

Регистр флагов прерываний 1 |

IFG1 |

Чтение/запись |

002h |

Сбрасывается после PUC |

|

|

|

|

|

|

|

* Некоторые биты регистра также инициализируются при PUC. См. описание регистра.

DCOCTL, регистр управления DCO

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

DCOx |

|

|

|

|

MODx |

|

|

|

|

|

|

|

|

|

|

|

rw–0 |

rw–1 |

|

rw–1 |

rw–0 |

rw–0 |

rw–0 |

rw–0 |

rw–0 |

DCOx |

Биты |

Выбор частоты DCO. Эти биты определяют одно из восьми дискрет |

||||||

|

7…5 |

ных значений частоты в пределах выбранного диапазона, задаваемо |

||||||

|

|

го битами RSELx. |

|

|

|

|

||

MODx |

Биты |

Настройка модулятора. Эти биты определяют, как часто сигнал час |

||||||

|

4…0 |

тотой fDCO+1 будет использоваться в течение периода, равного 32 так |

||||||

|

|

там DCOCLK. В оставшееся время (MOD – 32) будет использоваться |

||||||

|

|

сигнал частотой fDCO. Эти биты не используются при DCOx = 7. |

||||||

BCSCTL1, регистр управления 1 модуля синхронизации |

|

|

||||||

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

XT2OFF |

XTS* |

|

DIVAx |

|

RSELx |

|

|

|

|

|

|

|

|

|

|

|

|

rw–(1) |

rw–(0) |

|

rw–(0) |

rw–(0) |

rw–0 |

rw–1 |

rw–1 |

rw–1 |

*XTS = 1 не поддерживается в микроконтроллерах MSP430x20xx. |

|

|

||||||

XT2OFF |

Бит 7 |

Выключение XT2. Этот бит управляет работой генератора XT2. |

||||||

0XT2 включен

1XT2 выключен и не используется для формирования MCLK или SMCLK

XTS |

Бит 6 |

Режим LFXT1. Этот бит определяет режим работы генератора LFXT1. |

|

|

|

0 |

Низкочастотный режим (LF) |

|

|

1 |

Высокочастотный режим (HF) |

DIVAx |

Биты |

Делитель для ACLK. |

|

|

5…4 |

00 |

/1 |

|

|

01 |

/2 |

|

|

10 |

/4 |

|

|

11 |

/8 |

RSELx |

Биты |

Выбор диапазона. Доступно 16 частотных диапазонов. Нижнему диа |

|

|

3…0 |

пазону соответствует значение RSELx = 0. Бит RSEL3 игнорируется |

|

|

|

при DCOR = 1. |

|