203-elektrotehnika-i-elektronika-elektronika-26mb

.pdf2.Как будет вести себя схема И, если на одном из входов вслед- ствие внутренней неисправности будет постоянно присутствовать логическая единица?

3.Как будет вести себя схема ИЛИ, если на одном из входов вследствие внутренней неисправности будет постоянно присутство- вать логический нуль?

4.Какие логические функции выполняет дешифратор?

5.Каково назначение входов управления в дешифраторе?

6.Как влияет сигнал управления на выходные функции дешиф- ратора?

7.Как из двух дешифраторов 2×4 сделать один дешифратор 3×8?

8.Функцию какого электрического устройства выполняет мульти- плексор для логических сигналов?

9.Как реализовать схему мультиплексора 2×1 с управляющим входом на элементах И-НЕ?

10.Как можно на основе двух мультиплексоров 2×1 сделать один мультиплексор 4×1?

11.Перечислите логические функции одного и двух аргументов, покажите примеры реализации.

12.Приведите примеры простейших цифровых устройств на ос- нове логических элементов.

13.Реализуйте схему, реализующую функцию исключающее ИЛИ на логических элементах И-НЕ (ИЛИ-НЕ).

91

Лабораторная работа 11

ТРИГГЕРЫ

11.1. Цель работы

Изучение устройств последовательностной логики – триггеров: их структуры, функционирования.

11.2. Теоретическое введение

Триггеры относят к устройствам так называемого последователь- ностного типа, или к устройствам «с памятью». Состояние на выхо- дах таких устройств определяется не только состояниями на их вхо- дах, но и их предшествующим состоянием.

Простейшим типом триггера является RS-триггер. RS-триггеры вы- пускаются в составе некоторых серий интегральных микросхем (напри- мер, микросхема К555ТР2 серии ТТЛ, которая содержит 4 RS-триггера), либо могут быть реализованы на логических элементах.

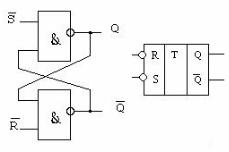

На рис. 11.1 приведена схема RS-триггера с инверсными входами на двух логических элементах типа И-НЕ и обозначение RS-триггера на принципиальных схемах.

Рис. 11.1. RS-триггер с инверсными входами

Для этого триггера существует так называемое запрещенное со- стояние для логических уровней на входах – состояние «00». Вход S называют входом установки в «1», вход R – установки в «0» или «сброса».

92

Для установки триггера в «1», необходимо, чтобы на входе S был установлен низкий уровень (уровень логического «0»), а на входе R – высокий уровень. Для переключения триггера (установки в «0») не- обходимо установить на входах обратные значения.

Комбинация на входах S = «1» и R = «1» соответствует режиму хранения, т.е. состояния на выходах триггера остаются неизменными.

Предположим, что состояние на выходе триггера (Q) соответствует уровню логического нуля, комбинация на входах S = «1» и R = «1». На втором выходе – уровень логической «1».

Если на входах установить уровни S = «1» и R = «0», на выходе Q дол- жен сохраниться «0» (на входах верхнего по схеме элемента И-НЕ все еди- ницы), а на инверсном выходе – логическая «1», так как на одном из входов нижнего по схеме элемента И-НЕ логическая «1», а на другом – «0».

При S = «0» и R = «1» на выходе Q установится «1» (на одном из входов элемента И-НЕ уровень «0»), а на инверсном выходе – логический «0».

Комбинация на входах S = «0» и R = «0» приводит к неопреде- ленным состояниям на выходах и поэтому не разрешена.

Триггер RS с входами без инверсии может быть реализован по схеме, аналогичной схеме рис. 11.1, если элементы И-НЕ заменить на элементы ИЛИ-НЕ, либо использовать дополнительно элементы НЕ для инверсии управляющих сигналов (рис. 11.2).

а |

б |

Рис. 11.2. RS-триггер на логических элементах НЕ и И-НЕ (а) и условное обозначение (б)

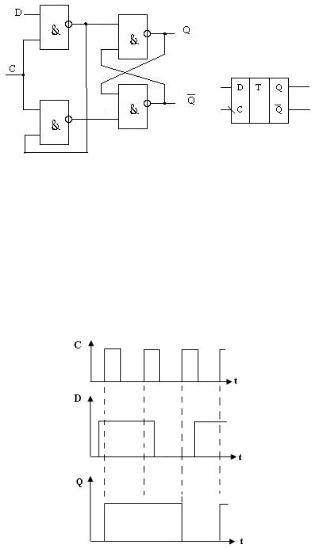

Второй тип часто используемого триггера – D-триггер, или триг- гер-задержка. Он имеет один информационный вход – D и вход син- хронизации – С. При управлении по уровню состояние на выходе триггера будет соответствовать текущему состоянию на входе D по- сле установления уровня 1 на входе синхронизации С.

93

При логическом уровне «0» на входе С триггер будет сохранять предшествующее состояние. Триггер может быть выполнен также с динамическим управлением по фронту или спаду импульса синхро- низации. Схема реализации триггера на логических элементах и ус- ловное обозначение представлены на рис. 11.3.

а |

б |

Рис. 11.3. Схема D-триггера на логических элементах И-НЕ (а) и условное обозначение D-триггера с управлением по спаду импульса синхронизации (б)

На рис. 11.4 приведены временные диаграммы, иллюстрирующие работу D-триггера. Переключение триггера происходит при логиче- ском уровне «1» на входе С. При этом на выходе устанавливается уровень, соответствующий уровню на входе D.

Рис. 11.4. Временные диаграммы работы D-триггера

94

Часто в D-триггерах и некоторых других типов триггеров реали-

зуют так называемое динамическое управление переключением, когда момент переключения совпадает с прохождением фронта либо спада импульса. Условные обозначения для вариантов управления пере- ключением триггеров показаны на рис. 11.5.

Рис. 11.5. Условные обозначения для статического и динамических входов

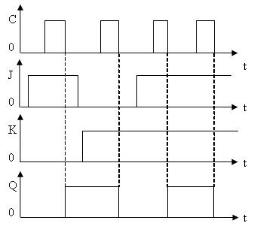

JK-триггеры. Эти триггеры могут быть синхронными или асин- хронными. Обозначение JK-триггера показано на рис. 11.6. Инфор- мационные входы триггера – J и K, вход С – исполнительный. Запись информации осуществляется по спаду импульса на этом входе. Дей- ствие JK-триггера поясняет рис. 11.7.

Рис. 11.6. Условное обозначение JK-триггера

95

Рис. 11.7. Временные диаграммы, иллюстрирующие работу JK-триггера

Таблица состояний имеет вид, приведенный в табл. 11.1.

|

|

|

|

Таблица 11.1 |

|

|

|

|

|

J |

0 |

1 |

0 |

1 |

|

|

|

|

|

K |

0 |

0 |

1 |

1 |

|

|

|

|

|

Qn+1 |

Qn |

1 |

0 |

NOT(Qn) |

|

|

|

|

|

|

|

|

|

|

Из временных диаграмм работы асинхронного JK-триггера следу- ет, что при поочередном поступлении импульсов на входы J и К этот триггер действует подобно RS-триггеру, но отличается от него при одновременной подаче «1» на оба входа: выходное состояние меня- ется на противоположное предшествующему.

Т-триггер (счетный триггер). Эти триггеры – асинхронные, име- ют только один информационный вход, и каждый импульс, посту- пающий на него, ведет к смене выходного состояния (рис. 11.8).

96

Рис. 11.8. Временные диаграммы работы Т-триггера с управлением по спаду импульса С

Счетный триггер можно реализовать из JK-триггера, если на вхо- дах J и K установить логический уровень «1».

11.3.Подготовка к работе

1.Освоить основные положения теоретического введения.

2.Нарисовать в лабораторную тетрадь принципиальные схемы и условные обозначения триггеров.

3.Подготовить таблицы состояний для триггеров RS, D, JK по форме табл.11.1 для результатов измерений.

4.Начертить в лабораторной тетради схемы проведения экспери-

мента (рис. 11.9 – 11.12).

11.4.Порядок выполнения работы

Задание 1

1. Подготовить для исследований схему RS-триггера с инверсны- ми входами (рис. 11.9).

Рис. 11.9. Исследование работы RS-триггера

97

2.Выбрать двухвходовые элементы И-НЕ (NAND2) для реализа- ции триггера. К выходам триггера подключить индикаторы (probe).

3.Заполнить таблицу состояний 11.2. Уровень логической «1» на входе устанавливают подключением входа к источнику напряжения. Состояние

«1» на выходе индицирует горящий светодиод. В табл. 11.2 S и R – входы триггера, Qn–1 – состояние до установления заданной комбинации на вхо- дах, Qn – состояние при заданной комбинации уровней на входах.

|

|

|

Таблица 11.2 |

|

|

|

|

R |

S |

Qn–1 |

Qn |

0 |

0 |

|

|

01

10

1 |

1 |

Запрещенное состояние |

4.Как работает триггер и почему состояние 0-0 на входах являет- ся запрещенным?

5.Используйте дополнительно два элемента И-НЕ в качестве эле- ментов НЕ и соберите схему RS-триггера без инверсии.

6.Составьте таблицу состояний. Каким уровням на входах будет соответствовать «запрещенное» состояние?

Задание 2

1. Собрать схему для изучения работы D-триггера (рис. 11.10).

Рис. 11.10. Исследование работы D-триггера

98

2. Выбрать триггер D Flip Flop.

3.Установить режим работы генератора импульсов (CLOCK _VOLTAGE): амплитуда 5 В, частота 2 Гц, отношение дли- тельности импульса к периоду (duty cycle) 20 %.

4.Реализовать временную диаграмму на входах D и С (см. рис. 11.4). Для реализации этой диаграммы нажатием клавиши «пробел» сфор- мируйте сигнал на входе D. Наблюдайте на осциллографе импульсы синхронизации и состояние на выходе триггера. Состояние на линии D показывает индикатор (probe).

5.Нарисуйте под временными диаграммами для D и С диа- грамму для Q.

Задание 3

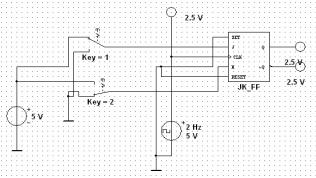

1. Подготовить для исследований схему JK-триггера (рис. 11.11).

Рис. 11.11. Исследование работы JK-триггера

2. Выбрать триггер JK Flip Flop.

3.Установить режим работы генератора импульсов (CLOCK_ VOLTAGE): амплитуда 5 В, частота 2 Гц, отношение длительности импульса к периоду (duty cycle) 20 %.

4.Провести исследование работы схемы. Переключая контакты нажатием клавиш 1 и 2 наблюдать за состояниям на выходах (по све- чению светодиодов) при J = 1, K = 0, при J = 0, K = 1, при J = 1, K = 1.

5.Составить таблицу состояний триггера (по аналогии с табл. 11.2). При установлении на входах J и K высокого уровня (ключи на

схеме в верхнем положении) триггер функционирует как T- триггер, т.е. с приходом каждого импульса на вход С меняет свое состояние.

99

Задание 4

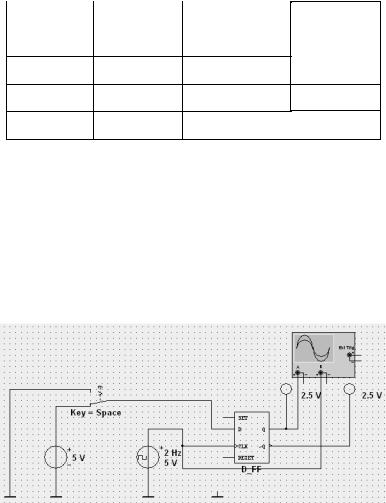

1.Подготовить для исследований схему JK-триггера (рис. 11.12).

2.Выбрать триггер Dual JK FF.

В данной схеме на вход C поступают импульсы с частотой 5 Гц, на вход J – с частотой 1 Гц и на вход K – с частотой 2 Гц. Источни- ками импульсов являются элементы «Clock».

Рис. 11.12. Исследование работы JK-триггера

3.Перечислить последовательность зажигания светодиодов на входах и выходах.

4.Переключая входы осциллографа к выводам 1C, 1J, 1K, 1Q в раз- личных комбинациях, нарисуйте соответствующие осциллограммы.

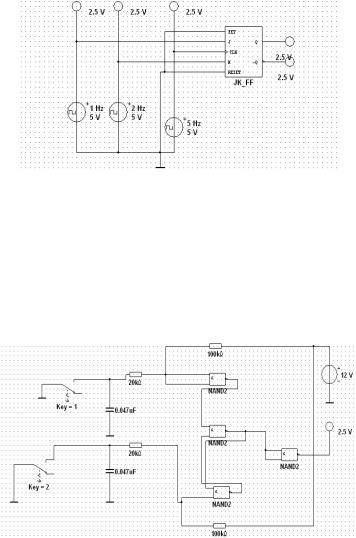

Задание 5

1. Собрать схему управления погружным насосом (рис. 11.13).

Рис. 11.13. Схема управления погружным насосом

100