Лекция 36

ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ

Цель лекции:

Изучить: принципы построения и работу программируемых логических интегральных схем.

План лекции:

1.Общая характеристика ПЛИС.

2.Обобщённая структурная схема ПЛИС.

3.Применение ППЗУ в качестве ПЛИС.

4.Программируемая матричная логика.

5.Программируемые логические матрицы.

Применение БИС и СБИС в цифровых электронных устройствах позволяет существенно улучшить их эксплуатационные возможности, в

первую очередь повысить надежность и быстродействие, снизить потребляемую мощность и габаритные размеры либо при неизменных потреблении и габаритных размерах значительно расширить функциональные возможности аппаратуры. Однако разработка БИС и СБИС представляет собой длительный и дорогостоящий процесс, который экономически оправдан только при достаточно большом объеме выпуска готовых изделий. Повышение специализации ИС при улучшении указанных выше показателей всегда вступает в противоречие с их универсальностью,

что расширяет их необходимую номенклатуру и уменьшает объем выпуска каждого отдельного типономинала. Последнее ведет к удорожанию продукции.

Устранить указанное противоречие между специализацией и универсальностью можно путем разработки БИС, алгоритмы работы которых могут быть изменены по желанию разработчика конкретной аппаратуры, то есть путем создания настраиваемых или программируемых логических схем.

Здесь под программируемостью понимается не способность реализовать заданный алгоритм обработки входных кодов, изменяя программу работы,

как это делает микропроцессор, а возможность изменения внутренней струк-

туры ИС таким образом, чтобы она обеспечивала реализацию заданных функций алгебры логики (ФАЛ) на аппаратном уровне.

При изготовлении таких ИС используется единый комплекс фотошаблонов, поэтому с точки зрения изготовителя, – это универсальные изделия. Настройку же данной ИС на заданный алгоритм работы выполняет непосредственно изготовитель аппаратуры, с точки зрения которого данная схема выполняет узкоспециализированные задачи. В результате программирования в ИС вносятся обратимые или необратимые изменения структуры, которые и приводят к получению заданных свойств.

Всоответствии со сказанным, основным преимуществом про-

граммируемых логических элементов (ЛЭ) перед специализированными БИС и СБИС является малое время изготовления ИС с наперед заданными характеристиками. При этом берется стандартная схема и подачей на определенные входы специальных сигналов или соответствующим соединением выводов направленно изменяются ее параметры.

Данное преимущество определяет основное назначение таких ИС – замену групп логических ИС малой и средней степени интеграции. По результатам зарубежных исследований в зависимости от уровня сложности одна программируемая ИС может заменить до 60 и более ИС малой и средней степени интеграции. Следовательно, такая замена позволяет в значительной степени реализовать преимущества БИС и СБИС при низкой стоимости изготовления, что особенно важно при небольших объемах выпуска конкретной аппаратуры.

Следует отметить, что возможность программирования ИС достигается путем избыточности их аппаратной части, то есть требуется введение дополнительных выводов и элементов настройки, добавление информационных цепей и т.д. Поэтому реальное быстродействие устройств,

выполненных на программируемых ИС, их потребление и другие характеристики будут всегда хуже, чем у устройств на специализированных СБИС. Однако эти характеристики будут заведомо лучше аналогичных характеристик аппаратуры, построенной на стандартных ИС малой и средней степени интеграции. Это ухудшение свойств является компенсацией за при-

обретение многофункциональности, способствующей унификации номенклатуры выпускаемой продукции электронной техники.

В качестве простейших программируемых логических интегральных схем (ПЛИС) могут использоваться ИС мультиплексоров. В более сложных случаях применяют специально разработанные для этой цели ПЛИС.

Обобщённая структурная схема ПЛИС

Рассмотрим общий вопрос технической реализации системы ФАЛ,

заданной в виде дизъюнктивной нормальной формы. Для этого рассмотрим систему ФАЛ вида

F0 ( x) |

|

xn xn 1 ...x2 x1 x0 |

|

x n xn 1 ...x2 x1 x0 |

|

... |

x n |

x n 1 ...x 2 x1 |

x 0 |

, |

|||||||||||||

F1 ( x ) |

|

xn xn 1 ... |

|

2 x1 x0 |

|

xn xn 1 ... |

|

2 x1 |

|

0 |

|

... |

|

n |

|

n 1 ... |

|

2 |

|

1 |

|

0 |

, |

x |

x |

x |

x |

x |

x |

x |

x |

||||||||||||||||

…………………………………………………………………………………....

Fm ( x) xn x n 1 ...x2 x1 x0 x n xn 1 ...x2 x1 x0 ... x n x n 1 ...x2 x1 x 0 .

Число произведений в каждой функции ограничено величиной 2n,

причем в предельном случае каждое произведение (терм) является соответствующей конституентой единицы. Для получения значения функции над всеми термами, входящими в систему ФАЛ, необходимо выполнить операцию дизъюнкции, то есть логического сложения.

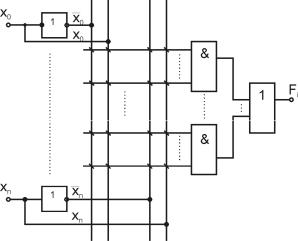

В соответствии с этим схема аппаратной реализации системы ФАЛ должна содержать последовательно включенные входной буфер, блок формирования термов, блок дизъюнкции и выходной буфер (рисунок 19).

Рисунок 19 – Обобщенная структурная схема ПЛИС

В общем случае блок термов (конъюнкций) представляет собой матрицу логических элементов И, а блок дизъюнкций – матрицу логических элементов ИЛИ. Поэтому последовательное соединение таких матриц в общем случае позволяет реализовать ФАЛ произвольного вида. Получение конкретных ФАЛ предполагает выполнение конкретных соединений в матрицах элементов И и ИЛИ.

Таким образом, меняя соединения элементов в матрицах И и ИЛИ,

можно настраивать свойства устройства, соответствующего схеме,

приведенной на рисунке 19. Практически возможны три варианта настройки:

-постоянная структура матрицы И и программируемая, изменяемая структура матрицы ИЛИ;

-изменяемая структура матрицы И и постоянная структура матрицы

ИЛИ;

-изменяемая структура как матрицы И, так и матрицы ИЛИ. Каждому из этих вариантов соответствует свой тип ПЛИС.

Технической реализацией первого типа настройки ПЛИС является ППЗУ. Второй вариант настройки ПЛИС реализован в ИС программируемой матричной логики (ПМЛ) и третий – в программируемых логических матрицах (ПЛМ).

Применение ППЗУ в качестве ПЛИС

Запоминающие устройства благодаря своей простоте и, главное,

регулярности структуры, обеспечивают высокую технологичность при

изготовлении и максимально доступную на сегодняшний день степень интеграции. Поэтому в производстве БИС и СБИС они занимают ведущее место, что является предпосылкой снижения их стоимости. В соответствии с этим расширяется и область применения ЗУ.

В структуре ППЗУ легко можно выделить блоки, соответствующие обобщенной структурной схеме ПЛИС (см. рисунок 19). Роль матрицы И выполняет дешифратор, преобразующий п входных сигналов xi в 2n

выходных сигналов N. Такое построение матрицы И предполагает вполне определенную структуру матрицы ИЛИ, функции которой, по существу,

вырождаются до уровня подключения к выходу сигналов либо лог. 0, либо лог. 1.

Такая организация позволяет реализовать при помощи ППЗУ любую систему ФАЛ. Так, на ППЗУ с организацией N×M можно реализовать систему М ФАЛ п переменных, где п = log2N. Например, на ИС ППЗУ типа

556РТ5 с организацией 512×8 можно реализовать систему восьми ФАЛ девяти переменных.

Отметим следующие особенности использования ППЗУ в качестве ПЛИС:

-ППЗУ реализует ФАЛ, представленную в виде совершенной дезъюнктивной нормальной формы, то есть ФАЛ должна быть представлена суммой конституент единицы, поэтому для технической реализации ее минимизация не требуется;

-ППЗУ позволяет реализовать только полностью определенные ФАЛ,

поэтому требуется однозначность ее значений для всех возможных комбинаций входных переменных.

Из указанных особенностей следует, что при реализации любой ФАЛ п переменных в ППЗУ предполагаются одинаковые аппаратные затраты,

соответствующие максимально возможному числу конституент исходного набора переменных, то есть всегда существует возможность получения всех

N конституент. Поэтому, несмотря на относительную дешевизну ЭЗЭ по

сравнению со стандартными ЛЭ, применение ППЗУ технически и экономически оправдано только для реализации сложных, не поддающихся минимизации ФАЛ. К внешнему признаку таких функций следует отнести сложность их аналитической записи.

Алгоритм преобразования системы ФАЛ, не заданной таблично, к виду,

предполагающему ее реализацию с использованием ППЗУ, имеет следующий вид.

1.Записывают исходную систему ФАЛ.

2.Преобразуют эту систему к виду дизъюнкций конституент единицы,

для чего в неполные произведения вводят недостающие переменные путем домножения их на единичную сумму (xi xi).

3. Составляют таблицу программирования ППЗУ. Следует отметить, что быстродействие устройств, использующих для реализации заданных систем ФАЛ ППЗУ, как правило, выше, чем при реализации на основе стандартных ЛЭ, и равно времени обращения выбранного типа ИС.

Программируемая матричная логика

Практика показывает, что, как правило, ФАЛ, реализация которых необходима для решения тех или иных задач, содержит большое число переменных, но задана существенно меньшим, чем 2n числом конституент единицы. В этом случае применение ППЗУ в качестве ПЛИС становится неэффективным, что объясняется их большой аппаратной избыточностью.

Действительно, увеличение числа входных переменных на единицу требует двойного увеличения числа выходов дешифратора ППЗУ, то есть существенно усложняет ИС и повышает ее стоимость. Этот недостаток ППЗУ привел к созданию принципиально нового класса приборов – программируемой матричной логики (ПМЛ), в которой увеличение числа входов матрицы И не приводит к увеличению числа ее выходов. Это достигается уменьшением максимального числа конституент, задающих

исходную ФАЛ. Однако на практике это в подавляющем большинстве случаев вполне оправдано. Таким образом, ИС ПМЛ при одинаковой с ППЗУ площади кристалла позволяет реализовать ФАЛ значительно большего числа входных переменных.

Поскольку в ПМЛ появляется ограничение на максимальное число конъюнкций, то такие ИС, кроме разрядности входного слова п и числа выходных функций р, характеризуются еще одним параметром – максимальным числом конъюнкций (термов) в ФАЛ. Таким образом, одна ИС ПМЛ позволяет из п входных переменных синтезировать не более одного терма, который можно объединить с другими термами для реализации не более чем р выходных функций. Поэтому для реализации ФАЛ с использованием ИС ПМЛ ее необходимо минимизировать.

Как отмечалось ранее, ПМЛ реализует второй из рассмотренных вариантов программирования ПЛИС. В этом случае настраивается матрица И при жестко заданных связях матрицы ИЛИ. Возможный вариант структурной схемы, реализующей данное техническое решение, приведен на рисунке 20,

где на пересечении шин входных переменных хi и шин входных выводов элементов И условно указано наличие всех перемычек (\). Программирование ИС выполняется устранением лишних с точки зрения реализуемого алгоритма связей между указанными шинами.

Рассмотренный тип ИС прост для реализации заданных ФАЛ и при своем изготовлении использует хорошо отработанную технологию производства ППЗУ. Поэтому данный тип ИС завоевал наибольшую популярность у разработчиков электронных устройств и на сегодняшний день составляет подавляющую долю рынка всех выпускаемых ПЛИС за рубежом.

ИС ПМЛ содержат до 3600 эквивалентных элементарных ЛЭ

(двухвходовых И–НЕ или ИЛИ–НЕ), что, практически, перекрывает потребности проектируемой аппаратуры.

Рисунок 20 – Структурная схема ПМЛ

К сожалению, следует отметить, что данный класс ИС в настоящее время не типичен для отечественной элементной базы.

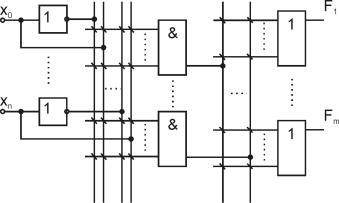

Программируемые логические матрицы

Программируемые ЛМ реализуют третий тип программирования ПЛИС и обеспечивают возможность изменения связей как в матрице И, так и в матрице ИЛИ.

При всей гибкости такого решения специалисты считают, что данный тип ПЛИС достаточно сложен для большинства потребителей с точки зрения их программирования. Кроме этого, наличие программируемого соединения,

например, плавкой перемычки, в обеих матрицах влечет за собой увеличение размеров, падение надежности и быстродействия по сравнению с ПМЛ.

Сказанное и определяет меньшее распространение данного типа ИС за рубежом. К тому же усложнение ИС не дает явных преимуществ при проектировании электронных схем.

Возможный вариант структурной схемы, реализующей рассмат-

риваемый принцип построения ПЛИС, показан на рисунке 21. На нем также

условно показано наличие всех перемычек в матрицах И и ИЛИ.

Рисунок 21 – Структурная схема ПЛМ

Как уже отмечалось, структуры ПМЛ и ПЛМ фрагментарно повторяют структуру ППЗУ. Поэтому исторически технология и физические принципы их построения повторяют путь, пройденный ППЗУ. Первыми были созданы ПЛМ и ПМЛ, изготовленные по биполярной технологии с программированием путем пережигания плавких перемычек. Затем появились ИС, выполненные по КМОП-технологии с плавкими перемычками, далее ИС с ультрафиолетовым и электрическим стиранием записанной информации. Сегодня ПЛМ и ПМЛ выпускаются с использованием всех существующих технологий.

Существует несколько способов расширения функциональных возможностей ПЛИС. Основными из них являются:

-использование дополнительных внешних соединений входных и выходных выводов, то есть введение цепей обратной связи;

-введение в ИС ПЛИС дополнительных элементов, например,

триггеров.

Отечественная промышленность выпускает ИС ПЛМ типа К556РТ1 и

К1556РТ1, обеспечивающие реализацию восьми выходных функций 16

переменных при максимальном числе термов 48.