- •Введение

- •Расшифровка и анализ задания

- •2.2 Система команд бис к1810вм86

- •2.3 Генератор тактовых импульсов

- •2.4 Буферные регистры

- •2.5 Шинные формирователи

- •2.6 Контроллер шин к1810вг88

- •2.7 Арбитр шин к1810вб89

- •2.8.2 Формирование магистралей адреса, данных и управления

- •4.3 Разработка контроллера прямого доступа к памяти

- •16К/64к – вход выбора режима. Сигнал высокого уровня на этом входе задает режим работы кдп с озу емкостью 16к слов, а сигнал низкого уровня – режим работы с озу емкостью 64к.

- •6 Организация управления мпс

- •6.1 Сопряжение с клавиатурой

- •6.2 Сопряжение с дисплеем

- •7 Построение мпс

Введение

Микроэлектроника, заявившая о себе в начале шестидесятых годов, сегодня оказывает решающее влияние на техническое перевооружение во всех областях радиоэлектроники. Цифровая техника - самое перспективное направление в современной электронике, в науке, народном хозяйстве, в учебном процессе в общеобразовательных школах, лицеях, техникумах, институтах и университетах. Без нее немыслим дальнейший научно-технический прогресс.

Постоянное повышение требований к качеству и надежности - характерная черта современного производства. Это обстоятельство приводит к необходимости постоянно модернизировать соответствующие информационно - управляющие системы. При этом, если эксплуатационные особенности, точность работы, надежность узлов системы, являющихся объектами контроля и управления (датчики, сигнализаторы, измерители и т.д.) не будут соответствовать функциональным и коммутационным возможностям устройств микропроцессорной техники, то рассчитывать на существенное улучшение свойств модернизируемой системы вряд ли стоит.

Целью курсового проекта является разработка микропроцессорной управляющей микроЭВМ, реализующей заданные взаимодействия с объектом управления (ОУ) и разработка программных средств системы, обеспечивающих выполнение заданного алгоритма управления.

-

Расшифровка и анализ задания

Задание на курсовой проект включает в себя набор исходных данных и ограничений для проектирования управляющей микроЭВМ.

Задание определяет:

- базовый микропроцессор К1810ВМ86, на основе которого требуется построить управляющую микроЭВМ.

- алгоритм управления определяется в задании видом функций f1 и f2 , длительностями управляющих сигналов t1, t2, t3, необходимо при срабатывании аварийного датчика (INT1) сформировать на пульте аварийную сигнализацию светодиодом (2Гц).

![]()

![]()

![]()

![]()

![]()

![]()

![]() мкс

мкс

![]()

![]() мкс

мкс

![]() мкс

мкс

- типы БИС, на которых должны быть реализованы блоки ПЗУ и ОЗУ: К537РУ8, К556РТ6.

Управляющая микроЭВМ проектируется на базе однокристального МП и включает в себя следующие основные устройства:

- процессорный модуль;

- память, состоящую из ОЗУ и ПЗУ;

- устройства параллельного ввода/вывода для связи с ОУ;

- блок последовательного канала для связи с ЭВМ верхнего уровня;

- программируемый системный таймер;

- контроллер прерываний;

- контроллер прямого доступа к памяти;

- пульт управления.

Алгоритм управления состоит из следующих этапов:

- обработка информации от цифровых

датчиков и выдача управляющего воздействия

![]() производится путем ввода значений х1,

х2, х3, х4 и вычисления

значения булевой функции f1(х1,

х2, х3, х4).(при единичном

значении f1

вырабатывается управляющий сигнал

производится путем ввода значений х1,

х2, х3, х4 и вычисления

значения булевой функции f1(х1,

х2, х3, х4).(при единичном

значении f1

вырабатывается управляющий сигнал

![]() =1

длительностью t1)

=1

длительностью t1)

- при обработке информации с аналоговых датчиков процессорный модуль принимает 8-разрядные двоичные коды NU1, NU2 с выводов АЦП и код константы К с регистра пульта управления; далее вычисляется значение функции NU=f2(NU1,NU2,K) и сравнивается с константой Q; в зависимости от результотов сравнения вырабатывается один из двух двоичных управляющих сигналов y2 или y3 длительностью t2 или t3 соответственно (если NU<Q, то выдается y2, иначе выдается y3);

- формируется управляющее воздействие Y4, для чего с АЦП вводится значение NU3 производится вычисление по формуле:

![]()

- значение Y4 в виде 8-разрядного кода выдается на вход ЦАП.

В системе необходимо предусмотреть следующие линии запроса на внешние прерывания:

INT0 – отказ источника питания;

INT1 – сигнал ха аварийного датчика ОУ;

INT2 – запрос от пульта управления;

INT3 – запрос от микроЭВМ верхнего уровня.

Программное обеспечение системы разрабатывается на языке Ассемблер соответствующего микропроцессора и включает следующие основные модули:

- модуль начальной инициализации системы;

- модуль управления;

- программы обслуживания прерываний, в том числе драйвер последова-тельного канала.

2 Разработка процессорного модуля, интерфейса и

уточненной структурной схемы.

2.1 Архитектура и режимы работы микропроцессора К1810ВМ86

Основные архитектурные особенности микросхемы К1810ВМ86, позволяющие больше чем на порядок повысить производительность систем, являются:

- мощная система команд с расширенными возможностями адресации памяти, включающая команды умножения, деления и обработки последовательностей байтов или слов;

- аппаратная реализация процесса совмещения операций выполнения и выборки команд;

- гибкая и мощная организация системы прерываний;

- аппаратная реализация некоторых механизмов взаимодействия нескольких процессов, упрощающая построение сложных мультипроцессорных систем.

Шестнадцатиразрядный однокристальный МП выполняющий около 2 млн. операций в секунду.

Синхронизируется с тактовой частотой 25 МГц.

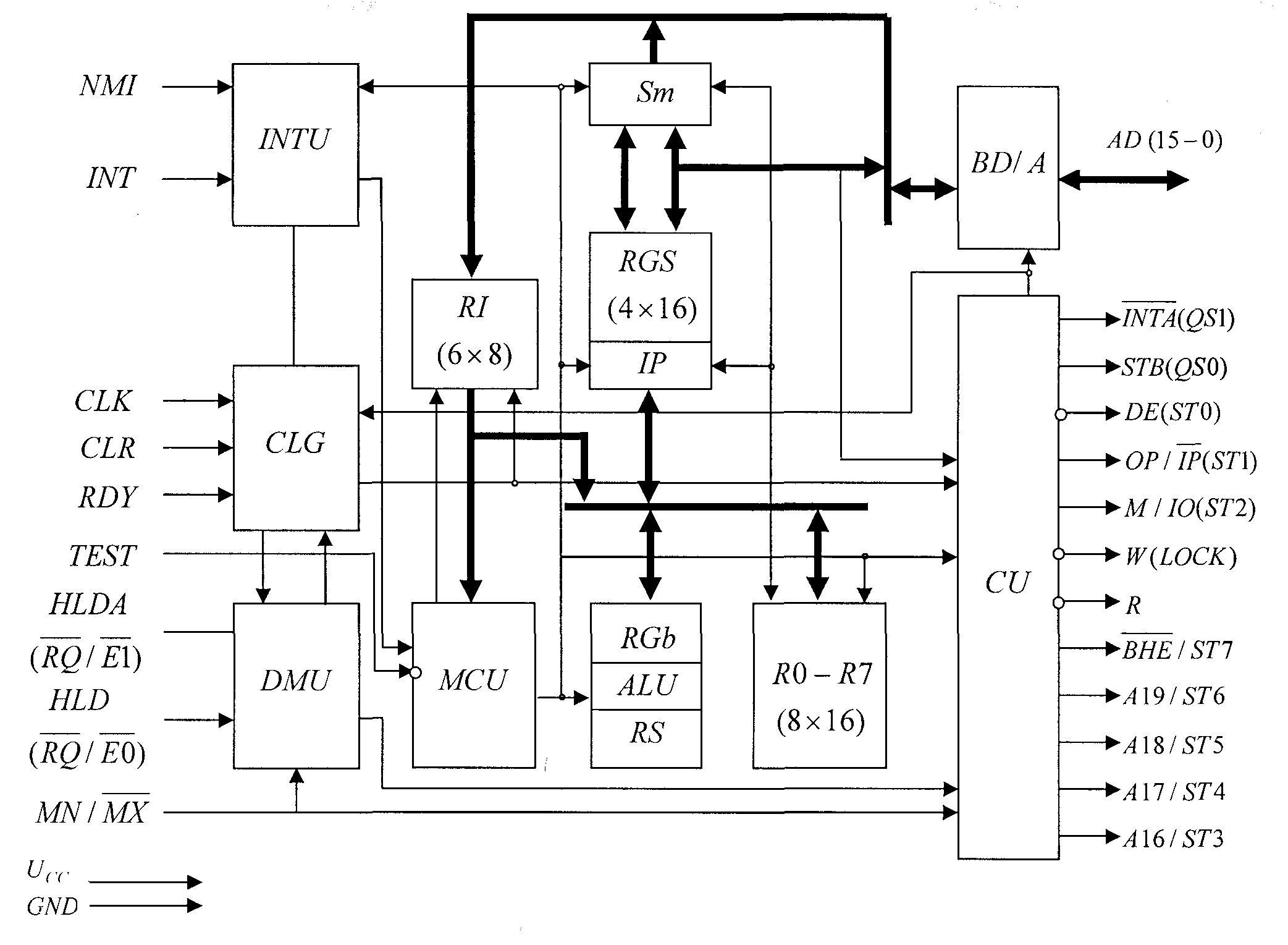

Структурная схема микропроцессора К1810ВМ86 представлена на рисунке 1. Она включает следующие устройства: арифметико-логическое устройство (ALU) с тремя регистрами временного хранения операндов (RGB) и регистром признаков (RS); группу регистров общего назначения (RO—R7); микропрограммное устройство управления (MCU) для управления выполнением команд; схему управления доступом к магистрали (DMU); схему внутренней синхронизации (CLG), преобразующую внешние тактовые импульсы во внутренние последовательности синхроимпульсов и обеспечивающую синхронизацию МП с медленными ЗУ и УВВ; схему обработки запросов прерываний (INTU); схему управления циклами обмена (CU), осуществляющую управление работой 16-разрядного канала адреса/данных; буферы канала адреса/данных (BD/A); указатель команд (IP), выполняющий функции программного счетчика; сегментные регистры (RGS), содержащие базовые адреса программ, данных и стека; сумматор адреса (Sm), служащий для вычисления 20-разрядного физического адреса; регистры очереди команд (RI), предназначенные для формирования шестибайтной очереди команд готовых к исполнению.

Рисунок 1 - Структурная схема микропроцессора К1810ВМ86

Отличительной особенностью архитектуры микропроцессора К1810ВМ86 является наличие двух основных асинхронно работающих устройств: устройства обработки (УО) и устройства сопряжения канала (УСК). Упрощенная структурная схема представляет МП в виде двух независимых устройств. УО декодирует и выполняет команды, а УСК осуществляет связь с внешними устройствами, обеспечивает выборку команд и данных из памяти, формирует очередь команд. Организация параллельной работы УО и УСК и уменьшение конфликтных ситуаций при обращении к памяти за счет применения очереди команд позволяет существенно повысить производительность систем на основе микропроцессора К1810ВМ86.

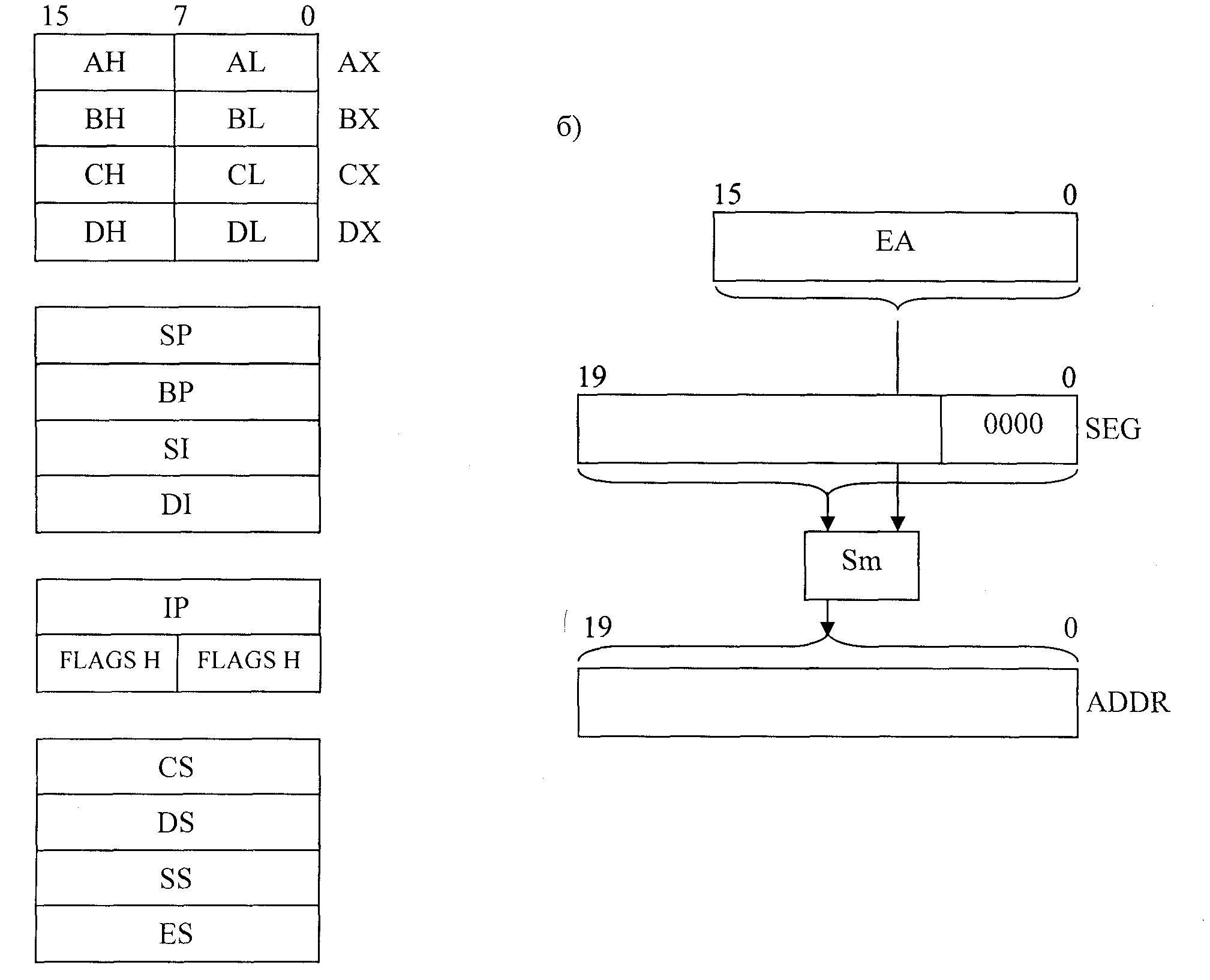

Регистровая модель микропроцессора К1810ВМ86 приведена на рисунке 2.

Рисунок 2 - Регистровая модель микропроцессора К1810ВМ86

Регистры CS, DS, SS и ES называются сегментными регистрами и используются при обращении к памяти для вычисления физических адресов ячеек. Основные назначения этих регистров следующие: регистр программного или кодового сегмента (CS) определяет текущий программный сегмент; содержимое регистра CS вместе с содержимым указателя команд (IP) задает адрес очередной команды выполняемой программы; регистр сегмента данных, или информационного сегмента (DS), используется в командах при обращении к данным; регистр стекового сегмента (SS) определяет текущий стековый сегмент и используется в командах обращения к стеку, при обработке подпрограмм и прерывании; регистр дополнительного сегмента (ES) обычно применяется как вспомогательный сегмент данных.

Регистры общего назначения АХ, ВХ, СХ и DX, называемые также регистрами данных, используются при выполнении арифметических и логических операций. Эти же регистры могут выполнять некоторые специальные функции, что и нашло отражение в их мнемонических обозначениях: АХ - аккумулятор, ВХ - базовый регистр, СХ - счетчик, DX - регистр данных. Эти регистры общего назначения допускают раздельную адресацию к их старшим (Н) и младшим (L) половинам и могут использоваться в виде набора 8-разрядных регистров.

Регистры общего назначения SP, BP, SI и DI называются адресными регистрами, так как в них хранятся относительные адреса, используемые для определения адресов операндов в пределах одного из сегментов памяти. В указателе стека (SP) и в указателе базы (ВР) содержаться относительные адреса в пределах стекового сегмента памяти, а в регистре индекса источника (SI) и регистре индекса приемника (DI) хранятся относительные адреса в пределах сегмента данных.

В пределах любого из сегментов емкостью в 64К байт обращение к операндам происходит с помощью 16-разрядного адреса смещения в сегменте. Этот адрес определяется способом адресации и называется также исполнительным адресом (ЕА). 20-разрядный физический адрес памяти (ADDR) формируется в сумматоре адреса (Sm) посредством сложения 16-раздного адреса смещения в сегменте с 16-разрядным адресом в сегментном регистре, сдвинутым на четыре разряда влево (рисунок 3).

Рассмотренные функции регистров микропроцессора К1810ВМ86 являются основными и реализуются в командах по умолчанию. Дополнительные возможности использования регистров указываются при описании конкретных видов команд.

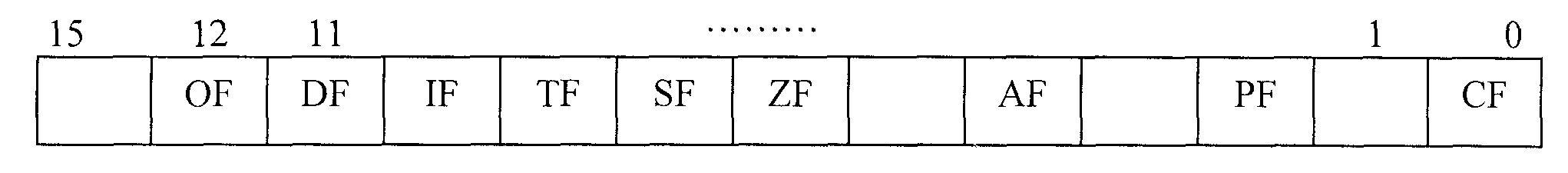

Регистр признаков или флагов (RS) состоит из одноразрядных регистров, фиксирующих состояние процессора и применяемых для управления его функционированием (рисунок 2). Флаги CF, PF, AF, SF и ZF аналогичны флагам микропроцессора КР580ИК80А и характеризуют результат выполнения последней арифметической или логической операции. Флаг переполнения OF устанавливается в состояние 1 при переполнении, возникающем в результате арифметических операций над величинами со знаком. Флаги DF, IF и TF применяются для управления микропроцессором. Флаг направления DF служит для автоматического увеличения или уменьшения адреса при обработке последовательностей символов (имитация режимов автоинкрементной и автодекрементной адресации). Установка флага разрешения прерывания IF разрешает МП прием запроса прерывания на входе INT. Установка флага трассировки TF переводит МП в состояние прерывания после выполнения каждой команды, т.е. организует режим пошагового выполнения программ.

Микропроцессор К1810ВМ86 предназначен для использования как в простых однопроцессорных, так и в сложных мультипроцессорных системах управления и обработки информации. В связи с этим МП имеет специальный вывод MN/MX (рисунок 1) для задания минимального или максимального режимов функционирования. Каждый режим характеризуется некоторым набором управляющих сигналов, соответствующим сложности проектируемой системы. При подключении вывода MN/MX к выводу Ucc микропроцессор настраивается на работу в минимальном режиме, в котором все сигналы управления периферийными устройствами вырабатываются самим МП. При подключении вывода MN/MX к выводу GND происходит изменение функций ряда управляющих сигналов и МП перенастраивается на работу в максимальном режиме. В этом режиме МП используется обычно с системным контроллером, генерирующим сигналы управления системой. Управляющие сигналы максимального режима работы на рисунке 1 заключены в круглые скобки.

Таблица 1 - Описание выводов микропроцессора, общих для максимально

го и минимального режимов

|

Обоз, вывода |

№ контакта |

Назначение вывода |

|

AD (15-0) |

39,2-16 |

Три стабильные входы/выходы канала, образующие адресную шину в такте обращения к памяти Ti и шину данных в последующих тактах (Т2, Т3, Tw, T4) |

|

A19/ST6 A18/ST5 A17/ST4 A16/ST3 |

35-38 |

Три стабильные выходы, образующие четыре старших разряда адреса памяти в такте Ti и сигналы состояния в последующих тактах; ST5 - состояние триггера разрешения прерывания; ST4 и ST3 служат для указания используемого в цикле обмена сегментного регистра, ST6 - сигнал L-уровня |

|

ВНЕ/ST7 |

34 |

Три стабильный выход, используемый для разрешения передачи данных по старшей половине шины AD (15 - 8) в такте Т1 по L-уровню сигнала ВНЕ и как сигнал состояния ST7 в тактах Т2, Т3, Т4 |

|

R |

32 |

Три стабильный выход сигнала чтения L-уровня, используемого для считывания информации из устройств, подключенных к каналу МП, и выдаваемого в тактах Т2, Т3, Tw каждого цикла чтения |

|

RDY |

22 |

Вход сигнала готовности Н-уровня, поступающего от внешних устройств и подтверждающего их готовность к обмену |

|

INT |

18 |

Вход маскируемого запроса прерывания Н - уровня |

|

NM1 |

17 |

Вход немаскируемого запроса прерывания (по положительному перепаду на входе) |

|

TEST |

23 |

Вход сигнала проверки, анализируемый специальной командой ожидания WAIT |

|

CLR |

21 |

Вход сигнала установки внутренних схем МП |

|

CLK |

19 |

Вход тактовых сигналов синхронизации |

|

MN/MX |

33 |

Вход сигнала управления режимом работы МП |

|

Ucc |

40 |

Напряжение питания (+5 В) |

|

GND |

1; 20 |

Напряжение питания (0 В) |

Таблица 2 - Описание выводов МП, используемых для минимального

режима

|

Обоз, вывода |

№ контакта |

Назначение вывода |

|

W |

29 |

Три стабильный выход сигнала записи L-уровня, используемого для записи информации в ЗУ или УВВ в зависимости от состояния сигнала М/IO и выдаваемого в тактах Т2, Т3 и Tw каждого цикла записи |

|

M/IO |

28 |

Три стабильный выход сигнала обращения к ЗУ или УВВ, вырабатываемого в такте предшествующего цикла и поддерживаемого до завершающего такта Т4 текущего цикла: L-уровень сигнала соответствует обращению к УВВ, а Н-уровень - обращению к ЗУ |

|

OP/IP |

27 |

Три стабильный выход передачи или приема данных, предназначенный для управления направлением обмена информацией через шинные формирователи |

|

DE |

26 |

Три стабильный выход сигнала разрешения передачи данных L-уровня, вырабатываемый в каждом цикле обращения к ЗУ или УВВ и в циклах подтверждения прерывания |

|

STB |

25 |

Выход строба адреса - сигнала Н-уровня, используемого для записи адреса во внешний буферный регистр адреса и генерируемого в такте Ti любого цикла канала |

|

INTA |

24 |

Выход сигнала подтверждения прерывания L-уровня, генерируемого в тактах Т2, Т3 и Tw каждого цикла подтверждения прерывания |

|

HLD |

31 |

Выход сигнала захвата, указывающего на запрос канала другим процессором |

|

HLDA |

30 |

Выход сигнала подтверждения захвата, сопровождающегося переводом канала и шин управления в высокоимпедансное состояние |

Таблица 3 - Описание выводов, используемых для максимального режима

|

Обоз, вывода |

№ контакта |

Назначение вывода |

|

ST0 - ST7 |

26, 27, 28 |

Три стабильные выходы сигналов состояния цикла канала, генерируемых в тактах Т4, Ti и Тг и используемых контроллером канала для выработки сигналов управления обменом информации с ЗУ и УВВ |

|

RQE1, RQE0 |

30,31 |

Двунаправленные выводы сигналов запроса разрешения доступа к магистрали, используемых другими устройствами, чтобы отключить МП от канала в конце текущего цикла канала; приоритет вывода RQ/Е0 выше, чем вывода RQ/E1 |

|

LOCK |

29 |

Три стабильный выход сигнала блокировки системного канала, указывающего другим устройствам на запрет использования системного канала, пока сигнал LOCK имеет L-уровень |

|

QS1,QS2 |

24,25 |

Выходы сигналов состояния очереди команд |

Назначения выводов МП и соответствующих им сигналов, общих как для максимального, так и для минимального режимов, приведены в таблице 1. Назначения выводов, относящиеся только к минимальному режиму, даны в таблице 3, а только к максимальному в таблице 3. В максимальном режиме, как это видно из таблицы 4, МП использует лишь три вывода ST0 - ST2 для управления периферией и ЗУ через контроллер, а на остальных пяти выводах генерируется сигналы, необходимые для организации работы МП в мультипроцессорных системах.

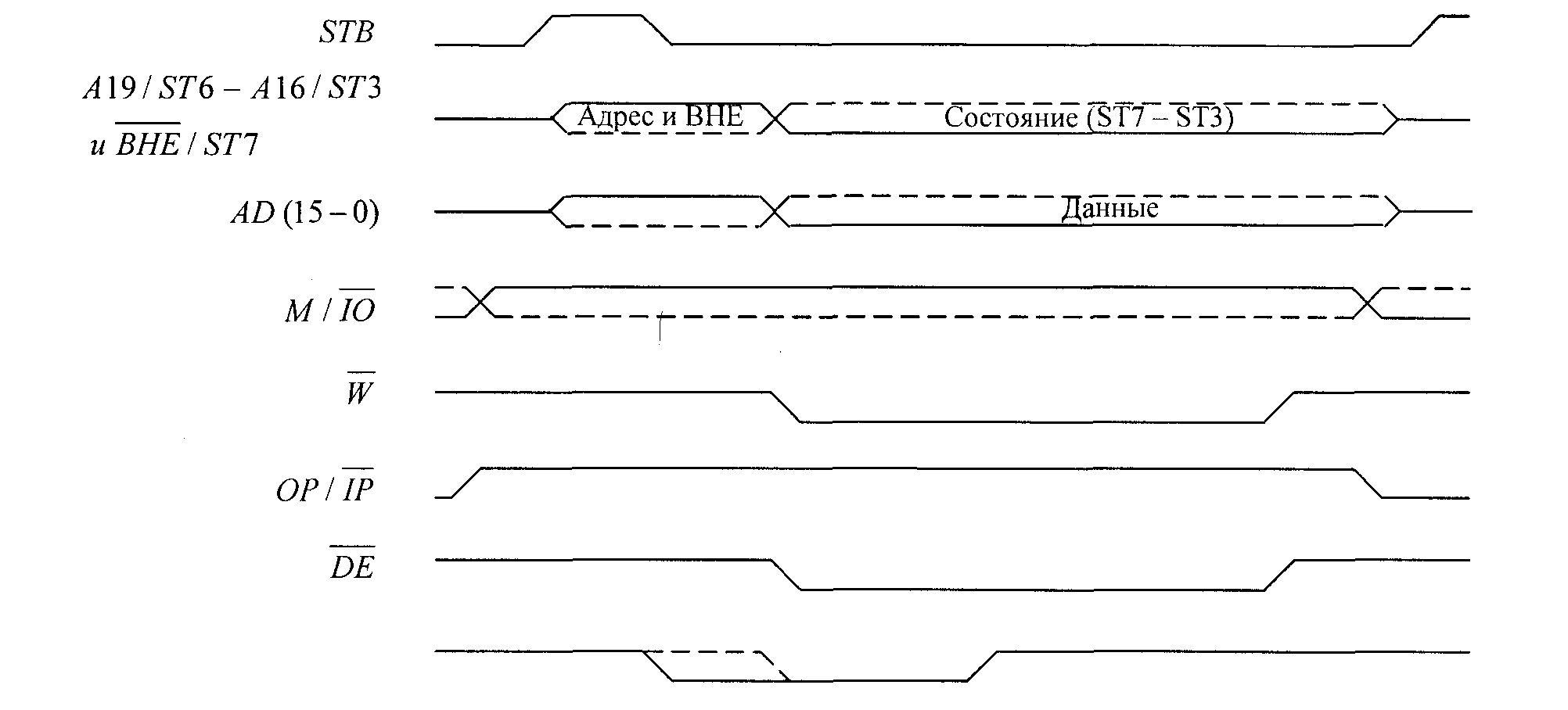

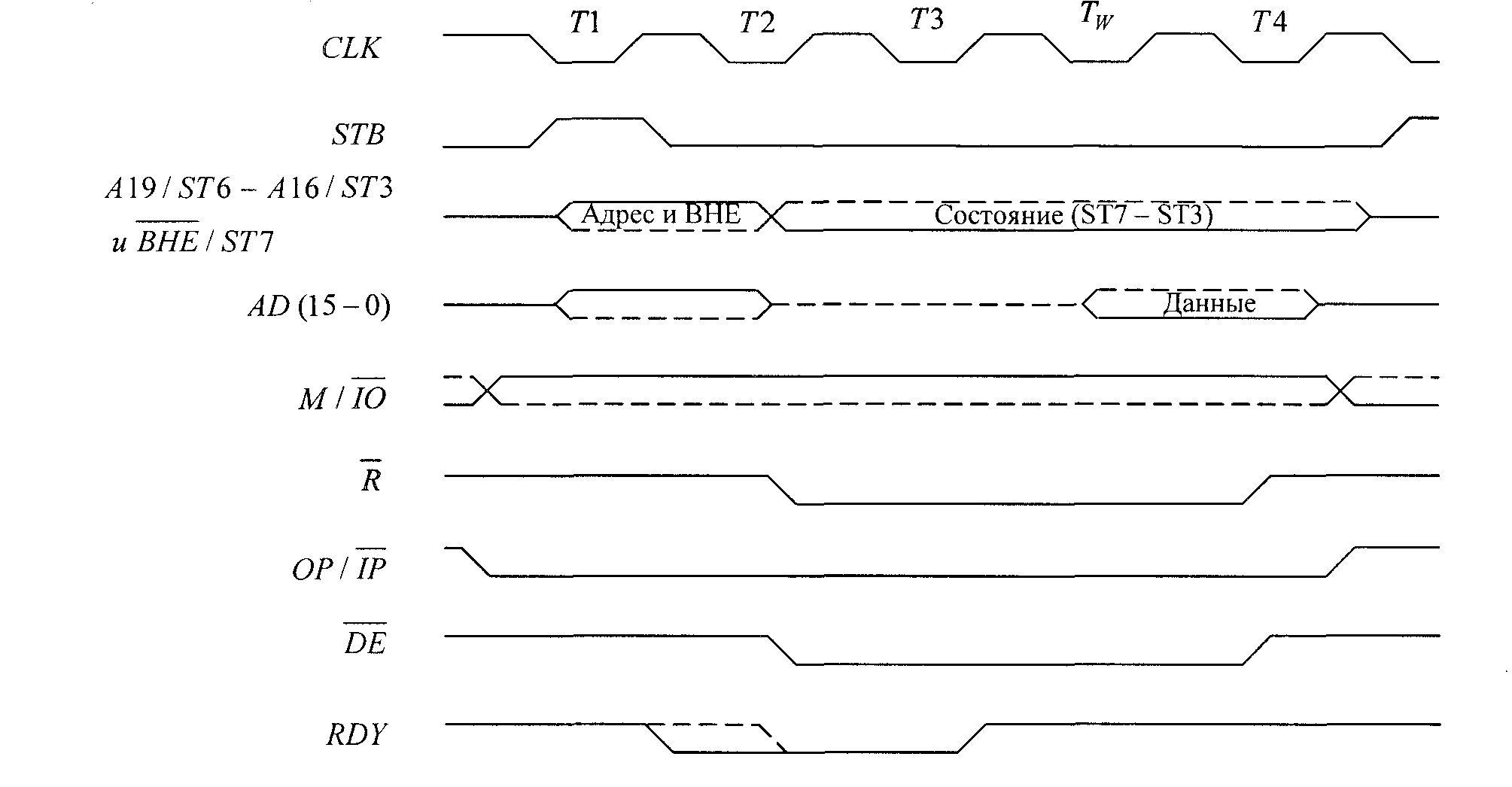

Микропроцессор К1810ВМ86 осуществляет обмен информацией с ЗУ и ВУ через 16-разрядный канал адреса/данных с помощью временного мультиплексирования. Цикл функционирования канала включает обычно выдачу адресов ЗУ или УВВ, данных, а также сигналов, сопровождающих процесс обмена, и состоит из четырех машинных тактов (Т1, Т2, Т3, Т4). В такте Ti в канал выдается адрес ЗУ или УВВ. Обмен данными для цикла записи происходит в тактах Т2, Т3, Т4, а для цикла чтения в тактах Т3, Т4. Такт Т2 в цикле чтения используется для переключения МП из режима записи в режим чтения, а канал переводится в высокоимпедансное состояние. Для согласования с медленными УВВ или ЗУ с помощью RDY между тактами Т3 и Т4 могут включаться дополнительные такты ожидания (Tw), в течение которых данные в канале остаются неизменными. Наконец, в ряде случаев между относительными циклами канала могут вводиться холостые такты Т5.

Временные диаграммы циклов чтения и записи для минимального режима представлены на рисунке 4. В цикле чтения (рисунок 3а) выдается сигнал чтения R, а также сигналы управления направлением обмена P0/IP и разрешением передачи данных DE. Сигнал DE разрешает шинным формирователям передать данные в МП. В цикле записи (рисунок 3б) сигнал DE выдается раньше, чем в цикле чтения, а выдача данных и сигнала записи W производится по переднему фронту в такте Т2. Для многих ЗУ и УВВ требуется постоянство адреса в течение всего цикла канала, поэтому в такте Т1 каждого цикла выдается стробирующий сигнал STB, позволяющий зафиксировать адрес по заднему фронту сигнала STB.

а)

б)

Рисунок 3 - Временная диаграмма цикла чтения (а) и записи (б)

Сигналы состояния ST3, ST4 указывают сегментный регистр, используемый в текущем цикле канала для вычисления физического адреса ячейки памяти.

Три 16-разрядных регистра очереди команд (RI) микропроцессора обеспечивают временное хранение 6 байт очереди команд (рисунок 1). УО микропроцессора при выполнении команды извлекает из очереди байт кода команды, не требуя доступа к каналу. УСК микропроцессора следит за состоянием очереди команд, пополняя ее, когда другие системные элементы не занимают память. При выполнении команд передачи управления очередь сбрасывается и после завершения перехода в место передачи управления начинает заполнять вновь. В максимальном режиме МП передает информацию о состоянии очереди на выходы QSO и QS1. Эта информация используется внешними процессорами. Тип цикла канала для максимального режима определяется с помощью сигналов ST2, ST1 и ST0.