- •Содержание

- •История развития микропроцессорной техники Классификация микропроцессорных средств

- •Основные определения

- •Архитектура cpu

- •Программная модель cpu.

- •Организация памяти базового мк. Память данных (пд) Карта памяти данных

- •Внешняя память мк

- •Карта памяти программ (пп)

- •Расширенная память

- •Организация sfr регистров

- •Система команд микроконтроллеров семейства mcs-51 Режимы адресации

- •Встроенные периферийные устройства мк

- •Альтернативные функции

- •Архитектура таймеров-счетчиков.

- •Форматы регистров управления. (sfr)

- •Tmod – режим (sfr)

- •Последовательный порт uart (асинхронный приёмопередатчик)

- •Форматы регистров управления Регистр управления последовательным портом scon

- •Регистр управления мощностью pmod

- •Скорость обмена данными для последовательного порта

- •Система прерываний

- •Особенности системы прерываний

- •Ie(разрешение прерываний)

- •Особенности системы прерываний мк Infineon 80c535

- •Дополнительный регистр запроса прерываний

- •Регистры приоритетов прерываний

- •Узел генератора

- •Регистры специального назначения.

- •Порты ввода-вывода

- •Цифровой коммутатор и приоритетный дешифратор

- •Форматы регистров конфигурирования

- •Особенности работы cpu. Особенности центрального процессорного устройства cip51.

- •Архитектура и программирование аналого-цифрового преобразователя(ацп)

- •Устройство выборки и хранения на входе ацп

- •Форматы регистров конфигурирования

- •Калибровка

- •Узел прямого доступа к памяти (dma)

- •2 Режима работы dma

- •2 Регистра управления dma

Форматы регистров конфигурирования

ADC0

Бит 6 – ADC0 – установка режима работы

Биты 7-4 – SC3 – SC0 – определение времени преобразования

Бит 3 – SCAL – разрешение калибровки (SCAL = 1)

Бит 2 – GCAL – калибровка чувствительности

Бит 1 – LCAL – калибровка линейности

Бит 0 – OCAL – калибровка смещения

ADC1 имеет схожую структуру.

ADC0CN

Бит 7 – ADC0 – разрешение ADC0

Бит 6 – ADT0 – дополнительное слежение

Бит 5 – AD0INT – бит прерывания («преобразование закончено»)

Бит 4 – AD0BUSY – выполняется преобразование

Бит 3-2 – AD0CM1-AD0CM0 – варианты запуска

Бит 1 – AD0WINT – флаг прерывания окна сравнения

ADC1 нет окна сравнения.

ADC1CN

Бит 3-1 – 5 вариантов запуска

Регистр управления образцовым напряжением

Бит 1 – BIASE0 – разрешение калибровок (=1)

Бит 0 – REFBE0 – образцовое напряжение – 0 -2,5 (=1)

Калибровка

2 регистра – ADC0ССF (регистр коэффициента калибровки)

(ADC1ССF)

ADC0СPT (адрес регистра коэффициентов)

(AD10СPT)

CPT после чтения автоматически инкрементируется.

ADC0ССF

|

ADC0CPT |

BIT7 |

BIT6 |

BIT5 |

|

|

|

BIT0 |

ADC0CPT – адрес

BIT7 – автоматический инкремент

BIT6 – выбор ADC

BIT5-0 – установка конкретных коэффициентов

Узел прямого доступа к памяти (dma)

DMA на кристалле разгружает процессор – направляет данных от ADC0 или ADC1.

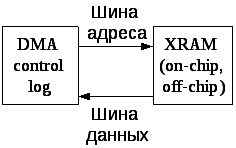

Схема 26. Узел прямого доступа к памяти

DMA имеет буфер инструкций (каким образом данные переправляются в XRAM).

Буфер инструкций – 64К

DMA POINTER – адрес инструкции

DMA DATA – сама инструкция

Двухкаскадное буферирование DMA:

-

Результат сохраняется в регистре результата ADC

-

Результат копируется через DMA s XRAM

У DMA есть свой регистр результата, куда копируется результат из ADC, а затем из этого регистра в XRAM.

Если DMA занят, то результат остается в ADC возможно переполнение и перетирание значения в регистре ADC).

DMA0

Схема 27. Устройство DMA Control Logic

DMA Control Logic принимает от ADC0результаты, записывает их в свой буфер и передает XRAM.

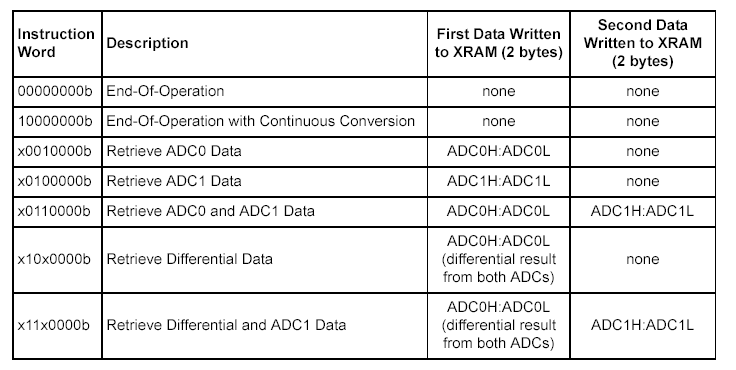

Набор инструкций для DMA04

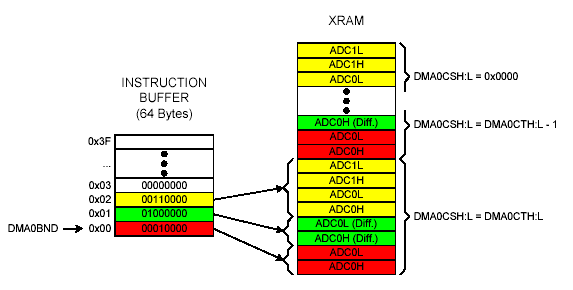

2 Режима работы dma

-

Режим 0

Регистр статуса DMA0ISW, ожидает адрес, содержащийся в регистре границы инструкции DMA0BND. Когда текущая инструкция DMA станет End of Operation instruction, Instruction Status Register сбросится в Instruction Boundary Register.

Схема 28. Режим 0 работы DMA

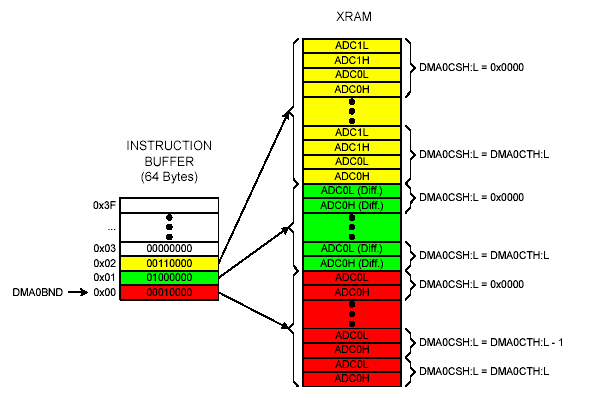

-

Режим 1

Регистр статуса DMA0ISW, ожидает адрес, содержащийся вне регистра границы инструкции DMA0BND. В конце выполнения инструкции Repeat Counter декрементируется, инструкция будет повторяться до тех пор, пока Repeat Counter не станет 0x0000. Затем значение Repeat Counter сбрасывается до Repeat Counter Limit. DMA инкрементирует DMA0ISW для следующего адреса инструкции.

Схема 29. Режим 1 работы DMA

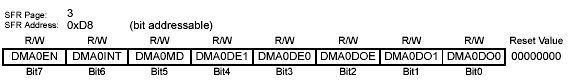

2 Регистра управления dma

DMA0CN:

Бит DMA0EN: разрешает DMA

Бит DMA0INT: 0 – операции выполняются, 1 – выполнение операций завершилось

Бит DMA0MD: режим работы DMA

Бит DMA0DE1: флаг ошибки переполнения

DMA0CF:

Бит DMA0HLT: 0 – DMA завершил доступ к XRAM, 1 – DMA работает с XRAM

1 CISC (Complex Instruction Set Computing) – традиционная архитектура процессоров с широким набором различных машинных команд переменной длины и разным временем их исполнения

RISC (Reduced Instruction Set Computing) – архитектура процессоров, построенная на основе сокращённого набора команд. Характеризуется наличием команд фиксированной длины, большого количества регистров, операций типа регистр-регистр (все, кроме команд чтения и записи в память), а также отсутствием косвенной адресации

2Гарвардская архитектура – архитектура компьютера, разработанная с целью увеличить скорость выполнения вычислительных операций и оптимизировать работу памяти. В Гарвардской архитектуре память данных отдельна от памяти программ

3 MAC (Mandatory access control) – разграничение доступа субъектов к объектам, основанное на назначении метки конфиденциальности для информации, содержащейся в объектах, и выдаче официальных разрешений (допуска) субъектам на обращение к информации такого уровня конфиденциальности

4 Конец операции, конец операции с продолжением преобразования, восстановление