Кругляк_Физика и моделирование нанотранзисторов_2018_314 стр_обложки

.pdf

Сопоставим результаты для DG ETSOI

kT |

|

q(VG VT )/kT |

|

|

|

|

||

Q(VG ) CQ q |

e |

|

|

|

, (VG |

VT ) |

(108) |

|

Q(VG ) CG (VG VT ). |

(VG |

VT ) |

|

|||||

с таковыми же (63) для массивной структуры MOS |

|

|

||||||

|

kT |

|

q(VG VT )/mkT |

|

|

|

||

Q(VG ) (m 1)Cox q |

e |

|

|

, (VG |

VT ) |

|||

Q(VG ) CG (VG VT ). |

|

|

|

|

(VG |

VT ) |

||

Организация канала проводимости (массивная структура MOS, ETSOI с двойным затвором или с одинарным и т. п.) качественно картину не меняет – заряд меняется экспоненциально с напряжением на затворе ниже порога и линейно – выше порога. В общем случае можно посчитать численно, вместе с тем, как будет показано в следующей главе, доступно эмпирическое выражение, обеспечивающее корректные результаты как ниже, так и выше порогового напряжения.

Подведем итоги. Физика процессов в полупроводниковой подложке MOSFET определяется изгибом зон, зависящим от поверхностного потенциалаS , который в свою очередь определяется напряжением на затворе VG . Получено достаточное общее уравнение (11), связывающее VG с S . В условиях режима истощения получена более простая связь S с VG (30), которой будем нередко пользоваться. Затем обсуждается поведение подвижного электронного заряда и Q VG : каким образом электронный заряд изменяется с поверхностным потенциалом и с напряжением на затворе в условиях до и после порогового напряжения. Правильные результаты в допороговой области напряжений и в режиме сильной инверсии получены не прибегая к численному решению уравнения Пуассона – Больцмана, вместе с тем численное решение этого уравнения покрывает как подпороговую область и область сильной инверсии, так и переходную область между ними. Рассмотрено поведение

Q S |

и Q VG для |

совершенно другой |

структуры |

MOS, |

структуры с |

|

исключительно тонкой кремниевой подложкой. Эта структура MOS характерна |

||||||

для нынешней |

тенденции миниатюризации транзисторов и носит название |

|||||

чрезвычайно |

тонкой |

КНИ-подложки |

(Extremely |

Thin |

Silicon-On- |

|

|

|

|

120 |

|

|

|

Insulator/ETSOI). Тем не менее, мы убедились, что основные особенности структуры ETSOI подобны свойствам массивной структуры MOS. Получены зависимости Q S для структуры ETSOI как ниже, так и выше порога напряжений. Полезны, конечно, и численное решение или эмпирическая зависимость, охватывающие всю область напряжений на затворе, к чему мы еще вернемся. Полученные результаты говорят также о том, что 1D электростатика приемлема как для массивных структур MOS, так и для структур ETSOI. Однако, далее мы покажем как 2D электростатика объясняет почему структура DG ETSOI предпочтительна для очень коротких нанотранзисторов.

121

Литература

1.R. F. Pierret, Semiconductor Device Fundamentals

(New York: Addison-Wesley: 1996).

2.B. Streetman, S. Banerjee, Solid State Electronic Devices

(New York: Prentice Hall: 2005).

3.Chenming Hu, Modern Semiconductor Devices for Integrated Circuits

(London, UK: Pearson India: 2009).

4.M. Lundstrom, Fundamentals of Nanotransistors

(Singapore: World Scientific: 2018); www.nanohub.org/courses/NT.

5.Y. Tsividis, C. McAndrew, Operation and Modeling of the MOS Transistor

(New York: Oxford Univ. Press: 2011).

6.Y. Taur, T. Ning, Fundamentals of Modern VLSI Devices

(New York: Oxford Univ. Press: 2013).

7.M. Lundstrom, Xingshu Sun, Notes on the Solution of the Poisson – Boltzmann Equation for MOS Capacitors and MOSFETs (West Lafayette, Indiana: Purdue University, USA); www.nanohub.org/resources/5338.

8.M. Lundstrom, ECE 612 Lecture 14: VT Engineering (West Lafayette, Indiana: Purdue University, USA); www.nanohub.org/resources/5670.

9.Ю. А. Кругляк, Наноэлектроника «снизу – вверх» (Одесса: ТЭС: 2015).

10.D. Vasileska, D. K. Schroder, D. K. Ferry,

IEEE Trans. Electron Dev., 44: 584 – 587 (1997).

122

Глава 4. 2D электростатика MOS и модель виртуального истока

4.1. Введение

Рассмотрим 2D электростатику MOS и обусловленные ею эффекты, а затем сформулируем ставшую уже классической модель виртуального истока без учета возможности баллистического транспорта в явном виде.

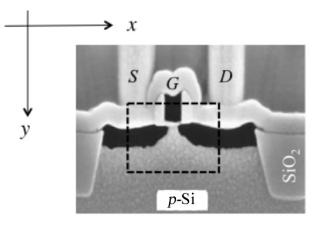

Мы до сих пор обсуждали каким именно образом поверхностный потенциал полупроводниковой подложки изменяется с ростом напряжения на затворе, прибегая к рассмотрению лишь 1D электростатики. В нанотранзисторах с короткими каналами проводимости потенциалы, подаваемые на исток и сток, создают сильное электрическое поле вдоль направления канала. Совершенно очевидно, что электростатический потенциал в короткоканальном MOSFET будет сильно изменяться в обоих х и у направлениях (рис. 1).

Рис. 1. Микрограмма сечения MOSFET, полученная на сканирующем электронном микроскопе (Texas Instruments, 1997), на которой хорошо видны

все контакты и диэлектрическая прослойка, изолирующая затвор от канала проводимости.

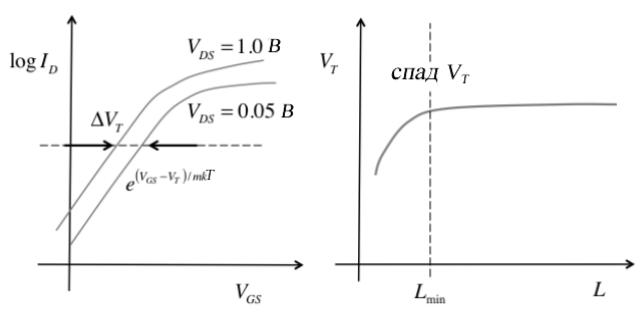

Учет 2D электростатики, особенно в нанотранзисторах, влечет серьезные последствия для режимов работы MOSFET. Как показано на рис. 2 слева, приложение большого напряжения на стоке сдвигает характеристику log10 IDS VGS влево.

Этот сдвиг на рис. 2 связан с DIBL VGS / VDS (рис. 11/гл. 1), где VGS есть такое изменение напряжения на затворе, которое необходимо, чтобы поддерживать ток стока неизменным при изменении напряжения на стоке на величину VDS .

123

Рис. 2. Иллюстративные примеры того, как учет 2D электростатики сказывается на характеристиках короткоканальных транзисторов.

Слева: DIBL, сдвигающее передаточные характеристики log10 IDS VGS ;

такое поведение может быть также интерпретировано как уменьшение порогового напряжения VT с возрастанием напряжения на стоке.

Справа: спад VT как результат снижения порогового напряжения у нанотранзисторов.

Если взять небольшой ток, соответствующий транзистору в режиме «ON» (пунктирная линия на рис. 2), то мы увидим, что большое напряжение на стоке уменьшает величину порогового напряжения на VT . Однако, полученное ранее выражение для VT (13/гл. 3) не содержит зависимости от напряжения на стоке, и

причина этого кроется в неучете 2D электростатики. Другое |

проявление |

|

2D электростатики состоит в зависимости VT |

от длины канала проводимости |

|

(рис. 2/справа). Выходное сопротивление |

транзистора также |

связано с |

2D электростатикой. Эти и другие вопросы, связанные с 2D электростатикой, обсудим в этой главе.

4.2. 2D электростатика MOS

Учесть 2D электростатику можно путем численного решения двухмерного уравнения Пуассона, а если речь пойдет о транзисторе с очень коротким каналом, то вынуждены будем решать и трехмерное уравнение Пуассона. Численное моделирование неизбежно в проектировании промышленного производства современных нанотранзисторов. Наша же задача все-таки состоит

124

в том, чтобы построить качественно правильную физическую картину процессов в MOSFET.

2D Уравнение Пуассона

Закон Гаусса для электрического смещения

|

|

|

|

D(x, y) (x, y) , |

(1) |

|

где |

D – |

вектор смещения, |

– зарядовая плотность. Связь с электрическим |

|||

полем дается соотношением |

|

|

|

|||

|

|

|

|

D(x, y) S E(x, y) , |

(2) |

|

где |

S |

– диэлектрическая |

проницаемость полупроводника |

или оксидной |

||

пленки, |

которые |

предполагаются |

пространственно |

однородными. |

||

Электростатический потенциал связан с электрическим полем: |

|

|||||

|

|

|

|

E(x, y) (x, y) , |

(3) |

|

так что уравнение Пуассона в окончательном виде

2 |

|

2 |

|

(x, y) . |

(4) |

|

x2 |

|

y2 |

|

|

S |

|

|

|

|

|

|

|

|

Нас особенно интересует решение уравнения Пуассона в подпороговой области и в самом начале режима инверсии, когда учет 2D электростатики позволяет понять природу эффекта DIBL и спада VT . В подпороговом режиме

(x, y) q[N |

(x, y) N |

(x, y)] qN |

A |

, |

(5) |

D |

A |

|

|

|

где последнее соотношение следует из предположения, что учитываются в канале проводимости только р-допанты и что они полностью ионизированы и однородно распределены.

Слой диэлектрика и электрод затвора являются частью канала проводимости и должны быть включены в рассмотрение при вычислении(x, y) . У слоя диэлектрика другая диэлектрическая проницаемость и электронным зарядом в этом слое обычно пренебрегают, так что уравнением Лапласа для этого слоя будет

2 |

|

2 |

0 . |

(6) |

x2 |

y2 |

125

В общем случае нужно численно решать систему уравнений (4) и (6) для нахождения электростатического потенциала. Мы же далее обсудим некоторые качественные подходы к пониманию решений этих уравнений.

Особое внимание далее мы уделим короткоканальным транзисторам, эффекты 2D электростатики в которых существенны. В случае достаточно длинного канала проводимости потенциал меняется медленно вдоль направления канала, так что

2 |

2 |

(7) |

|

x2 |

y2 |

||

|

и уравнение (4) сводится к одномерному уравнению Пуассона типа (57/гл. 2). Значительная и существенная часть современной традиционной модели MOSFET построена в предположении (7). Этот подход известен как плавноканальное приближение (gradual channel approximation). Стандартный подход к моделированию короткоканальных MOSFET сводится к разработке модели для достаточно длинного канала проводимости с дальнейшим учетом эффектов, вызванных 2D электростатикой [1 – 4].

Спад порогового напряжения и DIBL

Перепишем уравнение (4) с учетом (5) для режима истощения в виде

2 |

|

qN A |

|

2 . |

(8) |

|

y2 |

|

|||||

|

|

S |

x2 |

|

||

|

|

|

|

|

||

Для n-MOSFET электростатический потенциал растет от истока к стоку, так что

d /dx 0 . Электрическое поле, |

d /dx , также увеличивается |

от истока к стоку, |

|||

так что кривизна потенциала |

d 2 /dx2 положительная. |

Это |

также следует из |

||

результатов |

моделирования |

нанотранзисторов, |

представленных |

на |

|

рисунках 16 и 17/гл. 1: как при низком, так и при высоком напряжении на стоке

зависимость EC (x) имеет отрицательную кривизну, так что |

кривизна |

||||||||||||||

электростатического потенциала положительная. |

|

|

|||||||||||||

Учитывая положительную кривизну (x) , перепишем (8) в виде |

|

||||||||||||||

|

|

|

2 |

|

qN A |

|

eff |

, |

|

(9) |

|||||

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

y2 |

|

|

|

S |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

где |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N |

|

|

qN A |

|

2 |

N . |

(10) |

|||||||

|

|||||||||||||||

|

|

|

x |

|

|||||||||||

|

|

A |

eff |

S |

|

|

|

2 |

|

A |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

126 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

Уравнение (9) есть одномерное уравнение Пуассона для электростатического потенциала вглубь полупроводниковой подложки с эффективной плотностью допирования, меньшей фактической плотности допирования. Согласно (13/гл. 3), пороговое напряжение связано с плотностью допирования следующим образом:

|

|

|

|

|

2 |

|

|

|

V V |

|

|

2q s N A(2 B ) |

|

. |

(11) |

||

|

|

|

B |

|||||

T FB |

|

|

Cox |

|

|

|||

|

|

|

|

|

|

|||

Поскольку учет 2D электростатики эффективно уменьшает |

N A (10), можно |

|||||||

ожидать понижения порогового напряжения. При укорочении длины канала кривизна потенциала увеличивается, что уменьшает эффективную плотность допирования и понижает пороговое напряжение. В этом состоит объяснение почему VT уменьшается с укорочением канала проводимости (спад VT ). Прибегая к тем же самым аргументам, можно понять явление DIBL и уменьшение VT с увеличением напряжения на стоке при фиксированной длине канала: с ростом VDS кривизна потенциала d 2 /dx2 увеличивается, эффективная плотность допирования N A eff и VT уменьшаются.

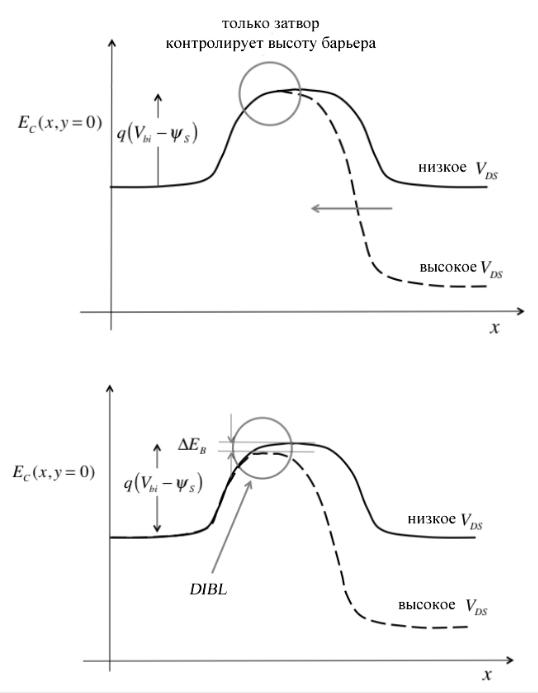

Учет 2D электростатики проявляется также в следующем. Барьер между истоком и каналом критически важен для функционирования транзистора. В идеале высота этого энергетического барьера полностью контролируется напряжением на затворе, а напряжение на стоке никак на нее не влияет (рис. 3/верх).

Вреальном транзисторе потенциал стока достает таки до вершины барьера

ипонижает его (рис. 3/низ). Через более низкий барьер проходит больше тока при том же напряжении на затворе. Можно сказать иначе: требуется меньшее напряжение на затворе для достижения нужного тока, поскольку барьер был понижен в результате влияния обоих потенциалов – и затвора и стока. Этот

эффект DIBL сдвигает передаточную характеристику log10 IDS VGS влево

(рис. 2).

Этот подход с понижением барьера также позволяет объяснить почему учет 2D электростатики понижает эффективное допирование. Для сильно допированных подложек зоны труднее изогнуть, а вот при учете 2D электростатики сток помогает затвору барьер понизить. Протяженность области канала проводимости, находящейся под влиянием стока, зависит от 2D геометрии транзистора, к обсуждению которой мы переходим.

127

Рис. 3. Иллюстрация влияния напряжения на стоке VDS на высоту барьера.

Верх: напряжение VDS не влияет на высоту барьера.

Низ: напряжение VDS немного понизило высоту барьера (эффект DIBL).

Геометрическое экранирование

Экранирование зарядов характерно для металлов и полупроводников. Если в какой-либо среде образовался «эффективный заряд», подвижные носители тока перестраиваются таким образом, чтобы нейтрализовать (экранировать)

128

этот заряд. Характерное расстояние, на котором заряд экранируется, называют длиной экранирования, или иначе, дебаевской длиной LD , а именно:

|

|

|

|

|

|

LD |

skT |

, |

(12) |

||

q2n |

|||||

|

|

0 |

|

|

|

где n0 – электронная плотность.

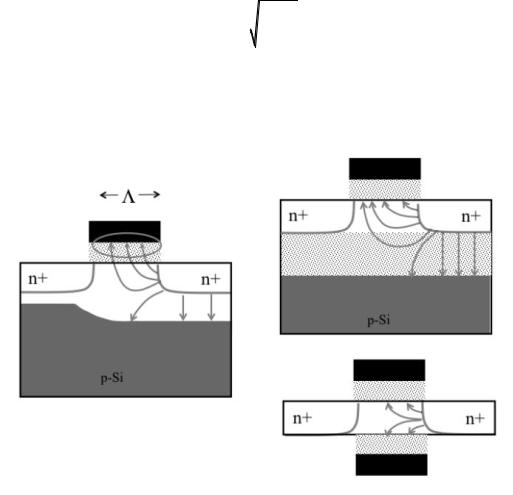

В MOSFET реализуется иной вариант экранирования электрического поля. Рисунок 4 иллюстрирует так называемое «геометрическое экранирование».

Рис. 4. Геометрическое экранирование в трех типах MOSFET. Слева: массивная структура MOSFET. Справа наверху: однозатворный SG

ETSOI. Справа внизу: DG ETSOI. В MOSFET высокого качества силовые линии электрического поля от стока проникают лишь на расстояние в канал проводимости, поскольку бόльшая часть линий закорачивается на верхнем и нижнем затворах [8].

Показаны три структуры MOSFET. Для DG ETSOI силовые линии электрического поля стока закорачиваются на верхнем и нижнем электродах затворов, проникая в канал лишь на расстояние . Если величина меньше длины канала проводимости L , L , электрическое поле стока не может «достать» начала канала проводимости и поэтому не может понизать барьер. В этом случае DIBL, если и есть, то очень небольшой. Точное значение длины геометрического экранирования определяется 2D геометрией транзистора, но интуитивно понятно, что чем плотнее окружен канал затворами, тем более

129