- •1. Осн.Параметры и характеристики ис

- •11.Классификация триггеров. АсинхронныеRs-триггеры с прямыми и инверсными входами.

- •3. Структура потенциальных элементов цэвм.

- •8.И2л:осн.Хар-ки.Баз.Лог.Элемент

- •6.Кмдп: осн хар-ки. Базовый лог элем-т

- •10. Преобразователи уровней

- •18. Классификация регистров. Параллельно-последовательные регистры.

- •17.Классификация триггеров. Специализированные характеристики триггеров.

- •38.Запоминающие устр-ва(зу):классификация,прим-ие, осн.Хар-ки.

- •2. Цифр.И анал.Эвм. Классификацияэл-вЦвм

- •9. Типы выходов цифровых элементов.

- •4. Ттл: осн хар-ки. Базовый лог элем-т.

- •7. Эсл: осн хар-ки. Базовый лог элем-т

- •36.Мультиплексоры:назнач-е,осн.Схемы,применение

- •19. Классификация регистров. Параллельные

- •20. Классификация регистров. Последоват.Регистры.

- •21. Классификация счетчиков.Вычит.Асинхр.Счетчики.

- •22. Классификация счетчиков.Сумм.Асинхр.Счетчики.

- •23. Классификация счетчиков.Реверсивн.Счет-ки

- •24. Класс-ция счет-в.Недвоич.Сч-ки.Синтез недв.Сч-ков

- •25.Классификация счет-ков.Синхр.Счетчики

- •26. Классификация счетчиков. Специализированные характеристики счетчиков.

- •27.Классификация сумматоров.Одноразр.Сумматоры.

- •29)Классификация сумматоров.Парал.Сумматор с параллельным переносом.

- •28)Классификация сумматоров.Последовательный многоразрядный сумматор.

- •32.Дешифраторы:наращ-е размерности дешифраторов:

- •34. Преобразователи кодов: назначение, основные типы.

- •35.Демультиплексоры(д):назнач-е,осн.Схемы,прим-ие

- •33.Шифраторы: назначение,осн.Схемы,применение.

- •31.Дешифраторы:назначение,осн.Схемы, применение:

- •41.Запоминающие устр-ва(зу):Блочная структура

- •42.Классификация пзу.Зэ неперепрограммируемых пзу:

- •43. Классификация пзу.Зэ программируемых пзу

- •45. Классификация озу.Зэ статических озу.

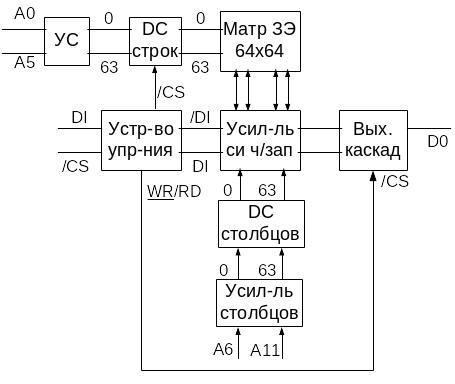

- •46. Структурная схема кмоп озу

- •48.Спец.Элементы эвм:элементы задержки

- •47. Классификация озу. Зэ динамических озу.

- •49.Спец.Элементы эвм: формирователи импульсов

- •50.Спец.Элементы эвм: генераторы

34. Преобразователи кодов: назначение, основные типы.

–устр-ва для автомат.изм-я кода по зад.алгоритму без изм-я смысл.содержания.Виды:1.Преобр-ние 1 типа(эл-ты вых.кода полностью соотв.эл-м вход.кода,но мен.их местопол-е);10110→11010.Может мен.время появления эл-в(пар-но-посл.регистры);2.Преобр-е 2 типа(кроме эл-в вх.кода в вых.присутствуют доп.эл-ты) 0110→0110_+бит контроля на четность(устр-во формир-я помехозащищ. кодов);3.Преобр-е 3 типа(эл-ты вых.кода не соотв.эл-м вх.кода) 0110→011 Форм-е кода на вых.происх.в 2 этапа ч-з промежут.код.Форм-е промежут.кода происх.при пом. дешифратора,преобр-е промежут.кода в вых.-при пом.CD. (ПЗУ:вх.код–адрес ячейки, вых.код–содержимое ячейки).

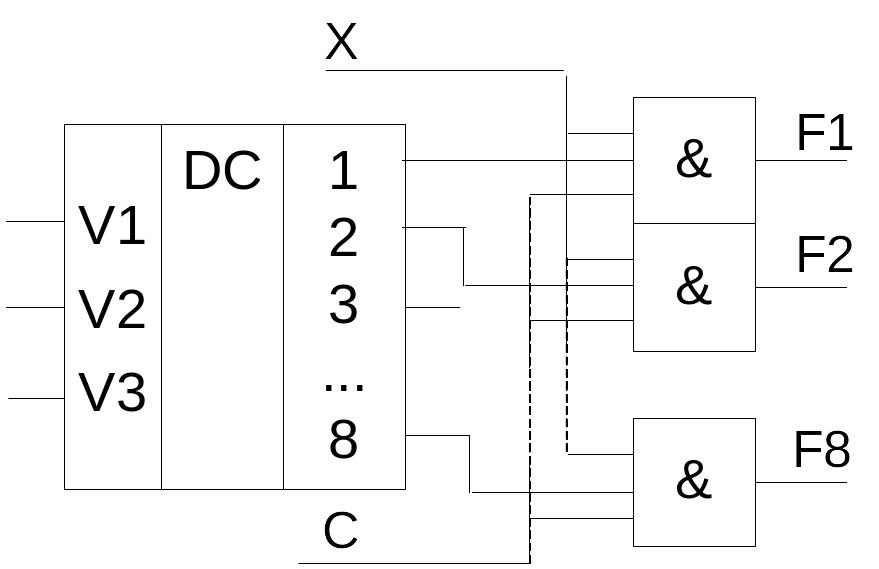

35.Демультиплексоры(д):назнач-е,осн.Схемы,прим-ие

Д–устр-ва,подключающие единств.информ.вход Х на 1 из выходов F1…Fn в зав-сти от кода на управляющих:V1..Vk, k-число упр.входов,n=2^k,k=]log2n[.

k =3,n=8

=3,n=8

V3 V2 V1 | N акт разр

0 0 0 | F1

0 0 1 | F2

0 1 0 | F3

……………. |…..

1 1 1 | F8

F1=x*/V3/V2/V1; F2=x*/V3/V2V1; ….; F8=x*V3V2V1

Код требуемого разряда подается на входы дешифр-ра V1,V2,V3.При этом на выходе дешифр-ра 1 устанавл.в раз-ряде,кот.соотв.коду поданного сигнала,на ост.выходах 0. Т.о.один эл-т”и”может пропуск.инфу со входа Х на выход F

33.Шифраторы: назначение,осн.Схемы,применение.

Вып.операцию,обр.по отн-ию к DС,т.е.преобр.код «1из N» в двоичный.При подаче «1» на один из входов шифратора, на его выходе формируется двоичный вхд номера входа.

Полный шифратор имеет 2N входов и N выходов.

N акт.разр|Q2 Q1 Q0 |

СДНФ:

|

0 | 0 0 0 |

Q0=x1+x3+x5+x7; |

1 | 0 0 1 |

Q1=x2+x3+x6+x7; |

2 | 0 1 0 |

Q2=x4+x5+x6+x7

|

3 | 0 1 1 |

|

4 | 1 0 0 |

|

5 | 1 0 1 |

|

6 | 1 1 0 |

|

7 | 1 1 1 |

Т.к. аргумент x0 не вход.ни в 1 из формул для Q, то на выходе нулевой набор CD форм-ся как при x0=0,так и при X0=1.Т.е.даже тогда,когда ни на 1 из входов не подан акт. сигнал.Для разрешения этих ситуаций необх.выход Е0.При этом данные на выходе Q явл.истинными при Е0=1.Схема им.вход синхр-ции С.При С=0 все входы СD уст-тся в ноль независимо от комбинации на входах.

31.Дешифраторы:назначение,осн.Схемы, применение:

Дешифратор–это комбинац.устр-во,преобр.вх.n-разр.дв. код в определенную комбинацию сигналов на выходах. Если число выходов s дешифратора равно 2n, то DC полный.В противном случае имеет место (2n - s) запрещенных комбинаций и DC неполныЙ.

D C

различаются по емкости, по числу каналов,

а также форматом вых.кода. В ЭВМ наиболее

часто исп-ся полный DC,

преобр.дв.код в напр-е лог-го уровня

(активного), появл.на том выходе, номер

кот.соотв.дв.коду. Ост.выходы в это время

находятся в пассивном состоянии. Такой

код называется унитарным..Fs-1

= Xn·Xn-1·…·X2·X1.Каждая

из функций представляет конъюнкцию n

переменных и может быть реализована с

помощью n-входовой

схемы "И". Входные сигналы на

дешифратор, как правило, поступают в

однофазном коде, поэтому, для получения

инверсных значений в схему DC

необх. вкл. инверторы. При необходимости

на доп. вход каждого элемента "И"

может быть подан синхросигнал, разрешающий

работу DC

только при наличии на нем активного

уровня. Внутр.стр-ра DC

на 2 входа и его УГО представлены на

рис. 1. DC,

построенные по такой схеме, называют

линейными.

C

различаются по емкости, по числу каналов,

а также форматом вых.кода. В ЭВМ наиболее

часто исп-ся полный DC,

преобр.дв.код в напр-е лог-го уровня

(активного), появл.на том выходе, номер

кот.соотв.дв.коду. Ост.выходы в это время

находятся в пассивном состоянии. Такой

код называется унитарным..Fs-1

= Xn·Xn-1·…·X2·X1.Каждая

из функций представляет конъюнкцию n

переменных и может быть реализована с

помощью n-входовой

схемы "И". Входные сигналы на

дешифратор, как правило, поступают в

однофазном коде, поэтому, для получения

инверсных значений в схему DC

необх. вкл. инверторы. При необходимости

на доп. вход каждого элемента "И"

может быть подан синхросигнал, разрешающий

работу DC

только при наличии на нем активного

уровня. Внутр.стр-ра DC

на 2 входа и его УГО представлены на

рис. 1. DC,

построенные по такой схеме, называют

линейными.

+линейныхDC высокое быстродействие. Для схемы рис. 1 оно определяется временем задержки инвертора и элемента "И". Если входные сигналы поступ.с устр-в, им. парафазный выход (например, с регистров памяти), то инверторы из схемы DC можно исключить и быстрод-е будет опр-ся только временем задержки 1 конъюнктора.

Прим-ся DC с инверс. выходами, выдающие нулевой сигнал на выходе, соотв/ поступившему на входы DC коду, при единичных сигналах на ост/выходах.

40.Запоминающие устр-ва(ЗУ): Структура 3D.

Позв.упростить дешифр-р с пом.2хкоординатн.выборки ЗЭ

а)1разряд.орг-ция:

код дреса разрядностью n дел-ся на 2 части,кажд.из кот. кодир-ся отд-но.Выбир-ся ЗЭ,кот.нах-ся на пересеч-и акт. линий DС.Кол-во пересеч-й 2N,сумм.кол-во выходов<<2N

б)многоразр.орг-ция:

|

неск.матриц упр-ся от 2х DC ||.Кол-во мат-риц=разряднос-ти слова.Кажд. матрица выдает 1 бит слова.

|

39.Запоминающие устр-ва(ЗУ): Структуры 2D, 2DM

1.двухмерная2D

k-число храним.слов,m-разр-сть 1 сл,V=k*m-емкость в бит

Дешифр-р адреса активир.1 из строк матрицы,вместе с сигналом CS разреш.доступ ко всем ее эл-м;ус-ли счит/зап опр-ют направл-е передачи вместе с сигн.WR/RD. Применение:ЗУ мал.емкости

3.стр-ра 2Dm-объедин-ся достоинства 2D и 3D стр-р.Им.1 DC адреса,но длина строкки>размера слова.Кол-во строк уменьш.=> уменьш.и кол-во выходов DC.Выбор конкр. слова из строки вып-ют MUX,кот.упр-ются частью линии адресаCтр.схема ПЗУ

стр.схема КМОП ОЗУ