Рис. 1. Принципиальная схема центрального процессорного устройства

Рис. 2. Типовая схема МП системы на базе МПК серии КР580.

Состав и функциональное назначение серии К580 представлено в таблице.

ИМС |

Функциональное назначение |

Заруб. аналог |

Тип корпуса |

ВГ18 ГФ24 ВК28

ВК38 ВТ42

BВ51А ВИ53 ВВ55А ВТ57 ВН59 ВГ75 ВВ79 ВМ80А ИР82 ИР83 ВА86 ВА87 ВК91А

ВГ92

ВГ93 ВГ72

ВР43 ВТ42 |

Контроллер шины И41 Генератор тактовых сигналов Системный контроллер и шинный формирователь. -//- Адресный мультиплексор и счетчик для динамического ОЗУ с объемом 16К Синхронно-асинхронный приемопередатчик Программируемый таймер интервалов Программируемый интерфейс параллельной связи Программируемый контроллер ПДП Программируемый контролер прерываний Программ. контроллер видеотерминала Программ. контроллер клавиатуры и индикации Центральный процессорный элемент Адресный буферный регистр Инвертированный ----//------- Шинные 8-разрядные формирователи -//- --//-- (инвер.) МП канал общего пользования (приемопередатчик на общую шину) Контроллер интерфейса МП - канал общего пользования Приемопередатчик МП - канала общего пользования Контроллер НГМД одинарный и двойной плотности записи Схема расширения ввода-вывода Адресный мультиплексор и счетчик для динамического ОЗУ с объемом 16К |

8218 8224 8228 8238

3242

8251А 8253 8255А 8257 8259 8275 8279 8080А 8282 8283 8286 8287 8291А

8293 8272А

3242 |

2123.40-2 238.16-2 2121.28-4 -//-

2121.28-5 2120.24-3 2123.40-2 2123.40-2 2121.28-5 2123.40-2 2123.40-2 2123.40-2 2140.20-1 2140.20-1 2140.20-1

2123.40-2

2121.28-10

|

Фирма Intel выпускает для МП 8080/8085 множество микросхем.

Например, выпускается 4 микросхемы PIO:

а) i8155 - имеет 3 порта, ЗУПВ 256 байт, 14-битный счетчик;

б) i8255 - имеет 3 порта;

в) i8355 - имеет 2 порта, ПЗУ 2 Кбайта;

г) i8755 - имеет 2 порта, СППЗУ 2 Кбайта.

i8231 - арифметический процессор (+,-,*,/, тригонометрич. и log функции);

i8232 - МП чисел с плавающей запятой (32 и 64 битные);

i8202 - контроллер динамических ЗУПВ;

i8253 - счетчик-таймер;

i8048 - три порта, один счетчик, ЗУПВ 64 байта, ПЗУ 1 Кбайт;

i8035 - три порта, один счетчик, ЗУПВ 64 байта, ПЗУ нет;

i8748 - три порта, один счетчик, ЗУПВ 64 байта, СПП3У 1 Кбайт;

i8049 - три порта, один счетчик, ЗУПВ 128 байт, ПЗУ 2 Кбайт;

i8022 - три порта, один счетчик, ЗУПВ 64байта, ПЗУ 1Кбайт, один АЦПУ;

i8051 - три порта, один счетчик, ЗУПВ 64 байта, ПЗУ 4 Кбайт.

Основные МП периферийные устройства, выпускаемые фирмой Intel

Microprocessor peripherals

8202A - Dynamic RAM Controller

8203 - 64Ê Dynamic RAM Controller

8206 - Error Detection and Correction Unit

8207 - Advanced Dynamic RAM Controller

8231 - Arithmetic Processing Unit

8232 - Floating Point Processing Unit

8251A - Programmable interval Timer

8254 - Programmable interval Timer (8253/8253-5)

8255A/8255-5 - Programmable Peripheral interface

8256 - Multifunction Universal Asynchronous Receiver-Transmitter

8271/8271-6 - Programmable Floppy Disk Controller

8272A - Single/Double Density Floppy Disk Controller

8273, 8273-4, 8273-8 - Programmable HDLC/SDLC Protocol Controller

8274 - Multi-Protocol Serial Controller (MPSC)

8275H - Programmable CRT Controller

8276H - Smalle System CRT Controller

8279/8279-5 - Programmable Keyboard/Display interface

8291A - GPIB Talker/Listener

8292 - GIPB Controller

8293 - GIPB Transceiver

8294A - Data Encryption Unit

8295 - Dot Matrix Printer Controller

82062 - Winchester Disk Controller

82051 - Ethernet Serial interface

82586 - Local Communications Controller

82720 - Graphics Display Controller

Рис. 3. Структурная схема МП системы на основе МП 8080А

Бис общего назначения

Шинный формирователь К589АП16(26)

Рис. 4. Шинные формирователи К589АП16, К589АП26.

Буферный усилитель данных

i8286(87) - КР580ВА86(87)

Адресный буферный регистр

i8282(83) - КР580ИР82(83)

Генератор тактовых импульсов С1,С2

i8224 (КР580ГФ24)

СИСТЕМНЫЙ КОНТРОЛЛЕР КР580ВК28(38)

(аналог i8228/38)

Программируемый параллельный интерфейс (ППИ)

i8255А (КР580ВВ55А)

Программируемый интервальный таймер (ПИТ)

i8253 (КР580ВИ53)

Таблица. Основные параметры БИС таймеров

рис. 10. Структурная схема рис. 11. Структурная схема

одного таймера канала таймера

Рис. 12. Слово управления (CW – Сommand Word) таймера

SC (Select Counter) - выбор счетчика

RL (Read/Load) - чтение/загрузка

M (Mode) - режим

BCD (Binary Coded Decimal) - двоично-десятичный код

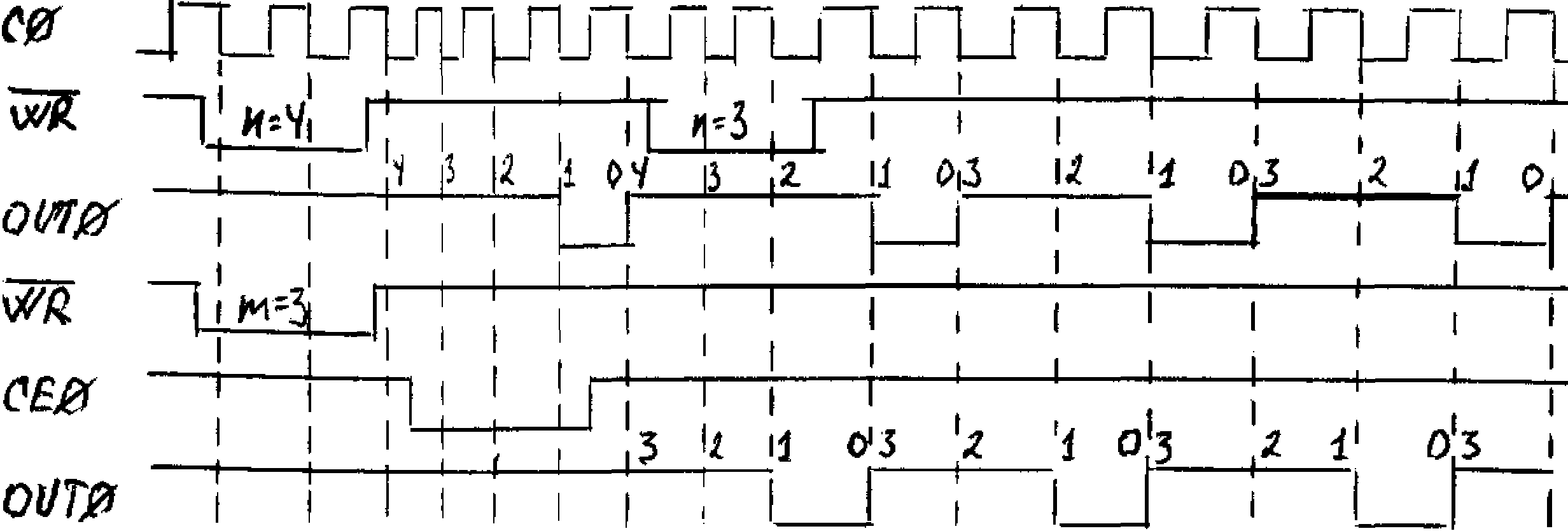

Рис. 13. Временная диаграмма работы таймера в 0 режиме

Рис. 14. Временная диаграмма работы таймера в 1 режиме

Рис. 15. Временная диаграмма работы таймера во 2 режиме

Рис. 16. Временная диаграмма работы таймера в 4 режиме

Рис. 17. Временная диаграмма работы таймера в 5 режиме

Организация прямого доступа к памяти

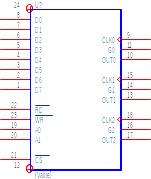

Рис. 18. Выводы БИС контроллера i8257

Рис. 19. Схема подключения DMAC к системной шине.

Рис. 20. Структурная схема БИС К580ВТ57

Регистр |

Байт |

Адрес. входы А3 А2 А1 А0 |

Двунаправленная ШД D7 D6 D5 D4 D3 D2 D1 D0 |

Адрес ПД в канале 0 |

Младший Старший |

0 0 0 0 0 0 0 0 |

А7 А6 А5 А4 А3 А2 А1 А0 А15 А14 А13 А12 А11 А10 А9 А8 |

N-1 циклов в канале 0 |

Младший Старший |

0 0 0 1 0 0 0 1 |

С7 С6 С5 С4 С3 С2 С1 С0 ЧтП ЗпП С13 С12 С11 С10 С9 С8 |

Адрес ПД в канале 1 |

Младший Старший |

0 0 1 0 0 0 1 0 |

То же, что и для канала 0

|

N-1 циклов в канале 1 |

Младший Старший |

0 0 1 1 0 0 1 1 |

|

Адрес ПД в канале 2 |

Младший Старший |

0 1 0 0 0 1 0 0 |

То же, что и для канала 0

|

N-1 циклов в канале 2 |

Младший Старший |

0 1 0 1 0 1 0 1 |

|

Адрес ПД в канале 3 |

Младший Старший |

0 1 1 0 0 1 1 0 |

То же, что и для канала 0

|

N-1 циклов в канале 3 |

Младший Старший |

0 1 1 1 0 1 1 1 |

|

Установка режима 1 0 0 0 А3 КС- УЗ ЦСП РКЗ РК2 РК1 РК0

(только

записыв.)

стоп

(только

записыв.)

стоп

Регистр состояния 1 0 0 0 0 0 0 ФОД ТС3 ТС2 ТС1 ТС0

(только читается)

АЗ - Автозагрузка

УЗ - Удлиненная запись

ЦСП - Циклический сдвиг приоритета

РКi - Разрешение i-го канала

ФОД - Флаг обновления данных

CLK

DREQ

HRQ

HLDA

AEN

ADSTB

DB7-DB0

A7-A0

DACK

IOR#,MEMR#

IOW#,MEMW#

INT,EOP#

EXT,EOP#

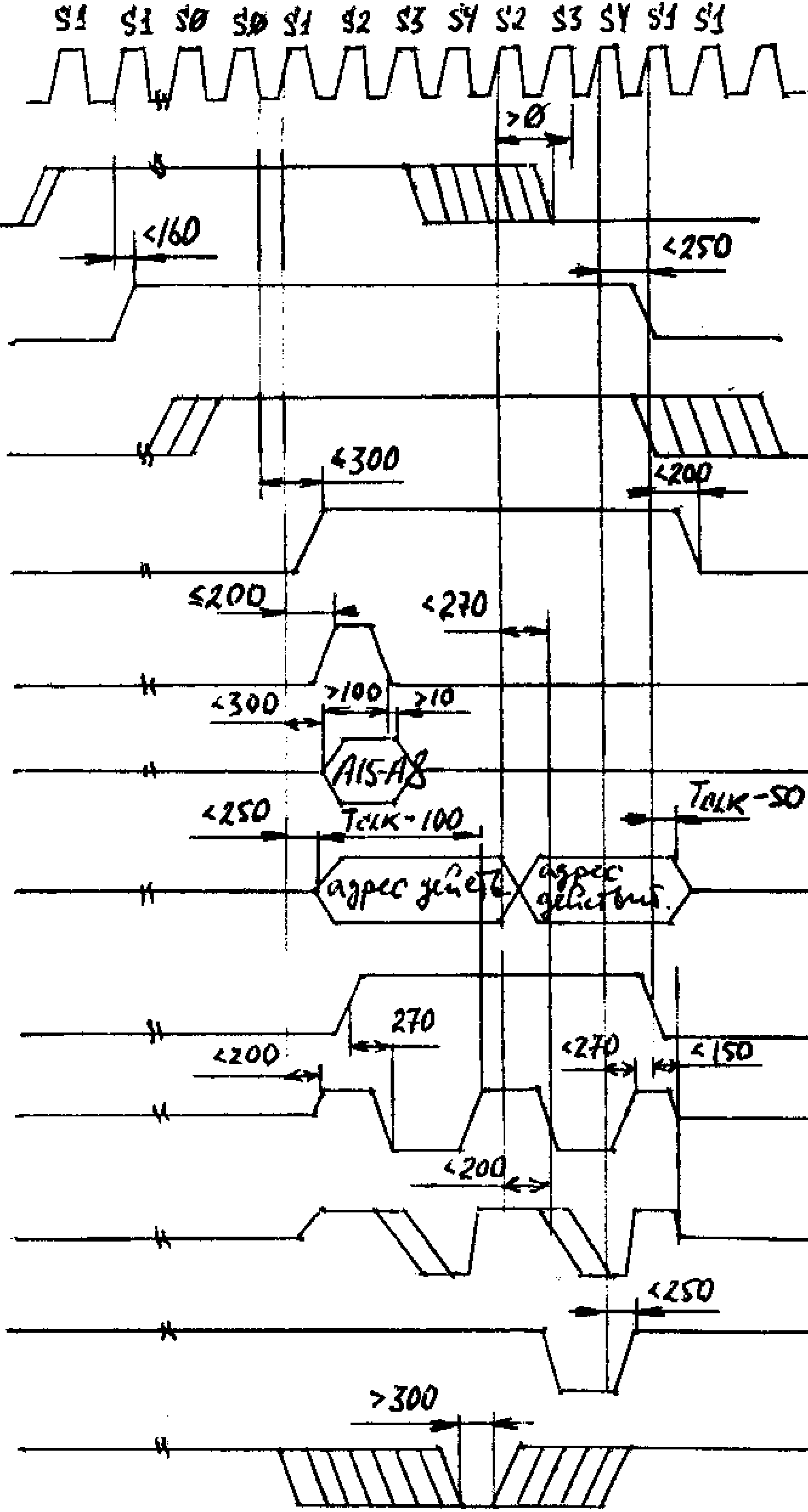

Рис. 21. Временная диаграмма работы DMAC i8237