Московский государственный технический университет им. Н. Э. Баумана

Елисеева о.И., Михайлов б.Б

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

К ВЫПОЛНЕНИЮ ЛАБОРАТОРНОЙ РАБОТЫ №3

Исследование микропроцессорного комплекта

серии К1804

по курсу «Элементы электроники и микропроцессорной

техники РТС»

2007 Г.

Цель работы: изучение архитектуры больших интегральных схем (БИС) микропроцессорного комплекта (МПК) серии К1804, основ микропрограммирования и принципов применения МПК серии К1804.

ТРЕБОВАНИЯ ПО ТЕХНИКЕ БЕЗОПАСНОСТИ

В работе исследуются характеристики БИС и функциональные особенности устройств, построенных на этих микросхемах, поэтому при работе на лабораторных стендах следует руководствоваться ГОСТ 12.3.019-80. «Испытания и измерения электрические. Общие требования безопасности».

К выполнению работ студенты допускаются только после проведения преподавателем инструктажа.

Перед выполнением работ необходимо:

осмотреть рабочее место и подготовить стенд к работе;

убедиться в наличии заземления стенда;

При выполнении работ необходимо:

поддерживать на рабочем месте чистоту и порядок, соблюдать осторожность и быть внимательным;

немедленно отключить стенд от питающей сети при появлении запаха гари, дыма, огня, необычного шума или вибрации, при искрении контактов.

ЗАПРЕЩАЕТСЯ:

приступать к работе без инструктажа по вопросам безопасности,

разрешения преподавателя и регистрации в специальном журнале;

включать силовые и осветительные рубильники;

оставлять без наблюдения работающий (включенный) стенд.

КРАТКИЕ ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ.

Процессоры с разрядно-модульной организацией (секционные) – это компромисс между универсальным микропроцессором с фиксированным набором команд и специализированным вычислителем, предназначенным для решения одной конкрентой задачи. Эти процессоры состоят из нескольких функциональных модулей, которые выполнены в виде больших интегральных схем. Обычно модули имеют невысокую разрядность (4 или 8). Для обработки многоразрядных чисел модули соединяют параллельно. Такой подход накладывает ограничения на возможные архитектуры процессора, которые можно реализовать из данного набора модулей, но позволяет существенно сократить количество используемых микросхем.

Процессор с разрядно-модульной организацией состоит из двух основных блоков: операционного блока и блока управления. Первый обеспечивает преобразование данных, второй формирует адрес, по которому из памяти микропрограмм выбирается текущая микрокоманда.

Упрощенно связь между блоками показана на рис.1.

Рис. 1. Формирование адреса микрокоманды

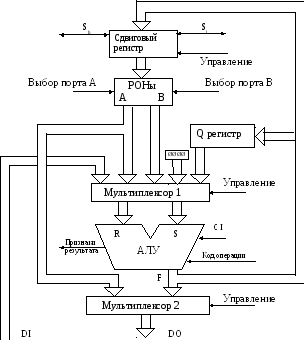

Операционный блок. Упрощенная структурная схема блока приведена на рис. 2. Именно в этом блоке осуществляются все операции над данными: арифметические, логические и т. п. Основными элементами блока являются арифметически-логическое устройство (АЛУ) и регистры общего назначения (РОН). В состав операционного блока входят также регистры, мультиплексоры, другие вспомогательные элементы.

Арифметически-логическое устройство данного блока может выполнять 8 операций, поэтому в микрокоманде для управления АЛУ отведено 3 разряда. Более мощные процессоры выполняют до 32-х операций. Результат работы АЛУ может быть либо сохранен во внутренних регистрах блока, либо выдан на выход операционного блока. Для этого используют мультиплексор 2, управление которым осуществляется специальным разрядом микрокоманды. Входными операндами АЛУ могут быть:

данные, записанные в РОНах,

информация со входа операционного блока,

содержимое рабочего регистра (Q-регистра),

нулевой операнд.

Операнды выбирают с помощью мультиплексора 1.

Регистры общего назначения представляют собой 16 четырехразрядных регистра. Доступ к этим регистрам возможен с помощью двух независимых портов А и В. Поэтому в составе микрокоманды имеется 8 разрядов (2*4), отводимых для обращения к РОНам.

Сдвиговый регистр операционного блока обеспечивает сдвиг занесенной информации на один разряд влево или вправо. Возможна также организация сдвига двойной длины (двойной сдвиг) путем последовательного соединения этого регистра с регистром Q. Для управления сдвиговыми операциями в микрокоманде отведены два специальных разряда.