МОСКОВСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ

УНИВЕРСИТЕТ имени Н.Э.БАУМАНА

Кафедра РК-10

О.И.Елисеева, Б.Б.Михайлов

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

К ВЫПОЛНЕНИЮ ЛАБОРАТОРНОЙ РАБОТЫ №5

«Исследование однокристального микропроцессора К1810ВМ86»

по курсу «Элементы электроники и микропроцессорной

техники РТС»

Москва

2009 г.

Краткое описание микропроцессора К1810ВМ86

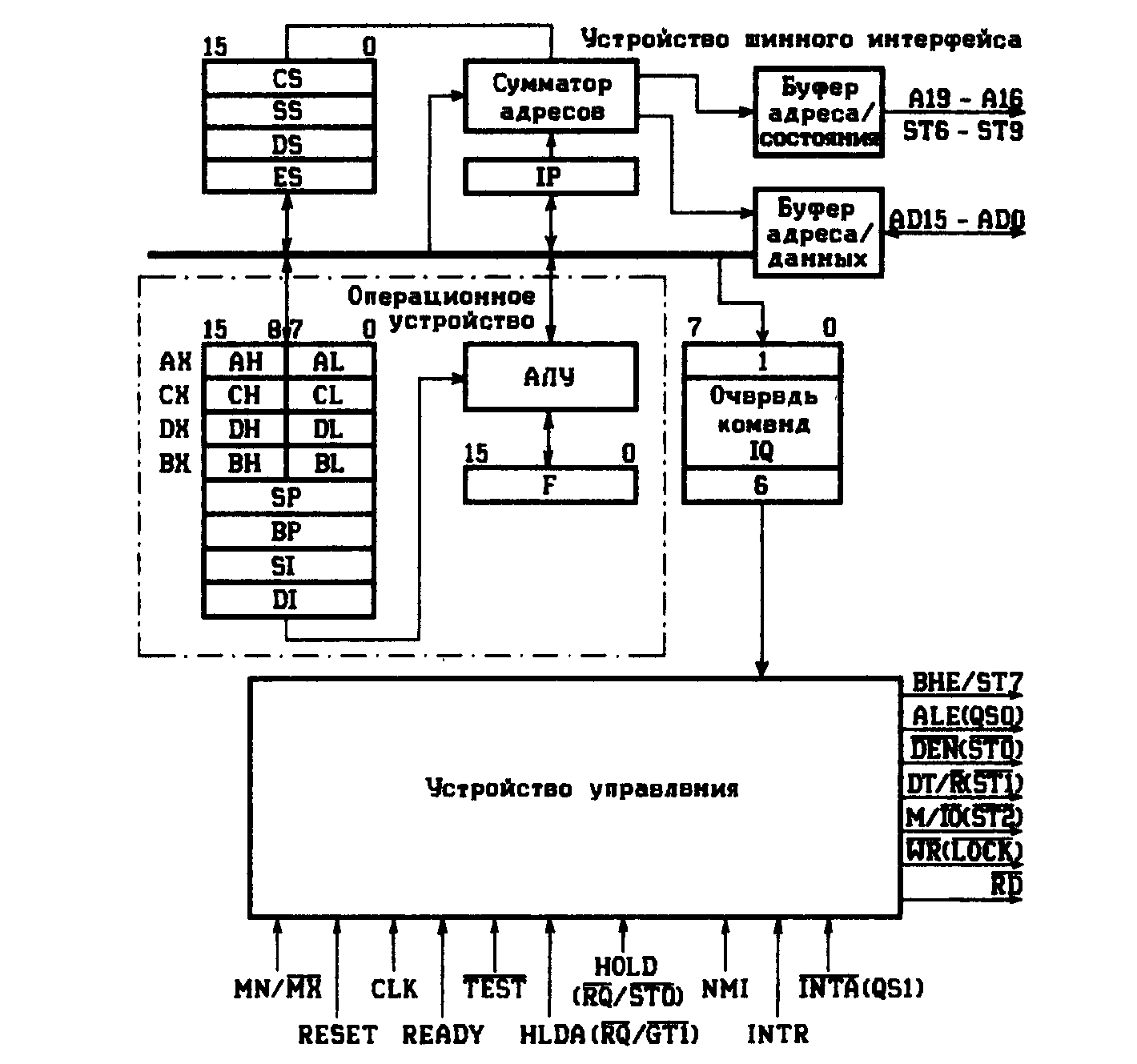

Микропроцессор имеет разрядность шины данных 16 бит, шины адреса 20 бит. Схема процессора представлена на рис.1:

Рис.1

В процессоре имеется восемь 16-разрядных регистров общего назначения:

AX – аккумулятор,

BX – базовый регистр,

CX – счетчик,

DX – регистр данных,

SP – указатель стека,

BP – указатель базы,

SI – индекс источника,

DI – индекс приемника.

Обычно регистры AX, BX, CX и DX используются для хранения данных, регистры SP, BP, SI, DI - для адресной информации. Для регистров AX, BX, CX, DX возможно также раздельное использование младших и старших байтов (AH, AL, BH, BL, CH, CL, DH, DL).

Регистр SP (Stack Pointer) представляет собой указатель стека (содержит текущее значение вершины стека), регистр BP (Base Pointer) используется при некоторых специальных формах адресации данных. Регистры SI и DI применяются при работе с так называемыми строками - последовательностями байтов или слов. Регистр SI (Source Index) указывает на текущий обрабатываемый элемент исходной строки (строки-источника), а DI (Destination Index) - на элемент результирующей строки (строки-приёмника).

Регистр флагов F:

|

FH |

FL |

||||||||||||||

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

x |

x |

x |

x |

OF |

DF |

IF |

TF |

SF |

ZF |

x |

AF |

x |

PF |

x |

CF |

Арифметические флаги:

CF – флаг переноса, фиксирует значение переноса из старшего бита результата при сложении, либо заема при вычитании, а также значение выдвигаемого бита при сдвиге операнда

PF – флаг паритета, фиксирует четное число единиц в младшем байте результата

AF – флаг вспомогательного переноса, фиксирует перенос из младшей тетрады (используется при выполнении десятичной коррекции)

ZF – флаг нулевого результата

SF – флаг знака, равен старшему разряду результата при работе со знаковой арифметикой

OF – флаг переполнения

Флаги управления:

DF – флаг направления обработки цепочек команд: DF=0 – в сторону больших адресов, DF=1 – в сторону меньших.

IF – флаг разрешения прерываний: IF=0 прерывания запрещаются, IF=0 – разрешаются.

TF – флаг трассировки: TF=1 – пошаговый режим работы.

Блок сегментных регистров состоит из четырех 16-разрядных регистров CS, SS, DS, ES, которые хранят базовые адреса сегментов памяти: CS – сегмент команд, SS – сегмент стека, DS – сегмент данных, ES – дополнительный сегмент (обычно также используется для хранения данных).

Указатель команд IP хранит смещение следующей команды в текущем кодовом сегменте.

Организация памяти в процессоре

Память представляет собой набор последовательно расположенных байтов, каждый из которых имеет 20-разрядный адрес. Два смежных байта могут рассматриваться как 16-битное слово, адресом слова считается адрес младшего байта (он меньше, чем адрес старшего байта). Адресное пространство имеет емкость 1 Мбайт и разбито на сегменты емкостью 64 Кбайт, которые характеризуются базами. Начальные адреса четырех текущих сегментов записываются в сегментные регистры CS, SS, DS, ES; для перехода к другой области памяти достаточно сменить содержимое сегментного регистра.

Каждая ячейка памяти характеризуется логическим и физическим адресом. Физический адрес представляет собой 20-разрядное число, однозначно определяющее положение ячейки в памяти. Логический адрес ячейки состоит из двух 16-битовых значений: базы сегмента и смещения внутри сегмента относительно базы (определяет расстояние от начала сегмента до этой ячейки). Для пересчета логического адреса в физический база сегмента сдвигается влево на 4 бит и суммируется со смещением. Если при суммировании возникает бит переноса, он игнорируется; таким образом, после ячейки памяти с адресом FFFFF идет ячейка с адресом 00000, то есть возникает кольцевая организация памяти (она также присуща каждому сегменту в отдельности).

Обращение к памяти.

К каждому сегменту памяти обращение осуществляется отдельно. Прямая передача информации между сегментами невозможна, для этого необходимо использовать регистры общего назначения.

Для обращения к памяти используются 4 регистра: BX, SI, DI, BP, а также смещение, задаваемое непосредственной величиной: d8 – 8 бит или d16 – 16 бит. Комбинируя эти регистры и смещения внутри квадратных скобок [ ], можно задействовать любую ячейку памяти.

|

r/m |

md=00 |

md=01 |

md=10 |

|

000 001 010 011 |

[BX + SI] [BX + DI] [BP + SI] [BP + DI] |

[BX + SI + d8] [BX + DI + d8] [BP + SI + d8] [BP + DI + d8] |

[BX + SI + d16] [BX + DI + d16] [BP + SI + d16] [BP + DI + d16] |

|

100 101 110 111 |

[SI] [DI] d16 [BX] |

[SI + d8] [DI + d8] [BP + d8] [BX + d8]

|

[SI + d16] [DI + d16] [BP + d16] [BX + d16] |

Для примера примем DS=100, BX=30, SI=70. В этом случае адрес [BX+SI]+25 будет преобразован процессором в следующий физический адрес: 100*16+30+70+25=1725.

По умолчанию сегментный регистр DS используется всегда, кроме режимов с регистром BP, в этом случае используется сегментный регистр SS. Адреса задаются в шестнадцатеричном коде.

Структура команд процессора

Двухоперандные команды:

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Код операции |

d |

s |

md |

reg |

r/m |

||||||||||

|

disp L |

disp H |

||||||||||||||

Бит d указывает направление передачи: d=1 – передача операнда или результата операции в регистр, указанный в поле reg, d=0 – передеча из регистра reg. Бит s показывает формат данных: s=1 – слово, s=0 - байт

Поле reg определяет второй операнд, обязательно находящийся в регистре; поле r/m (регистр/память) определяет первый операнд, который может находиться в регистре или памяти.

|

reg, r/m |

s=0 |

s=1 |

reg, r/m |

s=0 |

s=1 |

|

000 |

AL |

AX |

100 |

AH |

SP |

|

001 |

CL |

CX |

101 |

CH |

BP |

|

010 |

DL |

DX |

110 |

DH |

SI |

|

011 |

BL |

BX |

111 |

BH |

DI |

Поле md показывает, содержится первый операнд в памяти или в регистре, а в случае расположения операнда в памяти определяет вариант использования смещения disp, которе может находиться в третьем и четвертом байтах команды:

md=00 – операнд содержится в памяти, disp=0 (смещение отсутствует)

md=01 – операнд содержится в памяти, disp=disp L (команда содержит 8-битовое смещение, которое расширяется со знаком до 16 бит)

md=10 – операнд содержится в памяти, disp=disp H, disp L (команда содержит 16-битовое смещение)

md=11 – операнд содержится в регистре

Однооперандные команды:

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Код операции |

s |

md |

Код операции |

r/m |

|||||||||||

|

disp L |

disp H |

||||||||||||||

Могут содержать от 2хдо 4х байт в зависимости от s и md

Команды с непосредственной адресацией:

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Код операции |

s |

w |

md |

Код операции |

r/m |

||||||||||

|

disp L |

disp H |

||||||||||||||

|

data L |

data H |

||||||||||||||

Могут содержать до 3х слов. Поля s и w показывают, как используются последние 2 байта команды:

|

s |

w |

|

|

x |

0 |

data=data L (8 разрядов) |

|

0 |

1 |

data=data H, dataL (16 разрядов) |

|

1 |

1 |

data=data L (расширение до 16-разрядного слова со знаком) |