- •Лекция 11. Матричные вычислительные системы

- •Обобщенная модель матричной вс

- •Интерфейсная вм

- •Контроллер массива процессоров

- •Контроллер массива процессоров

- •If a (условиеA) then do в

- •Массив процессоров

- •Архитектура типа «процессорный элемент - процессорный элемент»

- •Архитектура типа «процессор-память»

- •Структура процессорного элемента

- •Структура процессорного элемента

- •Подключение и отключение процессорных элементов

- •Сети взаимосвязей процессорных элементов

- •Функциональная структура системы illiac IV

- •Структура межпроцессорных связей в illiaciv

- •Ассоциативная память

- •Структура ассоциативного зу

- •Ассоциативные вс

- •Систолические структуры

- •Классификация систолических структур

Сети взаимосвязей процессорных элементов

Эффективность сетей взаимосвязей процессорных элементов во многом определяет возможную производительность всей матричной системы. Применение находят самые разнообразные топологии сетей.

Поскольку процессорные элементы в матричных системах функционируют синхронно, обмениваться информацией они также должны по согласованной схеме, причем необходимо обеспечить возможность синхронной передачи от нескольких ПЭ-источников к одному ПЭ-приемнику. Когда для передачи информации в сетевом интерфейсе задействуется только один регистр пересылки данных, это может привести к потере данных, поэтому в ряде ВС для предотвращения подобной ситуации предусмотрены специальные механизмы. Так, в системе СМ-2 используется оборудование, объединяющее сообщения, поступившие к одному ПЭ.

В некоторых SIMD-системах, например МР-1, имеется возможность записать одновременно пришедшие сообщения в разные ячейки локальной памяти.

Хотя пересылки данных по сети инициируются только активными ПЭ, пассивные процессорные элементы также вносят вклад в эти операции. Если активный ПЭ инициирует чтение из другого ПЭ, операция выполняется вне зависимости от статуса ПЭ, из которого считывается информация. То же самое происходит и при записи.

Наиболее распространенными топологиями в матричных системах являются решетчатые и гиперкубические. Так, в ILLIAC IV, МРР и СМ-2 каждый ПЭ соединен с четырьмя соседними. В МР-1 и МР-2 каждый ПЭ связан с восьмью смежными ПЭ. В ряде систем реализуются многоступенчатые динамические сети соединений (МР-1, МР-2, GF11).

ВС ILLIAC IV

Матричная система ILLIAC IV (ILLInois Automated Computer) создана Иллинойским университетом и корпорацией Бэрроуз (Burroughs Corporation). Она разрабатывалась с 1966 и в 1972 система эксплуатировалась в Научно-исследовательском центре НАСА (NASA – National Aeronautics and Space Administration – Национальное управление аэронавтики и космоса).

Количество процессоров в системе – 64; быстродействие – 2*108 опер./с; емкость оперативной памяти – 1 М байт; полезное время составляет 80-85% общего времени работы ILLIAC IV, стоимость 40 000 000 долл., вес 75 т, занимаемая площадь 930 м2.

Система ILLIAC IV была включена в вычислительную сеть ARPA (Advanced Research Projects Agency – Управление перспективных исследований и разработок Министерства обороны США) и успешно эксплуатировалось до 1981 г.

Функциональная структура системы illiac IV

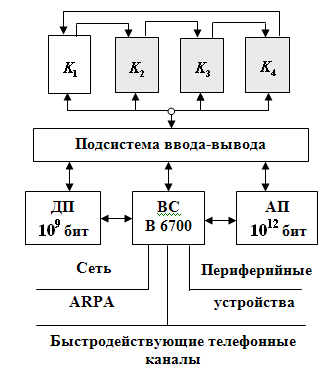

Матричная вычислительная система ILLIAC IV должна была состоять из 4 квадрантов (К1–К4), подсистемы ввода-вывода информации, ведущей ВС B 6700 (или B 6500), дисковой памяти (ДП) и архивной памяти (АП). Планировалось, что ВС обеспечит быстродействие 109 опер./с. В реализованном варианте ILLIAC IV содержался только один квадрант, что обеспечило быстродействие 2*108 опер./с. При этом ILLIAC IV оставалась самой быстродействующей вычислительной системой вплоть до 80-х годов 20 столетия.

Квадрант – матричный процессор, включавший в себя устройство управления и 64 элементарных процессора. Устройство управления представляло собой специализированную ЭВМ, которая использовалась для выполнения операций над скалярами и формировала поток команд на матрицу ЭП. Элементарные процессоры матрицы регулярным образом были связаны друг с другом. Структура квадранта системы ILLIAC IV представлялась двумерной решеткой, в которой граничные ЭП были связаны по канонической схеме (циркулянтным графом), которую можно изобразить в виде плоской решетки, где узлы в каждом столбце замкнуты в кольцо, а узлы в последовательных рядах соединены в замкнутую спираль. Второй вариант представления – хордальное кольцо с шагом хорды равном 4.

Каждый ЭП имел:

накапливающий сумматор (64 разряда),

регистр второго операнда (64 разряда),

регистр передаваемой информации (из данного ЭП в соседний ЭП) (64 разряда),

регистр, использовавшийся как временная память (64 разряда),

регистр модификации адресного поля команды (16 разрядов),

регистр состояния данного ЭП (8 разрядов).