- •Пояснительная записка

- •1.4.2. Диапазон и погрешность представления чисел

- •1.4.3. Форматы команд, данных и слова состояния процессора

- •1.4.4. Организация виртуальной памяти

- •1.4.5. Способы организации ввода-вывода информации

- •1.4.6. Способ оценки производительности эвм

- •1.4.7. Приращение производительности эвм

- •2.2. Функциональная модель эвм

- •2.3. Алгоритм функционирования эвм

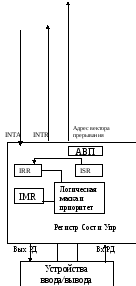

- •2.4. Средства управления прерываниями

- •2.5. Организация виртуальной памяти

- •Алгоритм работы виртуальной памяти

- •2.6. Оценка производительности эвм

- •3. Модификация созданной эвм

- •3.1. Возможности повышения производительности эвм

- •3.2. Организация конвейерной обработки команд

- •3.3. Расчет прироста производительности эвм

- •4. Тестовая задача

- •4.1. Алгоритм и программа для тестирования эвм

- •4.2. Моделирование процесса выполнения программы

- •5. Программирование ввода и вывода

- •5.1. Пример использования системных функций для ввода

- •5.2. Общие сведения об интерфейсе Win32 api

2.2. Функциональная модель эвм

Изобразим основные регистры и связи между ними, управляемые сигналами, поступающими из центрального устройства управления (УУ процессора). В алгоритме функционирования УУ процессора, описываемом на следующем этапе проектирования, предусматривается проверка значений признаков, поступающих на входы УУ процессора от исполнительных устройств и формирование управляющих сигналов, подаваемых на исполнительные устройства. Инициирование процесса формирования управляющих сигналов в УУ процессора осуществляется оператором путем установки триггера пуска (Тп) в единичное состояние. При переводе указанного триггера Тп в нулевое состояние УУ процессора проектируемой ЭВМ перестают формировать управляющие сигналы, ожидая появления единичного состояния триггера пуска Тп.

Приведенная на рис.2 модель содержит типовой набор регистров и устройств, обеспечивающих реализацию программного принципа управления.

Ready

ALU

ШД

Ready

ALU

ШД

Y10

S

ША

Y10

S

ША

R

T ALU

ШК

R

T ALU

ШК

Y11 Y11

Y7

А

LU

ОУ

ALU RD RA

LU

ОУ

ALU RD RA

Pi

Pi

Акк

Y6 Y9

V1

Акк

Y6 Y9

V1

Y5

IP

Y5

IP

SF

SF S V2

Y2

SF

SF S V2

Y2

ZF

FR ZF Z

ZF

FR ZF Z

OF

OF O Y8

OF

OF O Y8

STI

IF IF I

STI

IF IF I

CLI

CLI

Y4

Y4

Ready RAM

Ready RAM

RI КОП СА А

IRQ

АО

АО

ЧТ

INTR WR RAM режим

ЧТ

INTR WR RAM режим

DС

ЗП

DС

ЗП

…УУ

Процессора RD

RAM

режим

…УУ

Процессора RD

RAM

режим

Y0

Y0

INTA

G

… Y10

G

… Y10

Пуск

Пуск

S

S

Тп

Тп

1 E R

E R

Рис.2 Регистровая модель гипотетического CPU

Y3

Далее приводятся пояснения некоторых обозначений, используемых для предоставления регистровой модели CPU.

Yi – сигналы, которые вырабатываются УУ процессора, подаются на исполнительные устройства.

Ai – сигналы, управляющие функционированием арифметических блоков.

RD – регистр данных, на который поступает содержимое ячеек основной памяти.

RA – регистр адреса памяти.

IP – регистр - указатель адреса очередной команды.

IR – регистр для хранения текущей команды.

RO, Акк – регистры для хранения обрабатываемых операндов.

ALU – арифметико-логическое устройство, управляемое локальным устройством УУ ALU, функционирование которого инициирует УУ процессора. Взаимодействие названных устройств управления осуществляется с помощью триггера TALU, единичное состояние которого свидетельствует о функционировании ALU (Ready ALU).

Ready RAM - единичное значение этого сигнала свидетельствует о функционировании основной памяти в режиме записи или чтения.

INTA – сигнал подтверждения прерывания

INTR – сигнал о передаче вектора прерывания

АВП – адрес вектора прерывания, адрес ячейки памяти, указывающий на программу обработки прерывания. В оперативной памяти хранится таблица векторов прерываний, а адрес вектора прерывания состоит из смещения и номера уровня запроса, по этим данным адрес.

Регистр Сост и Упр. – регистр состояния контроллера и управления передачи данных

Вых РД – выходной регистр данных

Вх РД – входной регистр данных

ISR – сброс

IRQ – информация, необходимая для идентификации внешнего устройства, содержится в регистре состояния и управления. Когда устройство генерирует запрос прерывания, оно устанавливает 1 в разряд IRQ.

Устройство ввода/вывода сообщает о себе: диапазон адресов ввода-вывода, диапазон используемых адресов оперативной памяти, номера прерываний и их количества, номера и количество адресов прямого доступа к памяти DMA.