- •Задание 1.

- •Теоретическая часть.

- •Практическая часть.

- •Машинные коды.

- •Теоретическая часть.

- •Арифметические действия в машинных кодах.

- •Практическая часть.

- •Теория.

- •Теоретическая часть.

- •Практическая часть.

- •2) Для кнф и днф из лабораторной работы 3 построить функциональные схемы.

- •/R/s-триггер

- •Rs-триггер

- •D-Триггер

- •T-Триггер

- •Jk-Триггер

- •Полусумматор

- •Дешифратор

- •Шифратор

- •Компаратор

Полусумматор

Полусумматор — это узел, имеющий два входа и два выхода и выполняющий операцию арифметического сложения двух одноразрядных чисел А и В в соответствии со следующим правилом:

при любых наборах сигналов А и В на выходе сигнала суммы S формируется результат сложения по модулю 2, на выходе сигнала переноса Р во всех случаях будет 0, кроме А=В=1, когда Р'=1.

Таблица истинности:

|

А |

В |

S |

P |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

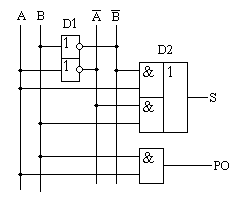

В соответствии с принципами построения

произвольной таблицы истинности получим

схему полусумматора. Эта схема приведена

на рисунке 1.

соответствии с принципами построения

произвольной таблицы истинности получим

схему полусумматора. Эта схема приведена

на рисунке 1.

Рисунок 1 Принципиальная схема, реализующая таблицу истинности полусумматора.

Полусумматор изображается на схемах как показано на рисунке 2.

Рисунок 2 Изображение полусумматора на схемах.

Дешифратор

Дешифраторы (ДШ) - это комбинационные схемы с п входами и m =2n выходами. Единичный сигнал, формирующийся на одном из т выходов, однозначно соответствует комбинации входных сигналов.

Таблица истинности дешифратора

|

Входы |

Выходы | |||||||

|

x1 |

x2 |

x3 |

Y0 |

Y1 |

... |

Y5 |

... |

Y7 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

|

0 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

|

0 |

|

0 |

1 |

0 |

0 |

0 |

|

0 |

|

0 |

|

0 |

1 |

1 |

0 |

0 |

… |

0 |

... |

0 |

|

1 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

|

0 |

|

1 |

1 |

0 |

0 |

0 |

|

0 |

|

0 |

|

1 |

1 |

1 |

0 |

0 |

|

0 |

|

1 |

Д ешифраторы

широко используются в ЭВМ для выбора

информации па определенному адресу,

для расшифровки кода операции и др.

Логические зависимости дешифратора:

ешифраторы

широко используются в ЭВМ для выбора

информации па определенному адресу,

для расшифровки кода операции и др.

Логические зависимости дешифратора:

Н а

рис.3.2 представлены структурная схема

ДШ,

построенная в базисе (И, НЕ), и условное

ее обозначение на принципиальных

электрических схемах ЭВМ. Кружочки у

линий, выходящих из логических элементов,

указывают на инверсию функций, реализуемых

элементами.

а

рис.3.2 представлены структурная схема

ДШ,

построенная в базисе (И, НЕ), и условное

ее обозначение на принципиальных

электрических схемах ЭВМ. Кружочки у

линий, выходящих из логических элементов,

указывают на инверсию функций, реализуемых

элементами.

Рисунок3 Структурная схема дешифратора (а) и обозначение дешифратора на принципиальных электрических схемах (б)

Шифратор

Шифратор (ШР) решает задачу, обратную схемам ДТП, т. е. по номеру входного сигнала формирует однозначную комбинацию выходных сигналов. Пример построения ШР иллюстрируется таблицей истинности и схемами на рисунке 4.

Таблица истинности шифратора

|

Входы |

Выходы | ||||||||

|

x1 |

x2 |

x3 |

X4 |

x5 |

x6 |

x7 |

yo |

y1 |

y2 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

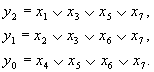

Л огические

зависимости:

огические

зависимости:

Рисунок 4 Структурная схема шифратора (а) и обозначение дешифратора на принципиальных электрических схемах (б)

Обратим внимание, что таблица истинности дешифратора и шифратора во многом похожи, входы и выходы в них поменялись местами. Состояния входов таблицы шифратора содержат только по одному единичному элементу. Другие произвольные комбинации входов недопустимы.