- •Лабораторная работа №3 Изучение триггеров

- •1. Краткие теоретические сведения.

- •1.2 Классификация триггеров.

- •2. Триггеры.

- •2.1.2 Создание принципиальной схемы

- •2.2 Синхронный rs-триггер

- •2.3 Универсальный jk-триггер.

- •3. Реализация схем, используя vhdl-программу, на примере d-триггера.

- •3.Задание к работе

- •Контрольные вопросы

2. Триггеры.

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельные или цифровые линии задержки.

2.1 RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер.

RS-триггер имеет два логических входа:

R - установка 0 (от слова reset);

S - установка 1 (от слова set).

RS-триггер имеет два выхода:

Q - прямой;

- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью (рис.2.)

Рис. 2 - Схема простейшего RS- триггера.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль =0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль - со входа R, другой - с выхода). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента. Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в "0". Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния.

Для описания работы триггера используют таблицу состояний (переходов).

Обозначим:

- Q(t) - состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) - состояние триггера после изменения на входах R и S.

Таблица 2 - Таблица переходов RS триггера в базисе ИЛИ-НЕ

R (S) |

S |

Q(t) |

Q(t+1) |

Пояснения |

0 |

0 |

0 |

0 |

Режим сохранения информации R=S=0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

Режим установки нуля R=1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

1 |

1 |

1 |

* |

2.1.2 Создание принципиальной схемы

В первую очередь следует запустить программу Xilinx. Создадим новый проект, задаем название FPGA_lab3. Вызываем мастер создания нового источника New Source Wizard, чтобы создать новую схему Schematic, необходимую для дальнейшей работы. Зададим имя нового модуля, File name – RS.

Нарисуем принципиальную схему триггера (рис.3.)

Рис. 3

Создаем отдельный элемент RS-триггера (рис 4). Для этого выбираем Symbol Wizard в меню Tools. Выбрав необходимые настройки, в итоге создается элемент RS.

Рис. 4. Элемент RS-триггер.

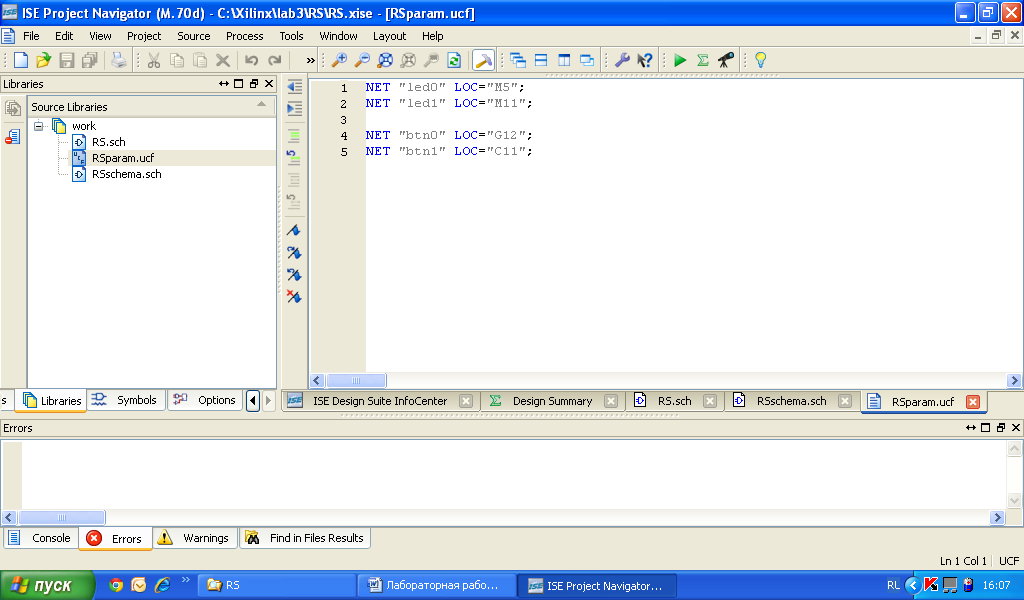

Осталось создать файл param с расширением *.ucf. В нём пропишем привязку выводов проекта к входам-выводам кристалла (рис.5).

Рис. 5

RS-триггер можно построить и на элементах "И-НЕ" (рис. 6).

Рис. 6 - Схема RS-триггера, построенного на схемах "И-НЕ"

Условное графическое обозначение RS-триггера представлено на рис.7.

Рис. 7

Входы R и S инверсные (активный уровень "0"). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов "0". Комбинация R=S=0 является запрещённой.

Таблица 3 - Таблица переходов RS триггера в базисе "И-НЕ"

R (S) |

S |

Q(t) |

Q(t+1) |

Пояснения |

0 |

0 |

0 |

* |

Режим сохранения информации R=S=0 |

0 |

0 |

1 |

* |

|

0 |

1 |

0 |

0 |

Режим установки единицы S=1 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

Режим установки нуля R=1 |

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

R=S=1 запрещенная комбинация |

1 |

1 |

1 |

1 |

Далее проведём запуск автоматизированного размещения проекта в кристалле и анализ генерируемых отчетов для выявления предупреждений и ошибок, а при отсутствии таковых и не критичных переходим к следующему этапу. Верификация проекта, т. е. окончательное временное моделирование (Post-Fit Simulation) после размещения проекта в кристалле при всех реальных задержках распространения сигналов внутри микросхемы ПЛИС.

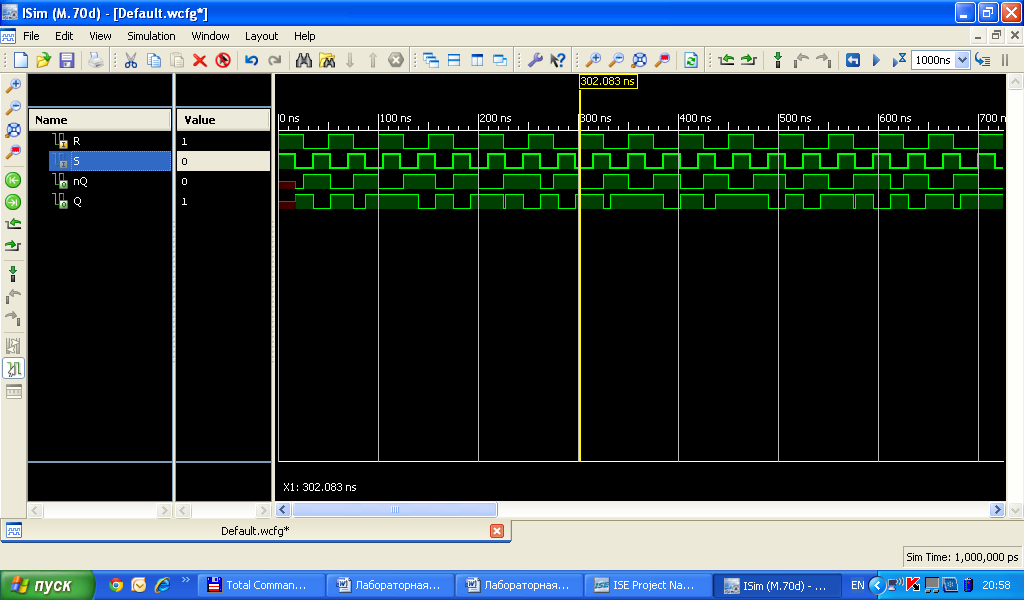

Для проверки работоспособности схемы RS- триггера проведем симулирование работы с помощью ISim, для этого в режиме симуляции выделяется исследуемая схема и запускается ISim Simulator.

В меню настройки входных сигналов необходимо указать параметры сигналов поступающих на входы R и S. Оба входа данного типа триггера являются информационными. Пример параметров изображен на рис. 8.

а б

Рис. 8. Пример параметров входных сигналов RS-триггера.

Рис. 9. Симуляция работы RS-триггера

По итогам симулирования работы схемы RS-триггера получены зависимости выходных импульсов от входных сигналов. Сравнив полученные данные с таблицей истинности, представленной в литературе, можно сделать выводы о правильности работы схемы.