- •3 Група індексних регістрів та вказівників які утворюють регістри т

- •5 Регістр вказівника (лічильника) команд еір призначений для адресації в середині "поточного сегмента коду Вказівник команди прямо у командах ие вказується, але бере

- •6 Регістр прапорців ерьаоз зберігає інформацію про ознаки результату

- •Способи адресування в мікропроцесорах сімейства іьггеь. Навести приклади.

- •2.2.6 Пряме адресування з індексуванням

- •6 Прерывания

- •Сегменгування пам'яті в мікропроцесорах сімейства интел

- •2.1 Сегментування пам'яті

- •Способи обміну інформацією у мікропроцесорній системі. Області застосування. Приклади реалізації

- •2.2 Особливості архітектури окремих процесорів сім'ї Интел 2.2-1 Мікропроцесор 18086

- •2Р(6) - прапорець нульового результату, встановлюється в 1, коли результат операції дорівнює о,

- •2.2.2 Мікропроцесор 180186

- •2.2.3 Мікропроцесор 180286

- •2.2.4 Мікропроцесори 180386 та 180486

2.2.6 Пряме адресування з індексуванням

При прямому адресуванні з індексуванням ефективна адреса обчислюється як сума зміщення та вмісту індексного регістра. Цей тип адресування зручний для доступу до елементів масиву у сегменті даних, коли мітка визначає перший елемент масиву, а вміст індексного регістра вказує на потрібний елемент. Наприклад: при виконанні команди

МОУ АХ, ТАВ \Т>1]

завантаження до АХ елемента масиву, номер якого визначається [ЛІ], якщо (ТЛ] дорівнює 4Н, до АХ буде завантажений третій двобайтовий елемент масиву з комірок пам'яті з ефективними адресами 0005Н та 0006Н. Якщо ж масив складається з однобайтових даних, то для адресації третього елемента масиву в регістр 0

1 треба завантажити число 2Н Замість мітки ТАВ у команді може бути вказане зміщення відносно початку сегмента даних. Наприклад, команда

МОУАХ, [ВІ+01Н]

завантажує до АХ два байти даних з масиву за ефективною адресою, що обчислюється як сума вмісту регістра ОІ та зміщення 01Н відносно початку сегмента, а команда:

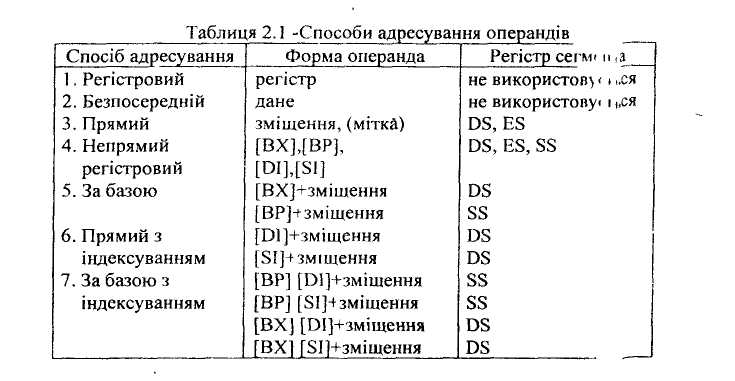

У таблиці 2.1 наводяться основні способи

адресування та наїіш регістрів, що

беруть участь у формуванні ефективної

адреси операндів у проіидорах

k

INTEL

таблиці 2.1 наводяться основні способи

адресування та наїіш регістрів, що

беруть участь у формуванні ефективної

адреси операндів у проіидорах

k

INTEL

Концепція переривань Види переривань.

Билет 6

Концепция прерываний и виды прерываний

Прерывания в МПС могут быть

6 Прерывания

маскируемые и не маскируемые

Аппаратные и программные

Внутренние и внешние

INT2 –интерфейс прерываний –это немаскируемое внешнее прерывания которое возникает при пропадании питания в случае ошибки в магистрали , или сбоев в памяти

INT 0 – внутреннее прерывание возникает в процессоре в случае ошибки деления

INT 1- прерывание в пошаговом режиме, в в компютере сопровождается выдачей на монитор содержимого всех регистров

INT3 сопровождается выдачей регистра процессора при работе в составе компютера

INT 4 – (INT0) прерывание при переполнении

Все остальные вплоть до 255 либо зарезирвированы фирмой либо представлены для свободного пользования пользователю

С этими прерывания ми могут осуществлятся переходы на подпрограммы обработки прерываний -которые предназначенны для стандартных внешних устройств могут быть по сути до 255 внешних устройств которые могут запросить прерывания одновременно во избежании этого конфликта каждому устройству предназначен свой приоритет приоритет азначается программно через контролер прерываний

Высший приоритет как правильно нулевой

Как правило контролеры программируются , так что отдельные внешние устройства маскируются это означает что их работа и реакция на запрос к прерываниям запрещается

Сегменгування пам'яті в мікропроцесорах сімейства интел

2.1 Сегментування пам'яті

Мікропроцесори сім'ї ПМТЕЬ призначені для роботи у складі комп'ютерів, що працюють у мультизадачному режимі, та у складі багатопроцесорних систем, де усі процесори можуть звертатися до загального запам'ятовуючого пристрою. Саме ці обставини призвели до способу організації пам'яті з кількох сегментів, кожний з яких має своє функціональне призначення: сегмент кодів, сегмент даних, сегмент стека, кілька додаткових сегментів даних залежно від моделі МП.

Мікропроцесори 18086, 18088, 180826 у реальному режимі , 180386 та 180486 у віртуальному режимі У86 програмно сумісні та можуть адресувати 1Мбайт фізичної пам'яті. Розмір сегмента становить 64 Кбайти. Сегменти можуть бути суміжними, розділеними, перекриватися повністю або частково.

Початкова адреса, тобто найменша адреса у цьому сегменті, вміщується у відповідні сегментні регістри, може встановлюватися робочою програмою та завжди починається з 16 байтової границі, наприклад,.0000Н, 7000Н.

Сегментні регістри мають 16 розрядів і доступні програмно через команди пересилань типу МОУ та РОР. Вони мають цільове призначення і не можуть виконувати функції регістрів загального призначення в арифметичних і логічних операціях.

Регістр сегмента команд С8 - керуючий регістр, що вказує сегмент, який вміщує адресу поточно виконуваної команди. Його вміст може бути змінений тільки при виконанні команд переходів, зверненні до підпрограм, поверненні з підпрограм або перериваннях зі зазначенням іншого сегмента команд.

Регістр сегмента даних О8 - керуючий регістр, що вказує сегмент, який вміщує програмно змінювані таблиці, масиви даних та константи. Така організація, за якої дані групуються разом в окремому сегменті, полегшує програмування. Усі прямі та непрямі засоби адресації даних, що використовують регістри ВХ, 81 або Ш, визначаються відносно регістра Б8.

Регістр сегмента стека 88 - керуючий регістр, вміст якого вказує початок стекової пам'яті (вершину). Вміст регістрів 5Р або ВР може використовуватись для зазначення відносних адреаі,переходів, які формуються за участю цих регістрів, або адрес відносно регіетра 88.

Регістр додаткового сегмента даних Е8, а також додаткових сегментів у МП 180386 та 180486, Р8 та С8 - керуючі регістри. Вміст цих регістрів вказує на початок області пам'яті, яка звичайно використовується для запам'ятовуванняпроміжних результатів, тобто рооочоі області пам яті. При необхідності використання додаткових сегментних регістрів використовуються команди з префіксом заміни сегмента, наприклад, команда

МОУАХ, Е5:[100]

звертається до додаткового сегмента даних, базова адреса якого знаходиться у регістрі Е5.

Вказівник команд ЇР- регістр, що виконує роль лічильника команд. Його вміст вказує адресу наступного байта команди у сегменті пам'яті, що визначається вмістом регістра сегмента команд С8. Вміст регістрів ІР та С8 однозначно визначає адресу байта в усьому адресному просторі. Вміст регістра ІР можна змінити тільки при виконанні команд переходів, виклику та поверненні з підпрограм та перериваннях.