- •Техническая Электроника

- •Оглавление

- •Предисловие

- •Введение

- •Глава 1 пассивные компоненты электронных устройств

- •1.1. Резисторы

- •Числовые коэффициенты первых трех рядов

- •Допустимые отклонения сопротивлений

- •Основные параметры резисторов

- •1.1.1. Система условных обозначений и маркировка резисторов

- •Специальные резисторы

- •1.2. Конденсаторы

- •1.2.1. Система условных обозначений конденсаторов

- •1.2.2. Параметры постоянных конденсаторов

- •1.2.3. Конденсаторы переменной ёмкости

- •1.3. Катушки индуктивности

- •Параметры катушек индуктивности

- •Глава 2 полупроводниковые диоды

- •2.1. Физические основы полупроводниковых приборов

- •2.2. Примесные полупроводники

- •2.3. Электронно-дырочный переход

- •2.4. Физические процессы в p–n переходе

- •2.5. Контактная разность потенциалов

- •2.6. Прямое включение p–n перехода

- •2.7. Обратное включение p–n перехода

- •2.8. Вольт–амперная характеристика p–n перехода

- •2.9. Пробой p–n перехода

- •2.10. Емкостные свойства p–n перехода

- •2.11. Полупроводниковые диоды

- •Система обозначения полупроводниковых диодов

- •2.12. Выпрямительные диоды

- •Параметры выпрямительных диодов

- •2.13. Стабилитроны

- •Параметры стабилитрона

- •2.14. Варикапы

- •Параметры варикапов

- •2.15. Импульсные диоды

- •Параметры импульсных диодов

- •2.15.1. Диоды с накоплением заряда и диоды Шотки

- •2.16. Туннельные диоды

- •Параметры туннельных диодов

- •2.17. Обращенные диоды

- •Глава 3 биполярные транзисторы

- •3.1. Режимы работы биполярного транзистора

- •3.2. Принцип действия транзистора

- •3.3. Токи в транзисторе

- •3.4. Статические характеристики

- •3.4.1. Статические характеристики в схеме с об входные характеристики

- •Выходные характеристики

- •Характеристики прямой передачи

- •Характеристики обратной связи

- •3.5. Статические характеристики транзистора в схеме с оэ

- •3.6. Малосигнальные параметры Дифференциальные параметры транзистора

- •Система z–параметров.

- •Система y–параметров

- •Система h–параметров

- •Определение h–параметров по статическим характеристикам

- •3.7. Малосигнальная модель транзистора

- •3.8. Моделирование транзистора

- •3.9. Частотные свойства транзисторов

- •3.10. Параметры биполярных транзисторов

- •Глава 4 полевые транзисторы

- •4.1. Полевой транзистор с управляющим p-n переходом

- •Статические характеристики

- •4.2. Полевые транзисторы с изолированным затвором

- •4.2.2. Статические характеристики мдп-транзистора с

- •4.3. Полевые транзисторы со встроенным каналом

- •4.4. Cтатические характеристики транзистора со

- •4.5. Cпособы включения полевых транзисторов

- •4.6. Полевой транзистор как линейный четырехполюсник

- •4.7. Эквивалентная схема и частотные свойства

- •4.8. Основные параметры полевых транзисторов

- •Глава 5 полупроводниковые переключающие приборы

- •5.1. Диодный тиристор

- •5.2. Триодный тиристор

- •5.3. Симметричные тиристоры (симисторы)

- •5.4. Параметры тиристоров

- •Глава 6 электронно-лучевые приборы

- •6.1. Электростатическая система фокусировки луча

- •6.2. Электростатическая отклоняющая система

- •6.3. Трубки с магнитным управлением электронным лучом

- •6.4. Экраны электронно-лучевых трубок

- •6.5. Система обозначения электронно-лучевых трубок

- •6.6. Осциллографические трубки

- •6.7. Индикаторные трубки

- •6.8. Кинескопы

- •6.9. Цветные кинескопы

- •Глава 7 элементы и устройства оптоэлектроники

- •7.1. Источники оптического излучения

- •7.2. Характеристики светодиодов

- •7.3. Основные параметры светодиодов

- •7.4. Полупроводниковые приемники излучения

- •7.5. Фоторезисторы

- •7.6. Характеристики фоторезистора

- •7.7. Параметры фоторезистора

- •7.8. Фотодиоды

- •7.9. Характеристики и параметры фотодиода

- •7.10. Фотоэлементы

- •7.11. Фототранзисторы

- •7.12. Основные характеристики и параметры фототранзисторов

- •7.13. Фототиристоры

- •7.14. Оптопары

- •7.15. Входные и выходные параметры оптопар

- •7.16. Жидкокристаллические индикаторы

- •Параметры жки

- •Глава 8 элементы интегральных микросхем

- •8.1. Пассивные элементы интегральных микросхем

- •8.1.1. Резисторы

- •8.1.2. Конденсаторы

- •8.1.3. Пленочные конденсаторы

- •8.2. Биполярные транзисторы

- •8.3. Диоды полупроводниковых имс

- •8.4. Биполярные транзисторы с инжекционным питанием

- •8.5. Полупроводниковые приборы c зарядовой связью

- •Применение пзс

- •Параметры элементов пзс

- •Глава 9 основы цифровой техники

- •9.1. Электронные ключевые схемы

- •9.2. Ключи на биполярном транзисторе

- •9.3. Ключ с барьером Шотки

- •9.4. Ключи на мдп транзисторах

- •9.5. Ключ на комплементарных транзисторах

- •9.6. Алгебра логики и основные её законы

- •9.7. Логические элементы и их классификация

- •Классификация ис по функциональному назначению

- •Классификация ис по функциональному назначению

- •9.8. Базовые логические элементы цифровых

- •9.9. Диодно–транзисторная логика

- •9.10. Транзисторно–транзисторная логика (ттл)

- •9.11. Микросхемы ттл серий с открытым коллектором

- •9.12. Правила схемного включения элементов

- •9.13. Эмиттерно–связанная логика

- •9.14. Интегральная инжекционная логика (и2л)

- •9.15. Логические элементы на мдп-транзисторах

- •9.16. Параметры цифровых ис

- •9.17. Триггеры

- •Параметры триггеров

- •9.18. Мультивибраторы

- •9.18.1. Мультивибраторы на логических интегральных элементах

- •9.18.2. Автоколебательный мультивибратор с

- •9.18.3. Автоколебательные мультивибраторы с

- •9.18.4. Ждущие мультивибраторы

- •Глава 10 аналоговые устройства

- •10.1. Классификация аналоговых электронных устройств

- •10.2. Основные технические показатели и характеристики аналоговых устройств

- •10.3. Методы обеспечения режима работы транзистора в каскадах усиления

- •10.3.1. Схема с фиксированным током базы

- •10.3.2. Схема с фиксированным напряжением база–эмиттер

- •10.3.3. Схемы с температурной стабилизацией

- •10.4. Стабильность рабочей точки

- •10.5. Способы задания режима покоя в усилительных

- •10.6. Обратные связи в усилителях

- •10.6.1. Последовательная обратная связь по напряжению

- •10.6.2. Последовательная обратная связь по току

- •10.7. Режимы работы усилительных каскадов

- •10.8. Работа активных элементов с нагрузкой

- •10.9. Усилительный каскад с общим эмиттером

- •10.10. Усилительный каскад по схеме с общей базой

- •10.11. Усилительный каскад с общим коллектором

- •10.12. Усилительные каскады на полевых транзисторах

- •10.12.1. Усилительный каскад с ои

- •10.12.2. Усилительный каскад с общим стоком

- •10.13. Усилители постоянного тока

- •Глава 11 Дифференциальные и операционные усилители

- •11.1. Дифференциальные усилители

- •11.2. Операционные усилители

- •11.3. Параметры операционных усилителей

- •11.4. Амплитудно и фазочастотные характеристики оу

- •11.5. Устройство операционных усилителей

- •11.6. Оу общего применения

- •11.7. Инвертирующий усилитель

- •11.8. Неинвертирующий усилитель

- •11.9. Суммирующие схемы

- •11.9.1. Инвертирующий сумматор

- •11.9.2. Неинвертирующий сумматор

- •11.9.3. Интегрирующий усилитель

- •11.9.4. Дифференцирующий усилитель

- •11.9.5. Логарифмические схемы

- •11.9.6. Антилогарифмирующий усилитель

- •Глава 12 компараторы напряжения

- •Глава 13 Цифро-аналоговые преобразователи

- •13.1. Параметры цап

- •13.2. Устройство цап

- •Глава 14 Аналого-цифровые преобразователи

- •14.1. Параметры ацп

- •14.2. Классификация ацп

- •14.3. Ацп последовательного приближения

- •ЛитературА

9.8. Базовые логические элементы цифровых

интегральных микросхем

Логические интегральные микросхемы, выпускаются в виде серии логических элементов. Логические интегральные микросхемы, выполненные по биполярной технологии и схемотехнической реализации, делятся на следующие группы:

1. Транзисторная логика с непосредственной связью между логическими элементами (ТЛНС).

2. Транзисторная логика с резистивными связями между логическими элементами (ТРЛ).

3. Резистивно–емкостная транзисторная логика (РЕТЛ).

4. Диодно–транзисторная логика (ДТЛ).

5. Транзисторно–транзисторная логика (ТТЛ).

6. Эмиттерно–связанная логика.

7. Инжекционная интегральная логика И2Л.

С применением полевых транзисторов наибольшее развитие получили микросхемы КМДП логики.

Серии цифровых интегральных микросхем ТЛНС, ТРЛ, РЕТЛ, ДТЛ хотя и продолжают выпускаться промышленностью, но используются для комплектации находящейся в эксплуатации электронной аппаратуры и не используются в новых разработках. Наиболее интенсивное распространение в настоящее время получили серии цифровых интегральных микросхем, построенных на основе ТТЛ, ЭСЛ, И2Л, КМПД логики.

Разработка каждой серии микросхем начинается с базового логического элемента – основы всех элементов, узлов и устройств серии. Базовые логические элементы выполняют либо операцию И–НЕ, либо ИЛИ–НЕ. Разнообразие типов базовых элементов объясняется тем, что каждый из них имеет свои достоинства и свою область применения.

9.9. Диодно–транзисторная логика

Диодно–транзисторная логика (ДТЛ) представляет собой сочетание диодных логических ячеек с транзисторным инвертором. Базовым логическим элементом всех серий ДТЛ является элемент Шеффера (элемент И–НЕ), реализующий операцию логического умножения с отрицанием. Промышленностью выпускается следующий перечень серий элементов ДТЛ: К104, К109, К121, К128, К146, К202, К215, К217, К218, К221, К240, К511.

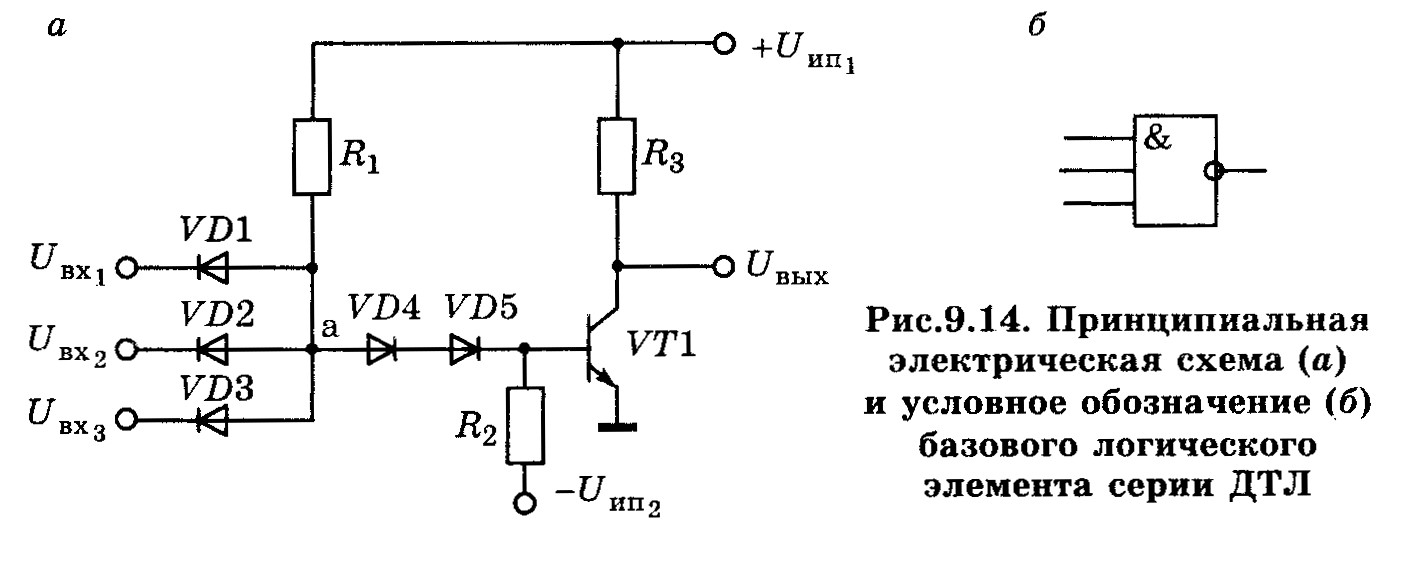

Схема логического элемента ДТЛ представлена на рис. 9.14.

Входные диоды VD1…VD3 и резистор R1 образуют входную логическую схему, выполняющую в положительной логике операцию И. Инвертор на транзисторе VТ1 выполняет логическую операцию НЕ, усиливает и формирует сигналы на выходе до стандартного уровня. Смещающие диоды VD4 и VD5 пред-

назначены

для увеличения порога запирания и

помехоустойчивости схемы в закрытом

состоянии, а резистор R2

и

![]() обеспечивают оптимальную величину тока

этих диодов. Диоды VD1…VD3

должны обладать минимальным сопротивлением

в проводящем состоянии; высоким

(максимальным) обратным напряжением;

малой емкостью и малым временем

восстановления обратного сопротивления.

обеспечивают оптимальную величину тока

этих диодов. Диоды VD1…VD3

должны обладать минимальным сопротивлением

в проводящем состоянии; высоким

(максимальным) обратным напряжением;

малой емкостью и малым временем

восстановления обратного сопротивления.

Рассмотрим

принцип работы ДТЛ. Пусть на один (или

на все входы) подается низкий входной

сигнал логического нуля

![]() .

Входной диод (или все диоды) открывается

и оказывается замкнутым на общую шину.

От источника питания

.

Входной диод (или все диоды) открывается

и оказывается замкнутым на общую шину.

От источника питания

![]() через резистор R1,

открытый диод и входную цепь протекает

ток, при этом потенциал точки a

уменьшается до уровня прямого падения

напряжения на диоде

через резистор R1,

открытый диод и входную цепь протекает

ток, при этом потенциал точки a

уменьшается до уровня прямого падения

напряжения на диоде

![]() ,

где Uпр –

падение

напряжения на открытом входном диоде.

При отсутствии VD4,

VD5

потенциал базы транзистора VТ1

был бы положительным, а транзистор –

открыт. За счет падения напряжения Uд см

на диодах VD4,

VD5

потенциал базы транзистора отрицателен –

Uб=Uа–2Uдсм,

транзистор закрыт и на выходе схемы

формируется высокий уровень напряжения

логической единицы. Диоды смещения

должны обладать большим сопротивлением,

чтобы при относительно малом токе

получить большое падение напряжения.

,

где Uпр –

падение

напряжения на открытом входном диоде.

При отсутствии VD4,

VD5

потенциал базы транзистора VТ1

был бы положительным, а транзистор –

открыт. За счет падения напряжения Uд см

на диодах VD4,

VD5

потенциал базы транзистора отрицателен –

Uб=Uа–2Uдсм,

транзистор закрыт и на выходе схемы

формируется высокий уровень напряжения

логической единицы. Диоды смещения

должны обладать большим сопротивлением,

чтобы при относительно малом токе

получить большое падение напряжения.

При одновременной подаче на все входы высокого уровня напряжения логической единицы диоды VD1…VD3 запираются. Транзистор VT1 переходит в область насыщения за счет тока, протекающего от источника питания через R1, смещающие диоды VD4, VD5, в базу транзистора. На выходе схемы появляется низкий уровень напряжения, близкий к нулю .

С целью уменьшения входного тока инвертора при действии на входе схемы напряжения логического нуля входную цепь усложняют, включая транзистор VТ1 (рис. 9.15), который работает как эмиттерный повторитель и увеличивает усиление по току. А для улучшения выходных характеристик логического элемента выходной каскад строится по более сложной схеме.

З а

счет падения напряжения на эмиттерном

переходе транзистора VТ1,

работающего в активном (ненасыщенном)

режиме, повышается общая помехоустойчивость

и уменьшается время переходных процессов

при включении и выключении схемы. Сложный

инвертор позволяет повысить нагру-зочную

способность. Схема обладает малым

выходным сопротивлением в обоих

состояниях, благодаря чему заряд и

разряд паразитных емкостей в нагрузках

следующего каскада протекает быстрее,

работа этого инвертора будет рассмотрена

при рассмотрении базового элемента

ТТЛ.

а

счет падения напряжения на эмиттерном

переходе транзистора VТ1,

работающего в активном (ненасыщенном)

режиме, повышается общая помехоустойчивость

и уменьшается время переходных процессов

при включении и выключении схемы. Сложный

инвертор позволяет повысить нагру-зочную

способность. Схема обладает малым

выходным сопротивлением в обоих

состояниях, благодаря чему заряд и

разряд паразитных емкостей в нагрузках

следующего каскада протекает быстрее,

работа этого инвертора будет рассмотрена

при рассмотрении базового элемента

ТТЛ.