- •1.4.2 Передатна характеристика

- •1.4.3 Швидкість наростання вихідного сигналу

- •2) Комутація пакетів

- •Iнтерполяцйне розділення - штучно збльшена розрізнювальна здатність сканера досягаться програмним шляхом в драйвер сканера за допомогою математичних алгоритмв.

- •1.4. Архітектура мікропроцесорних систем

- •2.5. Модель osi і реальні протоколи

- •1. Класифікація та характеристики сучасних пзп

- •2 Програмний обмін інформацією

- •3 Обмін за перериваннями

- •4 Обмін з використанням прямого доступу до пам'яті

- •2) Комутація пакетів

- •3.3.3. Формати кадрів технології Ethernet

- •4. Для даних, що передаються через комп’ютерну мережу виконати такі дії:

- •3.4. Множення чисел з плаваючою комою

- •4. Для даних, що передаються через комп’ютерну мережу виконати такі дії:

- •100Base-t4 для кабелю з чотирьох пар на неекранованій кручений парі utp категорії 3, 4 чи 5;

- •100Base-t4 — 4 пари категорії 3;

- •003Ffh) і кінцеві (ffff0h-fffffh) адреси зарезервовані для системи

- •Ip; зміщення в сегменті даних і додатковому сегменті даних - ефективною

- •4. Синтезувати схему керуючого автомата для закодованої граф – схеми алгоритму:

- •4. Для даних, що передаються через комп’ютерну мережу виконати такі дії:

- •4. Для даних, що передаються через комп’ютерну мережу виконати такі дії:

- •4. Для даних, що передаються через комп’ютерну мережу виконати такі дії:

- •4. Синтезувати схему керуючого автомата для закодованої граф – схеми алгоритму:

- •4. Синтезувати схему керуючого автомата для закодованої граф – схеми алгоритму:

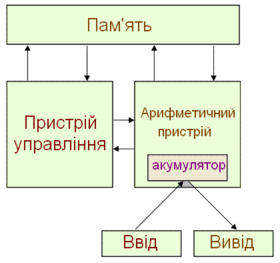

1.4. Архітектура мікропроцесорних систем

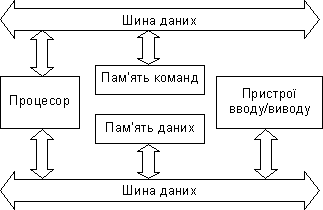

Дотепер ми розглядали тільки один тип архітектури мікропроцесорних систем - архітектуру з загальною, єдиною шиною для даних і команд (одношинну, або принстонську, фон-нейманівську архітектуру). Відповідно, у складі системи в цьому випадку присутня одна загальна пам'ять, як для даних, так і для команд (Рис. 1.15).

Рис.

1.15. Архітектура з загальною шиною даних

і команд.

Рис.

1.15. Архітектура з загальною шиною даних

і команд.

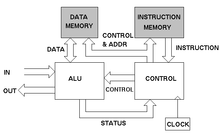

Але існує також і альтернативний тип архітектури мікропроцесорної системи - це архітектура з роздільними шинами даних і команд (двохшинна, або гарвардська архітектура). Ця архітектура припускає наявність у системі окремої пам'яті для даних і окремої пам'яті для команд (Рис. 1.16). Обмін процесора з кожним із двох типів пам'яті відбувається по своїй шині.

Архітектура з загальною шиною поширена набагато більше, вона застосовується, наприклад, у персональних комп'ютерах і в складних мікрокомп'ютерах. Архітектура з роздільними шинами застосовується, в основному, в однокристальних мікроконтролерах.

Розглянемо деякі переваги і недоліки обидвох архітектурних рішень.

Архітектура з загальною шиною (принстонська, фон-нейманівська) є простішою, вона не вимагає від процесора одночасного обслуговування двох шин, контролю обміну двома шинами відразу. Наявність єдиної пам'яті даних і команд дозволяє гнучко розподіляти її об'єм між кодами даних і команд. Наприклад, у деяких випадках потрібна велика і складна програма, а даних у пам'яті треба зберігати не надто багато. В інших випадках, навпаки, програма проста, але необхідні великі об'єми збережених даних. Перерозподіл пам'яті не викликає ніяких проблем, головне - щоб програма і дані разом вміщувалися в пам'яті системи. Як правило, у системах з такою архітектурою пам'ять буває досить великого об'єму (до десятків і сотень мегабайт). Це дозволяє вирішувати самі складні задачі.

Рис.

1.16. Архітектура з роздільними шинами

даних і команд.

Рис.

1.16. Архітектура з роздільними шинами

даних і команд.

Архітектура з роздільними шинами даних і команд складніша, вона змушує процесор працювати одночасно з двома потоками кодів, обслуговувати обмін двома шинами одночасно. Програма може розміщуватися тільки в пам'яті команд, дані - тільки в пам'яті даних. Така вузька спеціалізація обмежує коло задач, які розв'язуються системою, тому що не дає можливості гнучкого перерозподілу пам'яті. Пам'ять даних і пам'ять команд у цьому випадку мають порівняно невеликий об'єм, тому застосування систем з даною архітектурою обмежується переважно не надто складними задачами.

У чому ж перевага архітектури з двома шинами (гарвардської)? У першу чергу, у швидкодії.

Справа в тому, що при єдиній шині команд і даних процесор змушений по одній цій шині приймати дані (з пам'яті або пристрою вводу/виводу) і передавати дані (у пам'ять або в пристрій вводу/виводу), а також читати команди з пам'яті. Природно, одночасно ці пересилання кодів магістралями відбуватися не можуть, вони повинні відбуватися по черзі. Сучасні процесори здатні поєднати в часі виконання команд і проведення циклів обміну системною шиною. Використання конвеєрних технологій і швидкої кеш-пам'яті дозволяє їм прискорити процес взаємодії з порівняно повільною системною пам'яттю. Підвищення тактової частоти й удосконалення структури процесорів дають можливість скоротити час виконання команд. Але подальше збільшення швидкодії системи можливе тільки при поєднанні пересилання даних і читання команд, тобто при переході до архітектури з двома шинами.

У випадку двохшинної архітектури обмін обидвома шинами може бути незалежним, паралельним у часі. Відповідно, структури шин (кількість розрядів коду адреси і коду даних, порядок і швидкість обміну інформацією і т.д.) можуть бути обрані оптимально для тієї задачі, яка виконується кожною шиною. Тому за інших рівних умов перехід на двохшинну архітектуру прискорює роботу мікропроцесорної системи, хоча і вимагає додаткових витрат на апаратуру, ускладнення структури процесора. Пам'ять даних у цьому випадку має свій розподіл адрес, а пам'ять команд - свій.

Найпростіше переваги двохшинної архітектури реалізуються усередині однієї мікросхеми. У цьому випадку можна також істотно зменшити вплив недоліків цієї архітектури. Тому основне її застосування - у мікроконтролерах, від яких не потрібно рішення надто складних задач, але зате необхідна максимальна швидкодія при заданій тактовій частоті.

Сторінковий розподіл

На малюнку 2.12 показана схема сторінкового розподілу пам'яті. Віртуальний адресний простір кожного процесу ділиться на частини однакового, фіксованого для даної системи розміру, звані віртуальними сторінками. У загальному випадку розмір віртуального адресного простору не є кратним розміру сторінки, тому остання сторінка кожного процесу доповнюється фіктивною областю.

Вся оперативна пам'ять машини також ділиться на частини такого ж розміру, звані фізичними сторінками (або блоками).

Розмір сторінки зазвичай вибирається рівним ступеню двійки: 512, 1024 і так далі, це дозволяє спростити механізм перетворення адрес.

При завантаженні процесу частина його віртуальних сторінок поміщається в оперативну пам'ять, а останні - на диск. Суміжні віртуальні сторінки не обов'язково розташовуються в суміжних фізичних сторінках. При завантаженні операційна система створює для кожного процесу інформаційну структуру - таблицю сторінок, в якій встановлюється відповідність між номерами віртуальних і фізичних сторінок для сторінок, завантажених в оперативну пам'ять, або робиться відмітка про те, що віртуальна сторінка вивантажена на диск. Крім того, в таблиці сторінок міститься інформація, що управляє, така як ознака модифікації сторінки, ознака невыгружаемости (вивантаження деяких сторінок може бути заборонена), ознака звернення до сторінки (використовується для підрахунку числа звернень за певний період часу) і інші дані, що формуються і використовувані механізмом віртуальної пам'яті.

Мал. 2.12. Сторінковий розподіл пам'яті

При активізації чергового процесу в спеціальний регістр процесора завантажується адреса таблиці сторінок даного процесу.

При кожному зверненні до пам'яті відбувається читання з таблиці сторінок інформації про віртуальну сторінку, до якої відбулося звернення. Якщо дана віртуальна сторінка знаходиться в оперативній пам'яті, то виконується перетворення віртуальної адреси у фізичний. Якщо ж потрібна віртуальна сторінка в даний момент вивантажена на диск, то відбувається так зване сторінкове переривання. Процес, що виконується, переводиться в стан очікування, і активізується інший процес з черги готових. Паралельно програма обробки сторінкового переривання знаходить на диску необхідну віртуальну сторінку і намагається завантажити її в оперативну пам'ять. Якщо в пам'яті є вільна фізична сторінка, то завантаження виконується негайно, якщо ж вільних сторінок немає, то вирішується питання, яку сторінку слід вивантажити з оперативної пам'яті.

У даній ситуації може бути використане багато різних критеріїв вибору, найбільш популярні з них наступні:

найдовше сторінка, що не використалася

перша сторінка, що попалася

сторінка, до якої останнім часом було менше всього звернень.

У деяких системах використовується поняття робочої безлічі сторінок. Робоча множина визначається для кожного процесу і є переліком найбільш часто використовуваних сторінок, які повинні постійно знаходитися в оперативній пам'яті і тому не підлягають вивантаженню.

Після того, як вибрана сторінка, яка повинна покинути оперативну пам'ять, аналізується її ознака модифікації (з таблиці сторінок). Якщо виштовхувана сторінка з моменту завантаження була модифікована, то її нова версія повинна бути переписана на диск. Якщо немає, то вона може бути просто знищена, тобто відповідна фізична сторінка оголошується вільною.

Розглянемо механізм перетворення віртуальної адреси у фізичний при сторінковій організації пам'яті (малюнок 2.13).

Віртуальна адреса при сторінковому розподілі може бути представлений у вигляді пари (p, s), де p - номер віртуальної сторінки процесу (нумерація сторінок починається з 0), а s - зсув в межах віртуальної сторінки. Враховуючи, що розмір сторінки дорівнює 2 в ступені до, зсув s може бути отримане простим відділенням до молодших розрядів в двійковому записі віртуальної адреси. Старші розряди, що залишилися, є двійковим записом номера сторінки р.

Мал. 2.13. Механізм перетворення віртуальної адреси у фізичний при сторінковій організації пам'яті

При кожному зверненні до оперативної пам'яті апаратними засобами виконуються наступні дії:

на підставі початкової адреси таблиці сторінок (вміст регістра адреси таблиці сторінок), номери віртуальної сторінки (старші розряди віртуальної адреси) і довжини запису в таблиці сторінок (системна константа) визначається адреса потрібного запису в таблиці

з цього запису витягується номер фізичної сторінки

до номера фізичної сторінки приєднується зсув (молодші розряди віртуальної адреси).

Використання в пункті (3) того факту, що розмір сторінки дорівнює ступеню 2, дозволяє застосувати операцію конкатенації (приєднання) замість тривалішої операції складання, що зменшує час отримання фізичної адреси, а значить підвищує продуктивність комп'ютера.

На продуктивність системи із сторінковою організацією пам'яті впливають тимчасові витрати, пов'язані з обробкою сторінкових переривань і перетворенням віртуальної адреси у фізичний. При часто виникаючих сторінкових перериваннях система може витрачати велику частину часу даремно, на свопінг сторінок. Щоб зменшити частоту сторінкових переривань, слід було б збільшувати розмір сторінки. Крім того, збільшення розміру сторінки зменшує розмір таблиці сторінок, а значить зменшує витрати пам'яті. З іншого боку, якщо сторінка велика, означає велика і фіктивна область в останній віртуальній сторінці кожної програми. В середньому на кожній програмі втрачається половина об'єму сторінки, що в сумі при великій сторінці може скласти істотну величину. Час перетворення віртуальної адреси у фізичний в значній мірі визначається часом доступу до таблиці сторінок. У зв'язку з цим таблицю сторінок прагнуть розміщувати в "швидких" пристроях, що запам'ятовують. Це може бути, наприклад, набір спеціальних регістрів або пам'ять, що використовує для зменшення часу доступу асоціативний пошук і кешування даних.

Сторінковий розподіл пам'яті може бути реалізоване в спрощеному варіанті, без вивантаження сторінок на диск. В цьому випадку всі віртуальні сторінки всіх процесів постійно знаходяться в оперативній пам'яті. Такий варіант сторінкової організації хоча і не надає користувачеві віртуальної пам'яті, але майже виключає фрагментацію за рахунок того, що програма може завантажуватися в несуміжні області, а також того, що при завантаженні віртуальних сторінок ніколи не утворюється залишків.

БІЛЕТ № 4

1. T-тригер: загальні відомості, класифікація, типи.

2. Синхронізація паралельних процесів за допомогою семафорів.

3. Поняття архітектури ЕОМ. Архітектура фон – Неймана, гарвардська архітектура.

4. Створити процедуру обробки події мовою Visual Basic. Процедура повинна включати введення даних за допомогою форми, обчислення заданого виразу і виведення результатів через вікно повідомлення. Складену програму виконати на комп’ютері і перевірити правильність результату.

Cтворити процедуру обробки події для обчислення арифметичного виразу мовою Visual Basic:

Змінні А, В, С, Мі задані в процедурі

(A=8, B=2, C=3, M= ).

).

Варіант 1. Змінна R вводиться за допомогою вікна InputBox(), а результат виводиться через вікно повідомлення.

Варіант 2. Змінна R вводиться за допомогою вікна TextBox() першої форми, а результат виводиться за допомогою вікна TextBox() другої форми.

Складену програму виконати на комп’ютері і перевірити правильність результату.

Проект 4.

Триггер – устройство с двумя устойчивыми состояниями, которое содержит запоминающий элемент и схему управления. Триггера предназначены для хранения одного разряда информации.

Триггер Т-типа — триггер, который меняет свое состояние на противоположное с приходом сигнала на вход Т. Это единственный триггер, текущее состояние которого определяется не информацией на входах, а состоянием его в предыдущий момент времени. Ввиду широкого применения в счетчиках импульсов его часто называют счетным триггером.

Асинхронный Т-триггер - это устройство с двумя устойчивыми состояниями и одним информационным входом Т.

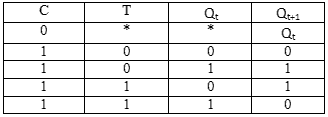

Синхронный Т-триггер отличается от асинхронного только наличием синхронного входа С. Когда С=0 – триггер находится в режиме хранения. Когда С=1 он работает как и асинхронный.

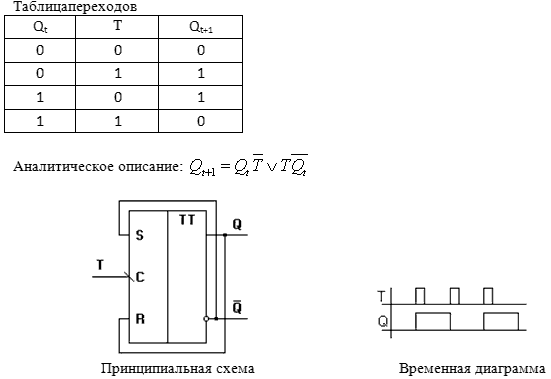

Таблица переходов

Временная диаграмма, функциональная и принципиальная схемы синхронного Т-триггера

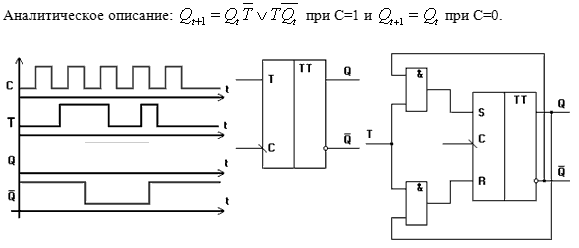

Реализация Т-триггеров на триггерах других типов:

Семафори.

Семафори традиційно використовувалися для синхронізації процесів, що звертаються до поділюваних даних. Кожен процес повинний виключати для всіх інших процесів можливість одночасного з ним звернення до цих даних (взаємовиключення). Коли процес звертається до поділюваних даних, говорять, що він знаходиться у своїй критичній ділянці.

Для вирішення задачі синхронізації необхідно, у випадку якщо один процес знаходиться в критичній ділянці, виключити можливість входження для інших процесів у їхні критичні ділянки. Хоча б для тих, котрі звертаються до тих же самим поділюваних даних. Коли процес виходить із своєї критичної ділянки, то одному з інших процесів, що очікують входу у свої критичні ділянки, повинно бути дозволено продовжити роботу.

Процеси повинні якнайшвидше проходити свої критичні ділянки і не повинні в цей період блокуватися. Якщо процес, що знаходиться у своїй критичній ділянці, завершується (можливо, аварійно), то необхідно, щоб деякий інший процес міг скасувати режим взаємовиключення, надаючи іншим процесам можливість продовжити виконання і ввійти у свої критичні ділянки.

Семафор – це захищених змінна, значення якої можна опитувати і змінювати тільки за допомогою спеціальних операцій wait і signal і операції ініціалізації init. Двійкові семафори можуть приймати тільки значення 0 і 1. Семафори з лічильниками можуть приймати невід’ємні цілі значення.

Операції є неподільними. Критичні ділянки процесів позначаються операціями wait() і signal(). Якщо одночасно декілька процесів спробують виконати операцію wait(), то це буде дозволено тільки одному з них, а іншим прийдеться зачекати.

Семафори з лічильниками використовуються, якщо деякий ресурс виділяється з множини ідентичних ресурсів. При ініціалізації такого семафора в його лічильнику вказується число елементів множини. Кожна операція wait() зменшує значення лічильника семафора на 1, показуючи, що деякому процесу виділений один ресурс із множини. Кожна операція signal() збільшує значення лічильника на 1, показуючи, що процес повернув ресурс у множину.

Архітекту́ра ЕОМ — це набір відомостей, необхідний та достатній для написання для даної обчислювальної машини коректних програм на машинній мові, таких, що не залежать від конкретного втілення цієї архітектури. Електронні обчислювальні машини одної архітектури (тобто з однаковою програмною організацією), але реалізовані з використанням різних конструктивних рішень, називають сумісними, або сумісним сімейством ЕОМ.

Найбільшого поширення в ЕОМ отримали 2 типи архітектури: прінстонська (фон Неймана) і гарвардська. Обидві вони виділяють 2 основних вузли ЕОМ: центральний процесор і пам'ять комп'ютера. Різниця полягає в структурі пам'яті: в прінстонській архітектурі програми і дані зберігаються в одному масиві пам'яті і передаються в процесор одним каналом, тоді як гарвардська архітектура передбачає окремі сховища і потоки передачі для команд і даних.

У докладніший опис, що визначає конкретну архітектуру, також входять: структурна схема ЕОМ, засоби і способи доступу до елементів цієї структурної схеми, організація і розрядність інтерфейсів ЕОМ, набір і доступність регістрів, організація пам'яті та способи її адресації, набір і формат машинних команд процесора, способи представлення і формати даних, правила обробки переривань.

За перерахованими ознаками та їх поєднаннями серед архітектур виділяють:

За розрядністю інтерфейсів і машинних слів: 8 -, 16 -, 32 -, 64-розрядні (ряд ЕОМ має й інші розрядності);

За особливостями набору регістрів, формату команд і даних: CISC, RISC, VLIW;

За кількістю центральних процесорів: однопроцесорні, багатопроцесорні, суперскалярні;

багатопроцесорні за принципом взаємодії з пам'яттю: симетричні багатопроцесорні (SMP), масивно-паралельні (MPP), розподілені

Архітектура ЕОМ включає інформацію про:

набір машинних команд (набір інструкцій), тобто операцій, які може виконувати ця обчислювальна машина

доступні регістр процесора — внутрішні комірки пам'яті процесора (пристрою, який виконує набір інструкцій), а саме: функціональне призначення, розрядність, кількість, особливості програмування таких регістрів.

розрядність та формати даних операндів — об'єктів, над якими виконуються операції

способи адресації пам'яті — методи доступу до операндів в пам'яті ЕОМ

механізми управління та захисту пам'яті

особливості обробки виключних ситуацій та помилок в системі

організацію системи вводу-виводу

доступні програмісту апаратні засоби організації багатозадачної та багатопроцесорної обробки інформації

Часто, особливо в останній час, термін «архітектура ЕОМ» вживається також для позначення саме архітектури системи команд, або архітектури (програмної моделі) процесора, тобто пп. 1-6 цього переліку. Інша інтерпретація цього поняття стосується вже обчислювальних систем, які включають багато обчислювачів, об'єднаних тим чи іншим чином, які реалізують певні стратегії обчислень. Тоді під терміном «архітектура» розуміють якраз конфігурацію та стратегії обчислень даної системи. В цій енциклопедії, якщо не вказано додатково, під архітектурою ЕОМ розуміється саме вищенаведений перелік відомостей.

Архітекту́ра фон Не́ймана (архітектура фон Неймана-Екерта-Маклі), архітектура електронних обчислювальних машин, основною відмінністю якої від інших подібних архітектур є спільне зберігання даних та машинних команд в комірках однієї й тієї ж пам'яті, що унеможливлює їх розрізнення за способом представлення або кодування. Названа так на честь відомого математика та теоретика обчислювальної техніки Джона фон Неймана (John von Neumann), та по сьогодні залишається домінуючою схемою організації ЕОМ загального призначення.

![]()

Схематичне вираження схеми фон Неймана

Формальне визначення

Обчислювальна машина є машиною з архітектурою фон Неймана, якщо:

Програма та дані зберігаються в одній загальній пам'яті.

Кожна комірка пам'яті машини ідентифікується унікальним номером, який називається адресою.

Різні слова інформації (команди та дані) розрізняються за способом використання, але не за способом кодування та структурою представлення в пам'яті.

Кожна програма виконується послідовно, починаючи з першої команди, якщо немає спеціальних вказівок. Для зміни цієї послідовності використовуються команди передачі управління.

[ред.] Класична структура машини фон Неймана

Машина фон Неймана, як і практично кожна сучасна ЕОМ загального призначення, складається з чотирьох основних компонентів:

Операційний пристрій (ОП), який виконує команди з визначеного набору, який називається системою (набором) команд, над порціями інформації, яка зберігається відокремленій від операційного пристрою пам'яті (хоча сучасні архітектури мають в складі операційного пристрою додаткову пам'ять (зазвичай банк регістрів), в якій операнди зберігаються порівняно короткий час безпосередньо в процесі проведення обчислень.

Пристрій управління (ПУ), який організує послідовне виконання алгоритмів, розшифрування команд, які поступають із запам'ятовуючого пристрою (див. нижче), реагує на аварійні ситуації та виконує загальні функції управління всіма вузлами обчислювальної машини. Зазвичай ОП та ПУ об'єднуються в структуру, яка називається центральним процесором. Слід звернути увагу, що вимога саме послідовного, в порядку надходження з пам'яті (в порядку зміни адрес в лічильнику команд) виконання команд є принциповою. Архітектури, які не додержуються такого принципу, взагалі не вважаються фон-нейманівськими.

Запам'ятовуючий пристрій (ЗП) — масив комірок з унікальними ідентифікаторами (адресами), в яких зберігаються команди та дані.

Пристрій вводу-виводу (ПВВ), який забезпечує зв'язок ЕОМ з зовнішнім світом, різними пристроями, які передають інформацію на переробку в ЕОМ та приймають результати.

[ред.] Принцип функціонування

Після завантаження програми (алгоритму й даних для обробки) в запам'ятовуючий пристрій, машина фон-Неймана може працювати автоматично, без втручання оператора. Кожна комірка пам'яті машини має унікальний номер — адресу, а спеціальний механізм, частіше всього — лічильник команд — забезпечує автоматичне виконання необхідної послідовності команд, і визначає на кожному етапі адресу комірки, з якої необхідно завантажити наступну команду.

Перед початком виконання програми в лічильник записується адреса її першої команди. Визначення адреси наступної команди відбувається за одним з наступних сценаріїв:

Якщо поточна команда не є командою передачі управління (тобто це просто арифметична або логічна операція над даними), то до поточного значення лічильника додається число, яке дорівнює довжині поточної команди в мінімально адресованих одиницях інформації (зрозуміло, що це можливо за умови, якщо звичайні команди в блоках, не розділених командами передачі управління, розташовуються послідовно в пам'яті, інакше адреса наступної команди може зберігатись, наприклад, безпосередньо в команді).

Якщо поточна команда — команда передачі управління (команда умовного або безумовного переходу), яка змінює послідовний хід виконання програми, то в лічильник примусово записується адреса тої команди, яка була замовлена при виконанні переходу, де б вона не знаходилась.

ти до: навігація, пошук

Га́рвардська архітекту́ра — архітектура обчислювальних машин, головною відмінністю якої від інших подібних архітектур (див. напр. Архітектура фон Ноймана), є те, що дані та оператори (алгоритм) зберігаються окремо. Першим комп'ютером, який застосовував гарвардську архітектуру, був Mark I, який експлуатувався в Гарварді (звідки назва архітектури) та зберігав дані окремо на перфокартах, а команди в релейному запам'ятовуючому пристрої.

Така структура має одну важливу перевагу над фон-нойманівською архітектурою: дані можна завантажувати для обробки з запам'ятовувальний пристрою одночасно з командами. В фон-нойманівській архітектурі для зв'язку операційного та керувальний пристроїв (які разом складають центральний процесор), використовується одна шина, тому необхідно спочатку завантажити в процесор команду, а вже потім, звернувшись за адресою, як вкзана в ній самій — завантажити дані. Наявність в гарвардській архітектурі двох незалежних підсистем пам'яті з окремими шинами, дозволяє вести процес завантаження команд і даних практично паралельно.

Головним недоліком гарвардської архітектури є порівняна з фон-нойманівською складність реалізації. Адже для кожного з запам'ятовуючих пристроїв необхідний свій контролер, своя шина, що зі збільшенням розрядності призводить до зростання кількості з'єднань в системі, і це негативно впливає як на складність проектування, так і на швидкодію.

Гарвардська архітектура широко застосовується в спеціалізованих обчислювачах, зокрема в мікроконтролерах та цифрових сигнальних процесорах, де необхідний високоінтенсивний обмін даними. Також за гарвардською архітектурою зазвичай організується кеш-пам'ять в ЕОМ загального призначення, яка розділяється окремо на кеш-пам'ять команд та кеш-пам'ять даних (але, строго кажучи, це стосується внутришньої організації процесора, а не архітектури ЕОМ)

БІЛЕТ № 5

Порівняльна характеристика RISC та СISC архітектури.

Сучасні моделі опису комп’ютерних мереж (моделі OSI та TCP/IP), їх порівняльний аналіз.

Постійні запам’ятовуючі пристрої. Flash – пам'ять.

Синтезувати схему керуючого автомата для закодованої граф – схеми алгоритму:

побудувати граф автомата, таблиці переходів та виходів автомата;

визначити логічні вирази для функцій збудження елементів пам’яті та вихідних функцій;

реалізувати схему автомата в заданому базисі та побудувати часові діаграми для заданої вихідної функції.

Вихідні дані:

закодована ГСА;

тип елементів пам’яті;

базис;

вихідна функція для побудови часових діаграм.

Аналіз коду програм, що генерується компіляторами мов високого

рівня, показав, що найчастіше використовується тільки обмежений набір

простих команд форматів "регістр, регістр →регістр" і "регістр↔ пам'ять".

Компілятори не в змозі ефективно використовувати складні команди. Це

спостереження сприяло формуванню концепції процесорів з скороченим

набором команд, так званих RISC-процесорів (RISC - Reduced Instruction Set

Computer).

Дейв Паттерсон і Карло Секуін сформулювали 4 основних принципи

побудови RISC-процесорів:

1. Будь-яка операція повинна виконуватися за один такт, незалежно від

її типу.

2. Система команд повинна містити мінімальну кількість найпростіших

інструкцій однакової довжини, що найбільш часто використовуються.

3. Операції обробки даних реалізуються тільки у форматі "регістр←

регістр" (операнди вибираються з оперативних регістрів процесора, і

результат операції записується також у регістр, а обмін між оперативними

регістрами й пам'яттю виконується тільки за допомогою команд

завантаження записи).

4. Склад системи команд повинен бути "зручний" для компіляції

операторів мов високого рівня.

Таким чином, RISC-процесори комп'ютерів зі скороченим набором

команд мають команди обробки типу "регістр ←регістр" і команди

збереження (store) і завантаження (load) типу "пам'ять ← регістр" і "регістр

← пам'ять" відповідно. Функціональні перетворення можуть виконуватися

лише над вмістом регістрів, а результат поміщається тільки в регістр.

Після відокремлення RISC-процесорів в окремий клас процесори з

традиційними наборами команд стали називатися "CISC-процесорами" (CISC

– Complicated Instruction Set Computer) з повним набором команд. Як

правило, в цих процесорах команди мають багато різних форматів і

вимагають для свого представлення різне число байтів пам'яті. Це обумовлює

визначення типу команди в ході її дешифрування при виконанні, що

ускладнює пристрій управління процесора і перешкоджає підвищенню

тактової частоти до рівня, досяжного в RISC-процесорах на тій же

елементній базі.

Мікропроцесори з класичною CISC - архітектурою реалізують на рівні

машинної мови комплексні набори команд різної складності (від простих,

характерних для мікропроцесора першого покоління, до складних,

характерних для 32-розрядних мікропроцесорів типу 80486, 68040 та ін.)

Лідером у цій галузі є фірма Intel і її клонмейкери, мікропроцесорами якої

комплектується більш 80% випускаються персональних комп'ютерів.

Мікропроцесори сімейства М60ххх фірми Motorola використовувалися в

персональних комп'ютерах типа Macintosh. Мікропроцесори цього сімейства

широко застосовуються також в пристроях управління, вбудованих в різні

прилади і системи: контрольну вимірювальну та зв'язкову апаратуру, лазерні

принтери та контролери дисководів, роботи і системи промислової

автоматики.

Мікропроцесори з RISC - архітектурою застосовуються, в основному, в

робочих станціях і потужних серверах. Широке застосування знаходять RISC

- мікропроцесори сімейств SPARC фірми Sun Microsystems і RxOOO фірми

MIPS Computer Systems. Останнім часом дуже активно впроваджуються в

різну апаратуру RISC - мікропроцесори сімейства PowerPC – спільна

розробка фірм IBM, Motorola і Apple Computers (альянс IMA). Процесори

PowerPC 7ХХ (G3), PowerPC 74XX (G4), PowerPC 970 (G5) являються

основою побудови персональних комп’ютерів iMac фірми Apple Computers.

Серед фірм, що випускають RISC-мікропроцесори, знаходяться також Intel,

Hewlett-Packard, Digital Equipment. Необхідно також відмітити трансп’ютери

– оригінальні RISC-мікропроцесори, що розроблені фірмою Inmos для

побудови мультипроцесорних систем.