- •1.Архитектура операционных систем

- •1.1Общие вопросы архитектуры операционных систем

- •1.2Архитектура Windows

- •1.2.1История возникновения Windows

- •1.2.2Архитектура ос Windows

- •1.2.3История возникновения ос Linux

- •1.2.4Архитектура Linux

- •1.2.5Интерфейсы системы unix

- •1.2.6Файловая система unix

- •1.2.7Аутентификация в unix

- •1.2.8Сценарии командной оболочки unix

- •1.3Операционная система qnx

- •1.3.1 Архитектура qnx

- •1.4Выводы

- •1.5Вопросы для самоконтроля

- •2.Типы и алгоритмы работы с оперативной памятью

- •2.1Общие принципы функционирования подсистемы памяти в ос

- •2.1.1Обобщённые принципы управления памятью

- •2.1.2Однозадачная система без подкачки на диск

- •2.1.3Многозадачность с фиксированными разделами

- •2.1.4Подкачка

- •2.1.5Управление памятью с помощью битовых массивов

- •2.1.6Управление памятью с помощью связанных списков

- •2.1.7Виртуальная память

- •2.1.8Многоуровневые таблицы страниц

- •2.1.9Алгоритмы замещения страниц

- •2.2Виртуальная память ос Windows

- •2.2.1Архитектура памяти в ос Windows

- •2.2.2Работа с виртуальной памятью в ос Windows

- •2.2.3Использование виртуальной памяти в приложениях

- •2.3Пример организации страничной памяти на примере linux

- •2.3.1Страничная организация памяти в Linux

- •2.3.2Права доступа к области памяти

- •2.3.3Работа с областями памяти в Linux

- •3.Процессы и потоки

- •3.1Процессы

- •3.1.1Модель процесса

- •3.1.2Создание процесса

- •3.1.3Завершение процесса

- •3.1.4Состояния процессов

- •3.1.5Реализация процессов

- •3.2Потоки

- •3.2.1Реализация потоков

- •3.2.2Реализация потоков на уровне ядра

- •3.2.3Смешанная реализация

- •3.2.4 Метод управления «Активация планировщика»

- •3.2.5Всплывающие потоки

- •3.3Межпроцессное взаимодействие

- •3.3.1Состояние состязания

- •3.3.2Критические секции (Критические области)

- •3.3.3Взаимное исключение с активным ожиданием

- •3.3.4Примитивы межпроцессного взаимодействия

- •3.4Семафоры

- •3.5Мьютексы

- •3.6Организация многопоточной обработки в среде Windows

- •3.6.1Объекты ядра Windows

- •3.6.2Потоки Windows

- •3.6.3Синхронизация потоков в Windows

- •3.6.4Синхронизация потоков с помощью объектов ядра

- •3.6.5Сравнение объектов, используемых для синхронизации потоков

- •3.7Организация процессов и потоков в Linux

- •3.7.1Среда окружения в Linux

- •3.7.2Создание нового процесса. Системный вызов exec.

- •3.7.3Потоки unix. Функции потоков стандарта posix.

- •3.8Синхронизация потоков в unix

- •3.8.1Мьютексы

- •3.8.2Семафоры

- •0,0,0, //Ожидать обнуления семафора

- •0,1,0 // Затем увеличить значение семафора на 1};

- •0,1, 0 // Увеличитьзначение семафора на 1};

2.3Пример организации страничной памяти на примере linux

В данной главе мы рассмотрим пример организации страничной адресации на примере Linux для процессора 80x86. Для данного процессора различают три вида адресов. Логический адрес— используется в инструкциях машинного языка для обозначения адреса операнда или инструкции. Этот тип адресов относится к широко известной сегментной архитектуре 80x86, которая заставляет программистов, работающих в MS-DOS и Windows, разбивать программы на сегменты. Каждый логический адрес состоит из сегмента и смещения, которое определяет расстояние от начала сегмента до адресуемой ячейки. Линейный адрес (также известный как виртуальный адрес) — 32-разрядное целое без знака, которое можно использовать для адресации до 4 Гбайт (4 294 967 296 ячеек памяти). Линейные адреса обычно представляются в шестнадцатеричной нотации, и их значения лежат в диапазоне от 0x00000000 до Oxffffffff. Физический адрес — используется для адресации ячеек в микросхемах памяти. Представляется электрическими сигналами, посылаемыми с адресных контактов микропроцессора на шину памяти. Физические адреса обозначаются 32- или 36-разрядными целыми без знака.

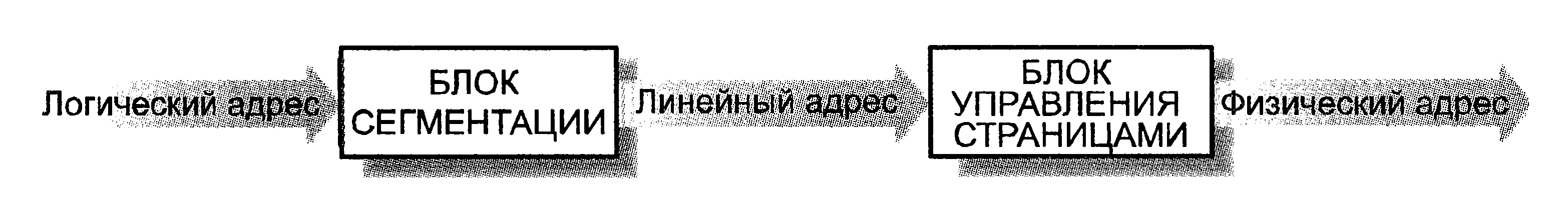

Блок управления памятью, или MMU (Memory Management Unit), преобразует логический адрес в линейный с помощью электронной схемы, которая называется блоком сегментации. Затем другая электронная схема, называемая блоком управления страницами, преобразует линейные адреса в физические (рис. 2.15)

Рис. 2.15. Преобразование логического адреса

В многопроцессорных системах все процессоры, как правило, совместно используют одну память. Это означает, что процессоры могут одновременно и независимо друг от друга обратиться к микросхемам оперативной памяти.

Поскольку операции чтения и записи на этих микросхемах должны выполняться последовательно, устройство, называемое арбитром памяти, помещается между шиной и каждой микросхемой оперативной памяти. Роль арбитра в том, чтобы предоставлять доступ процессору, если микросхема свободна, и откладывать запрос, если микросхема обслуживает другой процессор. Арбитры памяти существуют даже в однопроцессорных системах, потому что в таких системах имеются специализированные процессоры, называемые контроллерами DMA (Direct Memory Access, прямой доступ к памяти), которые работают параллельно с центральным процессором. В многопроцессорных системах структура арбитра сложнее, потому что у него больше входных портов. Например, в системах с двумя процессорами Pentium поддерживается арбитр с двумя портами на входе каждой микросхемы памяти, причем требуется, чтобы эти два процессора обменивались синхронизирующими сообщениями перед обращением к общей шине. От программиста арбитр скрыт, поскольку управляется аппаратными схемами.

2.3.1Страничная организация памяти в Linux

Начиная с процессоров 80386, блок управления страницами в процессорах Intel обрабатывает 4 Кбайт страниц.

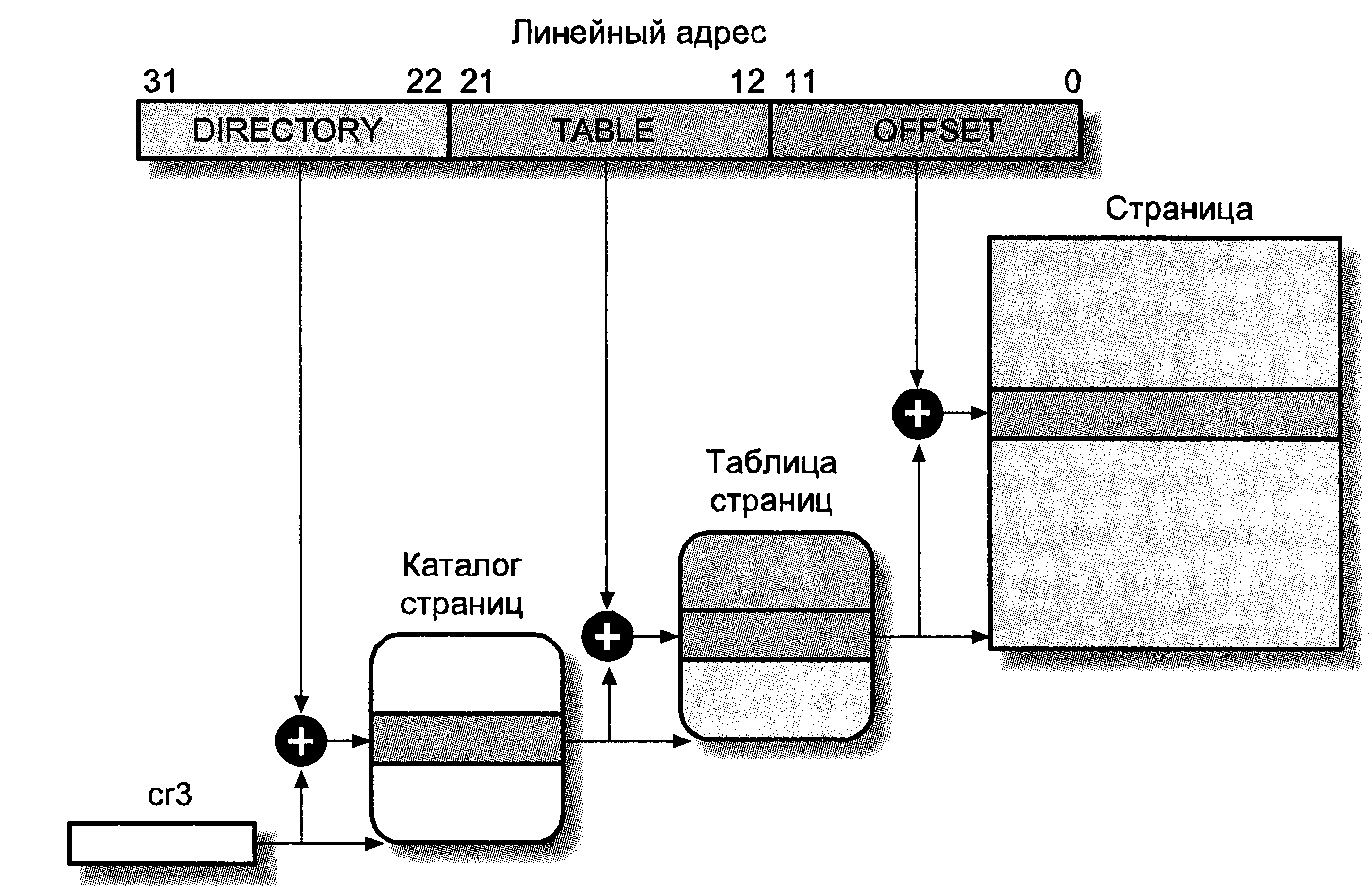

Тридцать два бита линейного адреса разделяются на три поля: каталог Directory — старшие 10 битов; таблица Table — средние 10 битов; смещение offset — младшие 12 битов. Преобразование линейных адресов происходит посредством двух таблиц.

Первая таблица преобразования называется каталогом страниц, а вторая — Таблицей Страниц1. Целью создания такой двухуровневой схемы является сокращение объема памяти, необходимого для Таблиц Страниц процессов. При наличии простой одноуровневой Таблицы Страниц потребовалось бы до 22 записей (или, если запись занимает 4 байта, 4 Мбайт оперативной памяти), чтобы представить Таблицу Страниц для каждого процесса (при условии, что процесс использует все 4 Гбайт пространства линейных адресов), даже если процесс не обращается к каждому адресу в этом диапазоне. Двухуровневая схема сокращает объем используемой памяти, поскольку требует Таблицы Страниц только для тех виртуальных областей, к которым фактически обращается процесс.

Каждый активный процесс должен иметь каталог страниц. В то же время отсутствует необходимость выделять память сразу под все Таблицы Страниц процесса. Будет гораздо эффективнее выделять оперативную память для Таблицы Страниц, только когда процесс действительно нуждается в ней.

Физический адрес используемого каталога страниц хранится в управляющем регистре cr3. Поле Directory линейного адреса определяет запись в каталоге страниц, указывающую на соответствующую Таблицу Страниц. Поле Table адреса, со своей стороны, определяет запись в Таблице Страниц, содержащую физический адрес страничного кадра, включающего в себя страницу.

Поле offset определяет относительную позицию внутри страничного кадра (рис. 2.16). Поскольку оно занимает 12 бит, каждая страница содержит 4096 байтов данных.

Рис. 2.16. Страничная организация в архитектуре 80x86

Поля Directory и Table имеют длину 10 битов, поэтому каталоги страниц и Таблицы Страниц могут содержать до 1024 записей. Отсюда следует, что каталог страниц может адресовать до 1024 х 1024 х 4096 = 232 ячеек памяти, как и следовало ожидать при 32-разрядной адресации.

Записи в каталогах страниц и в Таблицах Страниц имеют одинаковую структуру и была приведена ранее.