Лабораторная работа №2

.doc|

Министерство образования Российской Федерации |

|||

|

Уфимский Государственный Авиационный Технический Университет |

|||

|

|

|||

|

Отчет по лабораторной работе №3 |

|||

|

Проектирование и исследование регистров |

|||

|

|

|||

|

Вариант №5 |

|||

|

|

|||

|

|

Выполнил: |

студент группы |

|

|

|

XXX-XX ФИРТ |

||

|

|

Xxxxx X.X. |

||

|

Проверил: |

Xxxxx X.X. |

||

|

|

|||

|

Уфа – 2004 |

|||

Цель работы:

Изучение схемных разновидностей регистров, выполняемых на них микроопераций и овладение методами проектирования регистров.

Краткие теоретические сведения:

Регистром называется упорядоченная

последовательность триггеров,

предназначенная для хранения слов и

выполнения микроопераций над ними.

Микрооперация - это элементарное машинное

действие, в результате которого изменяется

значение слова или осуществляется его

пересылка. Обобщенная структура регистра

представлена на рис. 1, где КС - комбинационная

схема;

![]() - выходы i-х триггеров

(i=1,…,n);

- выходы i-х триггеров

(i=1,…,n);

![]() - функции возбуждения триггеров (например,

- функции возбуждения триггеров (например,

![]() ,

,

![]() ,

,

![]() ,

,

![]() ,

,

![]() ,

,

![]() и т. д.); С и Т - тактирующие входы

соответственно триггеров и регистра,

которые в конкретных схемах могут

отсутствовать.

и т. д.); С и Т - тактирующие входы

соответственно триггеров и регистра,

которые в конкретных схемах могут

отсутствовать.

Число разрядов (триггеров) называют

длиной регистра. Регистр может находиться

в

![]() состояниях, т. е. в него можно записать

состояниях, т. е. в него можно записать

![]() различных слов.

различных слов.

|

|

|

Рисунок 1 - Обобщенная структура регистра |

Различают синхронные и асинхронные

регистры. В синхронных регистрах

микрооперации выполняются по тактирующему

сигналу Т. Настройка регистра на

соответствующую микрооперацию

осуществляется предварительной

установкой на управляющих входах кода

микрооперации

![]() .

Число разрядов в коде определяется из

соотношения

.

Число разрядов в коде определяется из

соотношения

![]() ,

где k - количество

микроопераций.

,

где k - количество

микроопераций.

В асинхронных регистрах тактирующий

вход Т отсутствует. Каждая i-я

микрооперация выполняется под действием

собственного управляющего сигнала

![]() .

Количество таких сигналов равно числу

микроопераций k, т. е. в общем случае

больше, чем разрядов в коде микрооперации

.

Количество таких сигналов равно числу

микроопераций k, т. е. в общем случае

больше, чем разрядов в коде микрооперации

![]() синхронного регистра.

синхронного регистра.

При выполнении микроопераций в каждом

разряде регистра осуществляется

одинаковое преобразование информации.

Характер микрооперации можно описать

через состояния сигналов в момент

времени, предшествующий выполнению

микрооперации (![]() ),

и в момент завершения микрооперации

(

),

и в момент завершения микрооперации

(![]() ).

).

Наиболее часто на регистрах выполняют микрооперации занесения (приема, записи) слова параллельным кодом, сдвига слова, а также установки исходного (обычно нулевого) состояния.

Занесение слова осуществляется через

информационные входы

![]() (i=1,…,n). Для

i-го разряда регистра

можно записать

(i=1,…,n). Для

i-го разряда регистра

можно записать

![]() =

=![]() ,

т. е. при выполнении этой микрооперации

в i-й разряд регистра

записывается значение сигнала на входе

,

т. е. при выполнении этой микрооперации

в i-й разряд регистра

записывается значение сигнала на входе

![]() .

.

Регистры, на которых выполняются

микрооперации сдвига, называются

сдвиговыми. Сдвиг слова может быть

осуществлен влево (в сторону старших

разрядов) или вправо (в сторону младших

разрядов) на i разрядов

одновременно, где i=1,…,n-1.

Регистры, имеющие цепи как левого, так

и правого сдвига, называются реверсивными.

Сдвиг слова влево и вправо, например,

на один разряд можно описать соответственно

как

![]() и

и

![]() .

.

Установка нулевого состояния регистра

(![]() )

осуществляется, как правило, через

асинхронные установочные входы триггеров.

)

осуществляется, как правило, через

асинхронные установочные входы триггеров.

С помощью регистров можно выполнять и

другие преобразования информации,

например, поразрядные логические

операции: конъюнкция (![]() );

дизъюнкция (

);

дизъюнкция (![]() );

неравнозначность (

);

неравнозначность (![]() );

инвертирование разрядов (

);

инвертирование разрядов (![]() )

и т. д.

)

и т. д.

Задание:

1. Построить четырехразрядный синхронный

регистр для выполнения микроопераций,

заданных в табл. 1, где

![]() - сдвиг влево на один разряд;

- сдвиг влево на один разряд;

![]() - сдвиг вправо на один разряд;

- сдвиг вправо на один разряд;

![]() - прием слова параллельным кодом;

- прием слова параллельным кодом;

![]() - дизъюнкция;

- дизъюнкция;

![]() - инвертирование разрядов.

- инвертирование разрядов.

Таблица 1

|

|

|

|

Микрооперации |

||

|

Номер пункта задания |

|||||

|

1 |

2 |

3 |

|||

|

1 |

0 |

1 |

|

|

|

Для построения регистра можно использовать логические элементы, указанные в табл. 2, а также RS-, JK-, Т- или D-триггеры.

Таблица 2

|

|

|

|

Логические элементы |

||

|

Номер пункта задания |

|||||

|

1 |

2 |

3 |

|||

|

1 |

0 |

1 |

2ИЛИ-НЕ |

2И, 3ИЛИ-НЕ |

3И-НЕ |

Значения

![]() в табл. 1 и 2 определяют вариант задания.

Для выбора варианта необходимо его

номер представить в двоичной системе

счисления и обозначить шесть младших

разрядов в виде слова

в табл. 1 и 2 определяют вариант задания.

Для выбора варианта необходимо его

номер представить в двоичной системе

счисления и обозначить шесть младших

разрядов в виде слова

![]() .

.

5 = (101)2;

![]()

![]()

![]()

Определить требуемую организацию

триггеров (с внутренней задержкой или

без внутренней задержки) и построить

схему регистра с цепями выдачи прямого

кода. Предусмотреть установку регистра

в нулевое состояние, используя асинхронные

входы

![]() .

С помощью временной диаграммы определить

параметры регистра t и f,

обозначив задержку сигналов логическими

элементами через

.

С помощью временной диаграммы определить

параметры регистра t и f,

обозначив задержку сигналов логическими

элементами через

![]() ,

а время переключения триггера как

,

а время переключения триггера как

![]() .

.

2. Построить 4-разрядный синхронный регистр в соответствии с табл. 3 и 4, выполнив этапы, аналогичные п.1 задания. Регистр должен иметь выводы с тремя состояниями. Для построения регистра использовать асинхронные RS-, JК- или Т-триггеры.

3. Аналогично требованиям п.1 и п.2 задания выполнить синтез 4-разрядного асинхронного регистра на асинхронных RS-, JK-или Т-триггерах в соответствии с табл. 3 и 4. Предусмотреть в регистре цепи выдачи информации в прямом и обратном коде.

Выполнение:

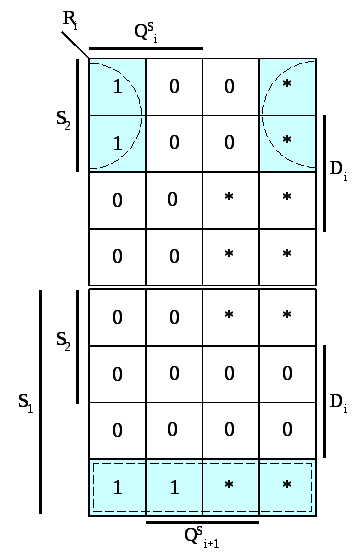

1. Построим четырехразрядный регистр

для выполнения микроопераций y2

(![]() )

– сдвиг слова вправо на один разряд, y3

(

)

– сдвиг слова вправо на один разряд, y3

(![]() =

=![]() )

– прием слова параллельным кодом, y4

(

)

– прием слова параллельным кодом, y4

(![]() )

– дизъюнкция. Для построения регистра

используем логические элементы 2ИЛИ-НЕ,

а также RS-, JK-,

Т- или D-триггеры.

)

– дизъюнкция. Для построения регистра

используем логические элементы 2ИЛИ-НЕ,

а также RS-, JK-,

Т- или D-триггеры.

|

Коды микроопераций

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||