- •Питання контролю спз

- •Класифікація програмного забезпечення обчислювальних систем. Предмет та задачі спз.

- •Еволюція спз.

- •Призначення та склад операційних систем.

- •Основні принципи розробки системного програмного забезпечення.

- •Стратегії планування.

- •Дисципліни диспетчеризації.

- •3. Алгоритми в диспетчеризації з витісненням та без.

- •4. Способи забезпечення гарантованого обслуговування процесів.

- •6. Вплив планування на ефективність обчислювальних систем.

- •7. Використання динамічних пріоритетів.

- •1. Незалежні та взаємодіючі обчислювальні процеси.

- •2. Види задач синхронізації паралельних процесів.

- •3. Синхронізація за допомогою блокування пам’яті.

- •5. Команда “перевірка” та “встановлення”.

- •6. Використання семафорів для синхронізації та впорядкування паралельних процесів.

- •7. Монітороподібні засоби синхронізації паралельних процесів.

- •8. Поштові ящики.

- •9. Конвеєри.

- •10. Черги повідомлень.

- •Підходи до керування реальною пам’яттю.

- •Неперервний розподіл оперативної пам’яті.

- •Розподіл з перекриттям.

- •Статичний розподіл пам’яті.

- •Динамічний розподіл пам’яті.

- •Структура, основні принципи віртуалізації пам’яті.

- •1. Реальний і захищений режими роботи процесора.

- •Мал. 3.1 Схема визначення фізичної адреси для процесора 8086.

- •2. Нові системні регістри мікропроцесорів і80x86.

- •Мал. 7.2 Основні системні регістри мікропроцесорів і80x86.

- •4. Підтримка сторінкового способу організації віртуальної пам'яті.

- •Мал. 7 Дескриптор сторінки.

- •6. Захист адресного простору задач.

- •Якщо цільовий сегмент є сегментом стека, то правило перевірки має вид

- •1. Основні поняття і визначення процесу вводу/виводу.

- •2. Режими керування вводом/виводом.

- •Керування вводом/виводом.

- •3. Закріплення пристроїв, загальні пристрої вводу/виводу.

- •4. Основні системні таблиці вводу/виводу.

- •Процес управління вводом/виводом.

- •Синхронний і асинхронний ввід/вивід.

- •6. Кешування операцій вводу/виводу при роботі з накопичувачами на магнітних дисках.

- •Файлові системи fat, vfat, fat32, hpfs.

- •Структура системи файлів.

- •Файлова система ntfs (New Technology File System)

Мал. 7.2 Основні системні регістри мікропроцесорів і80x86.

Керуючий регістр CR0 містить цілий ряд флагів, що визначають режими роботи мікропроцесора. Самий молодший біт (РЕ, protect enable) цього регістра визначає режим роботи процесора. При РЕ=0 процесор функціонує в реальному режимі роботи, а при одиничному значенні мікропроцесор переключається в захищений режим. Самий старший біт регістра CR0 (біт PG, paging) визначає, включений (PG=1) чи немає (PG=0) режим сторінкового перетворення адрес.

Регістр CR2 призначений для розміщення в ньому адреси підпрограми обробки сторінкового виключення, тобто у випадку використання сторінкового механізму відображення пам'яті звертання до відсутньої сторінки буде викликати перехід на відповідну підпрограму диспетчера пам'яті, і для визначення цієї підпрограми буде задіяний регістр CR2. Регістр CR3 містить номер фізичної сторінки, у якій розташовується таблиця каталогів таблиць сторінок поточної задачі. Очевидно, що, приписавши до цього номера нулі, ми потрапимо на початок цієї сторінки.

4. Підтримка сторінкового способу організації віртуальної пам'яті.

При створенні мікропроцесора i80386 розробники зштовхнулися з дуже серйозною проблемою в реалізації сторінкового механізму. Справа в тім, що мікропроцесор має широку шину адресу — 32 біта — і виникає питання про розбивку всієї адреси на поле сторінки і поле індексу. Якщо велику кількість бітів адреси відвести під індекс, то сторінки стануть дуже великими, що спричинить великі втрати і на фрагментацію, і на операції введення/виведення, зв'язані з заміщенням сторінок. Хоча кількість сторінок сталася б при цьому менше, і накладні витрати при їхній підтримці теж би зменшилися. Якщо ж розмір сторінки зменшити, то велике поле номера-сторінки привело б до появи величезної кількості можливих сторінок і необхідно було або вводити якісь механізми контролю за номером сторінки (для того, щоб він не виходив за розміри таблиці сторінок), або створювати ці таблиці максимально можливого розміру. Розробники пішли по шляху, при якому розмір сторінки все-таки невеликий (він обраний рівним 212 = 4096 = 4К), а поле номера сторінки завбільшки 20 бітів, у свою чергу, розбивається на два поля і здійснюється двохетапна (двохкрокова) сторінкова трансляція.

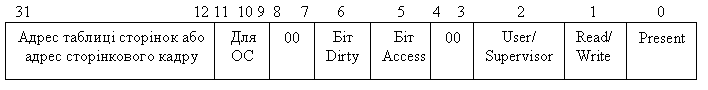

Для опису кожної сторінки створюється відповідний дескриптор. Довжина дескриптора обрана рівною 32 бітам: 20 бітів лінійної адреси визначають номер сторінки (власне кажучи — її адресу, оскільки додавання до нього (приписування як молодші розряди) 12 нулів приводить до визначення початкової адреси сторінки), а інші біти розбиті на наступні поля, що зображені на мал. 7. Як видно, три біти дескриптора зарезервовані для використання системними програмістами при розробці підсистеми організації віртуальної пам'яті. З цими бітами мікропроцесор сам не працює.

Мал. 7 Дескриптор сторінки.

6. Захист адресного простору задач.

Для можливості створення надійних мультипрограмних ОС у процесорах сімейства і80x86 є кілька механізмів захисту. Це і поділ адресних просторів задач, і введення рівнів привілеїв для сегментів коду і сегментів даних. Усе це дозволяє забезпечити як захист задач одна від одної, так і захист самої операційної системи від прикладних задач, захист однієї частини ОС від інших її компонентів, захист самих задач від деяких своїх власних помилок.

Захист адресного простору задач здійснюється відносно легко за рахунок того, що кожна задача може мати свій власний локальний адресний простір. Операційна система повинна коректно маніпулювати таблицями трансляції сегментів (дескрипторними таблицями) і таблицями трансляції сторінкових кадрів. Самі таблиці дескрипторів як сегменти даних (а відповідно, у свою чергу, і як сторінкові кадри) відносяться до адресного простору операційної системи і мають відповідні привілеї доступу; виправляти їх задачі не можуть. Цими інформаційними структурами процесор користується сам, на апаратному рівні, без можливості їх читати і редагувати з користувацьких додатків. Якщо використовується модель плоскої пам'яті, то можливість мікропроцесора контролювати звертання до пам'яті тільки усередині поточного сегмента фактично не використовується, і залишається в основному тільки механізм відображення сторінкових кадрів. Вихід за межі сторінкового кадру неможливий, тому фіксується тільки вихід за межі свого сегмента. У цьому випадку приходиться покладатися тільки на систему програмування, що повинна коректно розподіляти програмні модулі в межах єдиного неструктурованого адресного простору задачі. Тому при створенні багатопотокових додатків, коли кожна задача (у даному випадку — потік) може зіпсувати адресний простір іншої задачі, ця проблема стає дуже складною, особливо якщо не використовувати системи програмування на мовах високого рівня.

Однак для організації взаємодії задач, що мають різні віртуальні адресні простори, необхідно, як ми вже говорили, мати загальний адресний простір. І тут, для забезпечення захисту самої ОС, а виходить, і підвищення надійності всіх обчислень, використовується механізм захисту сегментів за допомогою рівнів привілеїв.

Рівні привілеїв для захисту адресного простору задач.

Для того щоб заборонити користувацьким задачам модифікувати області пам'яті, що належать самій ОС, необхідно мати спеціальні засоби. Одного розмежування адресних просторів через механізм сегментів мало, тому що можна вказувати різні значення адреси початку сегмента і тим самим одержувати доступ до чужих сегментів. Іншими словами, необхідно в явному виді розмежовувати системні сегменти даних і коду від сегментів, що належать користувацьким програмам. Тому були введені два основних режими роботи процесора: користувача і супервізора. Більшість сучасних процесорів мають принаймні два цих режими. Так, у режимі супервізора програма може виконувати всі дії і мати доступ до будь-яких адресів, тоді як у режимі користувача повинні бути обмеження, для того щоб виявляти і припиняти заборонені дії, перехоплюючи їхній і передаючи керування супервізору ОС. Часто і режиму користувача забороняється виконання команд введення/виведення і деяких інших, щоб гарантувати, що тільки ОС виконує ці операції. Можна сказати, що ці два режими мають різні рівні привілеїв.

У мікропроцесорах i80x86 маються не два, а чотири рівні привілеїв. Часто рівні привілеїв називають кільцями захисту, оскільки це іноді допомагає пояснити принцип дії самого механізму; тому говорять, що деякий програмний модуль «виконується в кільці захисту з таким-то номером». Для вказівки рівня привілеїв використовуються два біти, тому код 00 позначає самий вищий рівень, а код 11 (=3) — самий нижчий. Найвищий рівень привілеїв призначений для операційної системи (насамперед, для ядра ОС), найнижчий — для прикладних задач користувача. Проміжні рівні привілеїв введені для більшої свободи системних програмістів в організації надійних обчислень при створенні ОС і іншого системного ПЗ. Передбачалося, що рівень з номером (кодом) 1 може бути використаний, наприклад, для системного сервісу — програм обслуговування апаратури, драйверів, що працюють з портами введення/виведення. Рівень привілеїв з кодом 2 може бути використаний для створення користувацьких інтерфейсів, систем керування базами даних і т.п., тобто для реалізації спеціальних системних функцій, що стосовно супервізора ОС поводяться як звичайні додатки. Так, наприклад, система OS/2 використовує три рівні привілеїв: з нульовим рівнем привілеїв виконується код самої ОС, на другому рівні виповнюються системні процедури підсистеми введення/виведення, на третьому рівні виповнюються прикладні задачі користувачів. Однак найчастіше на практиці використовуються тільки два рівні — нульової і третій. Таким чином, згаданий режим супервізора для мікропроцесорів і80x86 відповідає виконанню коду з рівнем привілеїв 0 (його позначають так: PL0 – privilege level). Підводячи підсумок, можна констатувати, що саме рівень привілеїв задач визначає, які команди в них можна використовувати і яка підмножина сегментів і/чи сторінок у їхньому адресному просторі вони можуть обробляти.

Основними системними об'єктами, якими маніпулює процесор при роботі в захищеному режимі, є дескриптори. Дескриптори сегментів містять інформацію про рівень привілею відповідного сегмента чи коду даних. Рівень привілею задачі, що виконується, визначається значенням поля привілею, що знаходиться в дескрипторі її поточного кодового сегмента. Нагадаємо, що в кожнім дескрипторі сегмента (див. мал.3.3) мається поле DPL у байті прав доступу, що і визначає рівень привілею зв'язаного з ним сегмента. Таким чином, поле DPL поточного сегмента коду стає полем CPL. При звертанні до якого-небудь сегмента і відповідному селекторі вказується запитуваний рівень привілеїв RPL (див. мал. 3.4).

У межах однієї задачі використовуються сегменти з різним рівнем привілею й у визначені моменти часу виконуються чи обробляються сегменти з відповідними їм рівнями привілею. Механізм перевірки привілеїв працює в ситуаціях, які можна назвати міжсегментними переходами (звертаннями). Це доступ до сегмента даних чи стековому сегменту, міжсегментні передачі керування у випадку переривань (і особливих ситуацій), при використанні команд CALL, JMP, INT, IRET, RET. У таких міжсегментних звертаннях беруть участь два сегменти: цільовий сегмент (до якого ми звертаємося) і поточний сегмент коду, з якого йде звертання.

Процесор порівнює згадані значення CPL, RPL, DPL і на основі поняття ефективного рівня привілеїв (EPL = max (RPL, DPL)) обмежує можливості доступу до сегментів за наступними правилами, у залежності від того, чи йде мова про звертання до коду чи до даних.

При доступі до сегментів даним перевіряється умова CPL <= EPL Порушення цієї умови викликає так звану особливу ситуацію помилки захисту і виникає переривання. Рівень привілею сегмента даних, до якого здійснюється звертання, повинний бути таким же, як і поточний рівень, чи менше його. Звертання до сегмента з більш високим рівнем привілею сприймається як помилка, тому що існує небезпека зміни даних з високим рівнем привілеїв у програмі з низьким рівнем привілею. Доступ до даних з меншим рівнем привілею дозволяється.