Электроника Коллектив кафедры Электроника, БГУИР 2014 (Мет пособие)

.pdf

|

6 |

IN74HCT374A |

IN74HCT533A |

IN74HCT534A |

|

|

|

|

|

|

5 |

IN74HC374A |

IN74HC533A |

IN74HC534A |

|

|

|

|

|

|

4 |

IN74ACT374 |

IN74ACT533 |

IN74ACT534 |

|

|

|

|

|

|

3 |

IN74AC374 |

IN74AC533 |

IN74AC534 |

|

|

|

|

|

|

2 |

ИР23 |

ИР40 |

ИР41 |

Продолжение таблицы Б.1 |

|

|

|

|

1 |

16 Восьмиразрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с тремя состояниями выхода |

17 Восьмиразрядный регистр, управляемый по уровню, с параллельным вводом-выводом данных, с тремя состояниями и инверсией на выходе |

18 Восьмиразрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с тремя состояниями и инверсией на выходе |

Задача 3

Разработайте логическую схему КЦУ, заданного в таблице 6.

Таблица 6 – Исходные данные к задаче 3

Номер |

Наименование КЦУ |

Базис |

варианта |

|

|

|

|

|

1 |

2 |

3 |

|

|

|

1 |

Преобразователькода8421 вкод«сизбытком3» |

И-НЕ |

|

|

|

2 |

Мультиплексор на восемь входов без стробирова- |

И-ИЛИ-НЕ |

|

ния |

|

|

|

|

3 |

Дешифратор кода 2421 на десять выходов со |

И-НЕ |

|

стробированием |

|

|

|

|

4 |

Шифратор для преобразования десятичных цифр в |

И, ИЛИ, НЕ |

|

код «с избытком 3» со стробированием |

|

|

|

|

5 |

Дешифратор кода 7421 на десять выходов со |

И-НЕ |

|

стробированием |

|

|

|

|

6 |

Преобразователь кода 7421 в код 2421 |

И-НЕ |

|

|

|

7 |

Шифратор для преобразования десятичных цифр в |

И, ИЛИ, НЕ |

|

код 7421 со стробированием |

|

|

|

|

88 |

21 |

Окончание таблицы 6

1 |

2 |

3 |

8 |

Мультиплексор на восемь входов со стробирова- |

И-ИЛИ-НЕ |

|

нием |

|

|

|

|

9 |

Дешифратор кода «с избытком 3» на десять выхо- |

И-НЕ |

|

дов со стробированием |

|

|

|

|

10 |

Преобразователь кода «с избытком 3» в код 8421 |

И-НЕ |

|

|

|

1Дайте определение и поясните назначение заданного КЦУ.

2Приведите его условное графическое обозначение и поясните назначение выводов.

3Составьте таблицу истинности для заданного КЦУ.

4Запишите логические функции для выходов заданного КЦУ в базисе И, ИЛИ, НЕ (для преобразователей кодов логические функции минимизировать табличным методом с помощью карт Карно).

5Запишите полученные логические функции в базисе, заданном в таблице 6.

6Постройте логическую схему КЦУ в базисе, заданном в табли-

це 6.

7Проверьте правильность функционирования построенной логической схемы КЦУ для четвертой строки таблицы истинности.

Методические указания по выполнению задачи 3

Взадаче 3 рассматриваются следующие типовые КЦУ: преобразователи кодов, мультиплексоры, шифраторы и дешифраторы.

Ввариантах 1,6 и 10 задачи 3 требуется синтезировать в базисе И-НЕ схемы преобразователей кодов. В учебниках [1, С. 117-120] и [2, С. 188-190] приведены примеры синтеза преобразователя кода 8421 в код 2421 и обратно. Причем минимизация логических функций выполнена табличным методом с помощью карт Вейча. Рассмотрим пример синтеза преобразователя кода 8421 в код 2421 при минимизации логических функций с помощью карт Карно, которые более удобны и нашли более широкое практическое применение. Условное графическое обозначение такого преобразователя кода представлено на рисунке 6.

|

6 |

– |

– |

IN74HCT273A |

– |

IN74HCT373A |

|

|

|

|

|

|

|

|

5 |

IN74HC192A |

IN74HC193A |

IN74HC273A |

IN74HC279A |

IN74HC373A |

|

|

|

|

|

|

|

|

4 |

IN74ACT192 |

IN74ACT193 |

IN74ACT273 |

– |

IN74ACT373 |

|

|

|

|

|

|

|

|

3 |

IN74AC192 |

IN74AC193 |

IN74AC273 |

– |

IN74AC373 |

|

|

|

|

|

|

|

|

2 |

ИЕ6 |

ИЕ7 |

ИР35 |

ТР2 |

ИР22 |

Продолжение таблицы Б.1 |

|

|

|

|

|

|

1 |

11 Четырехразрядный двоично-десятичный реверсивный счетчик с параллельной загрузкой |

12 Четырехразрядный двоичный реверсивный счетчик с параллельной загрузкой |

13 Восьмиразрядный регистр, управляемый по фронту с параллельным вводом-выводом, с входом сброса |

14 Четыре RS-триггера |

15 Восьмиразрядный регистр, управляемый по уровню, с параллельным вводом-выводом данных, с тремя состояниями на выходе |

22 |

87 |

Продолжение таблицы Б.1

86

6 |

IN74HCT163A |

IN74HCT164A |

IN74HCT165A |

|

|

|

|

5 |

IN74HC163A |

IN74HC164A |

IN74HC165A |

|

|

|

|

4 |

IN74ACT163 |

IN74ACT164 |

– |

|

|

|

|

3 |

IN74AC163 |

IN74AC164 |

– |

|

|

|

|

2 |

ИЕ18 |

ИР8 |

ИР9 |

|

|

|

|

1 |

6 Четырехразрядный двоичный счетчик с синхронной установкой в «логический 0» |

7 Восьмиразрядный последовательный сдвиговый регистр с параллельными выходами |

8 Восьмиразрядный сдвиговый регистр с последовательным и параллельным вводом, по- |

|

|

|

|

|

IN74HCT174A |

– |

|

|

|

|

IN74HC174A |

IN74HC175A |

|

|

|

|

IN74ACT174 |

IN74ACT175 |

|

|

|

|

IN74AC174 |

IN74AC175 |

|

|

|

|

ТМ9 |

ТМ8 |

|

|

|

следовательным выводом информации |

9 Шесть D-триггеров с общими входами управления и сброса |

10 Четыре D-триггера с общими входами управления и сброса |

|

|

|

X |

|

|

|

|

Y |

|

1 |

1 |

X/Y |

1 |

1 |

||

X |

2 |

Y |

||||

|

|

|

||||

|

2 |

|

2 |

2 |

||

X |

3 |

|

Y |

|||

|

|

|

||||

|

4 |

|

4 |

3 |

||

X |

|

|

Y |

|||

4 |

8 |

|

2 |

|||

|

|

4 |

||||

|

|

|

|

|

|

|

Рисунок 6 – Условное графическое обозначение преобразователя кода

8421 в код 2421

Закон функционирования преобразователя кода представлен в таблице 7.

Таблица 7 – Таблица истинности преобразователя кода 8421 в код

2421

Десятичное |

|

Код 8421 |

|

|

Код 2421 |

|

||

число |

X4 |

X3 |

X2 |

X1 |

Y4 |

Y3 |

Y2 |

Y1 |

|

||||||||

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

4 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

5 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

6 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

7 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

9 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

На основании таблицы истинности преобразователя кодов заполним карты Карно (рисунок 7) и запишем логические функции для выходов Y1 ,…, Y4 в МДНФ.

23

X2X1 |

|

|

|

|

X4X3 |

00 |

01 |

11 |

10 |

|

||||

00 |

0 |

1 |

1 |

0 |

01 |

0 |

1 |

1 |

0 |

Y1 : |

Ф |

Ф |

Ф |

Ф |

11 |

||||

10 |

0 |

1 |

Ф |

Ф |

|

|

Y1 X1. |

|

|

X2X1 |

|

|

|

|

X4X3 |

00 |

01 |

11 |

10 |

|

||||

00 |

0 |

0 |

1 |

1 |

01 |

0 |

1 |

0 |

0 |

Y2 : |

Ф |

Ф |

Ф |

Ф |

11 |

||||

10 |

1 |

1 |

Ф |

Ф |

|

Y2 X4 X2 X3 X1 X2 X3. |

|||

Рисунок 7 – Карты Карно для преобразователя кода 8421 в код 2421

24

ПРИЛОЖЕНИЕ Б (справочное) |

Номенклатура и основные электрические параметры микросхем стандартной логики схемотехники КМОП производства НПО «Интеграл» |

Таблица Б.1 – Номенклатура микросхем стандартной логики схемотехники КМОП производства НПО «Интеграл» |

|

5564 (IN74HCT) |

6 |

IN74HCT74A |

– |

– |

– |

– |

|

|

|

|

|

|

|

|

|

|

Серии микросхем |

1564 (IN74HC) |

5 |

IN74HC74A |

IN74HC75A |

IN74HC109A |

IN74HC112A |

IN74HC161A |

|

1594 (IN74ACT) |

4 |

IN74ACT74 |

– |

IN74ACT109 |

IN74ACT112 |

IN74ACT161 |

||

|

|

|

|

|

|

|

|

|

|

1554 (IN74AC) |

3 |

IN74AC74 |

– |

IN74AC109 |

IN74AC112 |

IN74AC161 |

|

Подгруппа и вид по ГОСТ 17021–88 |

2 |

ТМ2 |

ТМ7 |

ТВ15 |

ТВ9 |

ИЕ10 |

||

|

|

|

|

|

|

|

|

|

Функциональное назначение |

1 |

1 Два D-триггера с установкой и сбросом |

2 Четыре D-триггера с прямым и инверсным выходами |

3 Два JK-триггера |

4 Два JK-триггера |

5 Четырехразрядный двоичный счетчик с асинхронной установкой в состояние «логический 0» |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

85 |

|

Окончание таблицы А.3 |

|

X2X1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

X4X3 |

00 |

01 |

11 |

10 |

39 |

Такт |

CLK |

|

||||

40 |

Управление |

C |

00 |

0 |

0 |

0 |

0 |

41 |

Установка в «1» |

SET или S |

|

|

|

|

|

42 |

Установка JK-триггера: |

|

01 |

1 |

0 |

1 |

1 |

|

– в состояние «логическая 1» |

J |

|||||

|

Y3 : |

|

|

|

|

||

|

– в состояние «логический 0» |

K |

Ф |

Ф |

Ф |

Ф |

|

43 |

Функция |

F |

11 |

||||

|

|

|

|

|

|||

44 |

Обозначение основных меток выводов, не несу- |

|

10 |

1 |

1 |

Ф |

Ф |

|

щих логической информации: |

VCC или U |

|||||

|

– вывод напряжения от источника питания |

|

|

|

|

|

|

|

– общий вывод, земля, корпус |

GND |

|

Y3 X4 X2 X3 X1 X3. |

|||

|

– вывод для подключения конденсатора |

CX |

X2X1 |

|

|

|

|

|

– вывод для подключения резистора |

X |

|

|

|

|

|

|

– вывод для подключения индуктивности |

LX |

X4X3 |

|

|

|

|

|

– вывод для подключения кварцевого резонатора |

BQ |

|

00 |

01 |

11 |

10 |

|

|

|

00 |

0 |

0 |

0 |

0 |

|

|

|

01 |

0 |

1 |

1 |

1 |

|

|

|

Y4 : |

Ф |

Ф |

Ф |

Ф |

|

|

|

11 |

||||

|

|

|

10 |

1 |

1 |

Ф |

Ф |

|

|

|

|

|

Y4 X4 X1 X3 X2 X3. |

||

Окончание рисунка 7

Y1 X1; |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Y2 X4 X2 X 3 X1 X 2 |

X3 |

|

|||||||

; |

(3) |

||||||||

Y3 X4 X2 X3 |

|

1 X3; |

|

|

|||||

X |

|

|

|

||||||

Y4 X4 X1 X3 X2 X3. |

|

|

|

||||||

|

|

|

|||||||

84 |

25 |

Преобразуем логические функции (3) в базис И-НЕ, используя правило де Моргана.

Y1 X1;

Y2 X4 X2 X 3 X1 X 2 X3

X 4 X2 X 3 X1 X 2 X3

X 4 | (X2 | X 3 ) | (X1 | X 2 | X3 );

Для остальных выходов аналогично:

Y3 X 4 | (X2 | X3 ) | (X1 | X3 ); Y4 X 4 | (X1 | X3 ) | (X2 | X3 ).

(4)

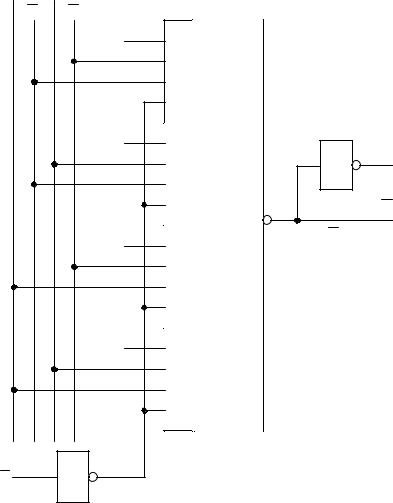

Логическая схема преобразователя кода 8421 в код 2421 в базисе И-НЕ, построенная по логическим функциям (4), представлена на рисунке 8.

Для проверки правильности функционирования логической схемы преобразователя кода проставим на выходах логических элементов значения сигналов для входного кодового слова 0011. Поскольку на выходах схемы устанавливается кодовое слово 0011, то преобразователь кода функционирует в соответствии с таблицей истинности.

Следует помнить, что проверка правильности функционирования только по одному входному набору является неполной.

Методика синтеза преобразователей кодов, заданных в вариантах 1, 6 и 10, аналогична. Для составления таблицы истинности следует использовать данные таблицы 8.

26

Продолжение таблицы А.3

|

1 |

2 |

16 |

Данные: |

D |

|

– входные |

DIN |

|

– выходные |

DOUT |

|

– последовательные |

D→, D← |

17 |

Загрузка (разрешение параллельной записи) |

LD |

18 |

Заем: |

BI |

|

– вход, принимающий заем |

|

|

– выход, выдающий заем |

BO |

19 |

Запись (команда записи) |

WR |

20 |

Ожидание |

WAIT |

21 |

Останов |

STOP |

22 |

Очистка |

CLR |

23 |

Ошибка |

ERR |

24 |

Передача |

TX |

25 |

Перенос: |

|

|

– вход, принимающий перенос |

CI |

|

– выход, распространяющий перенос |

CO |

26 |

Переполнение |

OF |

27 |

Подтверждение приема |

ACK |

28 |

Прерывание: |

INT |

|

подтверждение прерывания |

INTA |

29 |

Прием |

RX |

30 |

Разрешение |

EN |

31 |

Разрешение прохождения импульсов (работы цепи) |

CE |

32 |

Разрешение третьего состояния |

EN |

33 |

Режим |

M |

34 |

Сброс: |

SR |

|

– общий |

|

|

– обнуление |

RES или R |

35 |

Сдвиг: |

SH |

|

– слева направо (от старшего разряда к младшему) |

→n |

|

– справа налево (от младшего разряда к старшему) |

n← |

|

Примечание – При n = 1 это значение может быть |

|

|

опущено |

|

36 |

Синхронизация |

SYNC |

37 |

Строб (сигнал выборки) |

STR |

38 |

Считывание (чтение) |

RD |

83

Функциональное назначение выводов элемента обозначают при помощи меток выводов. Метку вывода образуют из прописных букв латинского алфавита, арабских цифр и (или) специальных знаков, записанных в одной строке без пробелов. Обозначения основных меток выводов цифровых элементов приведены в таблице А.3.

Таблица А.3 – Обозначения основных меток выводов цифровых элементов по ГОСТ 2.743-91

|

Наименование |

Обозначение |

|

1 |

2 |

1 |

Адрес |

ADR или A |

2 |

Байт |

BY |

3 |

Ввод (информации) |

I |

3 |

Вход обратного счета (вход уменьшения) |

– n или DOWN |

4 |

Вход операнда, над которым выполняется одна или |

Pn |

|

несколько математических операций |

+ n или UP |

5 |

Вход прямого счета (вход увеличения) |

|

|

Примечания к пунктам 3 и 5 – Параметр n следует |

|

|

заменить значением, на которое увеличивается или |

|

|

уменьшается содержимое счетчика |

T |

6 |

Вход, вызывающий изменение состояния на выходе |

|

|

элемента в дополнительное, каждый раз, когда он |

|

|

принимает состояние «логическая 1» (счетный вход) |

|

7 |

Выбор (селекция) |

SEL |

8 |

Выбор адреса: |

|

|

– столбца |

CAS |

|

– строки |

RAS |

9 |

Выбор кристалла (доступ к памяти) |

CS |

10 Вывод (информации) |

O |

|

11 Вывод двунаправленный |

< > или ↔ |

|

12 Выход с открытым коллектором или стоком |

|

|

|

(например, открытый коллектор n-p-n транзистора, |

|

|

открытый сток n-канала) |

|

13 Выход с открытым эмиттером или истоком |

|

|

|

(например, открытый эмиттер n-p-n транзистора, |

|

|

открытый исток n-канала) |

|

14 Выход с тремя состояниями |

|

|

15 Готовность |

RDY |

|

82 |

|

|

X4 X3 X2 X1

0 0 1 1

|

|

|

Y1 |

|

X2 |

X1|X2 |

|X3 |

1 |

|

Y2 |

||||

0 |

1 |

|

||

|

|

|

1 |

|

X3 |

X2 |X3 |

|

||

1 |

0 |

|

|

|

X4 |

|

|

|

|

1 |

|

|

|

|

X1 |

X1|X3 |

|

Y3 |

|

1 |

|

0 |

||

0 |

|

|||

|

|

|

||

|

X2 |X3 |

|

|

|

|

1 |

|

|

|

|

X1|X3 |

|

Y4 |

|

|

|

0 |

||

|

1 |

|

|

|

Рисунок 8 – Логическая схема преобразователя кода 8421 в код 2421 в базисе И-НЕ

27

Таблица 8 – Двоично-десятичные коды

Десятичное |

|

Двоично-десятичные коды |

|

||

число |

8421 |

2421 |

7421 |

|

«с избытком 3» |

0 |

0000 |

0000 |

0000 |

|

0011 |

1 |

0001 |

0001 |

0001 |

|

0100 |

2 |

0010 |

0010 |

0010 |

|

0101 |

3 |

0011 |

0011 |

0011 |

|

0110 |

4 |

0100 |

0100 |

0100 |

|

0111 |

5 |

0101 |

1011 |

0101 |

|

1000 |

6 |

0110 |

1100 |

0110 |

|

1001 |

7 |

0111 |

1101 |

1000 |

|

1010 |

8 |

1000 |

1110 |

1001 |

|

1011 |

9 |

1001 |

1111 |

1010 |

|

1100 |

Примечание – Код «с избытком 3» часто называют кодом 8421+3

В вариантах 2 и 8 задачи 3 требуется синтезировать в базисе И- ИЛИ-НЕ схему мультиплексора на восемь каналов (мультиплексоры называют коммутаторами каналов). Рассмотрим пример синтеза мультиплексора на четыре канала со стробированием. Условное графическое обозначение мультиплексора и назначение выводов представлено в [1, С. 123-125] и [3, С. 141-144]. Таблица истинности мультиплексора представлена в таблице 9.

Таблица 9 – Таблица истинности мультиплексора на четыре канала со стробированием

|

Адресные входы |

Стробирующий |

Выход |

|||

|

|

|

сигнал |

|

||

A1 |

|

A0 |

|

|

|

Q |

|

E |

|||||

X |

|

X |

1 |

|

0 |

|

0 |

|

0 |

0 |

|

D0 |

|

0 |

|

1 |

0 |

|

D1 |

|

1 |

|

0 |

0 |

|

D2 |

|

1 |

|

1 |

0 |

|

D3 |

|

Примечание – Знаком «X» обозначен произвольный уровень сигнала – 0 или 1

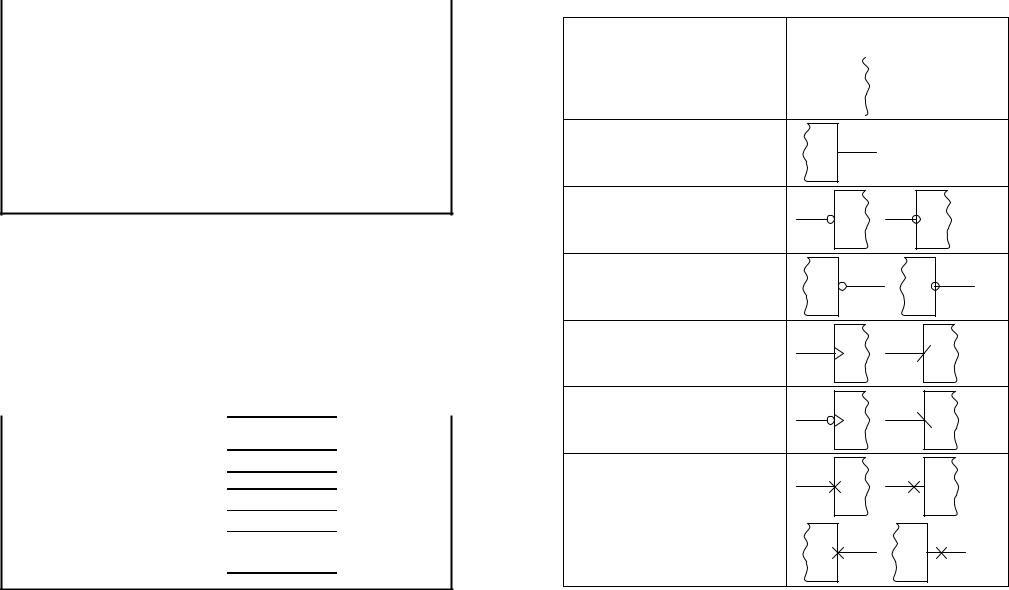

Таблица А.2 – Основные обозначения указателей выводов цифровых элементов по ГОСТ 2.743-91

Наименование |

Обозначение |

|||

1 |

|

2 |

||

1 Прямой статический вход |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

2 Прямой статический выход

3 Инверсный статический вход

4 Инверсный статический выход

5 Прямой динамический вход

6 Инверсный динамический вход

7 Вывод, не несущий логической информации

28 |

81 |

Окончание таблицы А.1 |

|

|

|

|

|

2 |

|

1 |

3 |

||

|

– индуктивностей |

*L |

|

|

– диодов |

*D |

|

|

– транзисторов |

*T |

|

|

– трансформаторов |

*TR |

|

|

– предохранителей |

*FU |

|

При необходимости указать сложную функцию элемента допускается составное обозначение функции. Например, если элемент выполняет несколько функций, то обозначение его сложной функции образовано из нескольких более простых обозначений функций, выполняемых элементом:

–четырехразрядный двоичный счетчик с модулем счета 16 CTRDIV16;

–преобразователь/усилитель двоично-десятичного кода в семисегментный код BCD/7SEG.

Выводы цифровых элементов подразделяют на несущие и не несущие логическую информацию.

Выводы, несущие логическую информацию, подразделяют на статические и динамические, а также на прямые и инверсные.

На прямом статическом выводе двоичная переменная имеет значение «1», если сигнал на этом выводе в активном состоянии находится в состоянии «логическая 1» в принятом логическом соглашении.

На инверсном статическом выводе двоичная переменная имеет значение «1», если сигнал на этом выводе в активном состоянии находится в состоянии «логический 0» в принятом логическом соглашении.

На прямом динамическом выводе двоичная переменная имеет значение «1», если сигнал на этом выводе изменяется из состояния «логический 0» в состояние «логическая 1» в принятом логическом соглашении.

На инверсном динамическом выводе двоичная переменная имеет значение «1», если сигнал на этом выводе изменяется из состояния «логическая 1» в состояние «логический 0» в принятом логическом соглашении.

Свойства выводов на УГО цифровых элементов обозначают указателями (таблица А.2).

Из таблицы истинности следует, что при отсутствии стробирую-

щего (разрешающего) сигнала ( E =1) на выходе мультиплексора Q устанавливается нулевой сигнал независимо от кода на адресных вхо-

дах A1 , A0 . При поступлении стробирующего сигнала ( E =0) на выход мультиплексора Q передается сигнал с того информационного входа D0 … D3 , номер которого указан на адресных входах A1 , A0 .

На основании таблицы истинности мультиплексора запишем логическую функцию для выхода Q в совершенной дизъюнктивной нормальной форме (СДНФ):

Q (D0 A1 A 0 D1 A1 A0 D2 A1 A 0 D3 A1 A0 ) E. (5)

По логической функции (5) можно построить логическую схему мультиплексора в базисе И, ИЛИ, НЕ, однако, более простой логическая схема мультиплексора будет в базисе И-ИЛИ-НЕ. Для преобразования логической функции (5) в базис И-ИЛИ-НЕ следует проинвертировать левую и правую части равенства:

Q (D0 A1 A 0 D1 A1 A0 D2 A1 A 0 D3 A1 A0 ) E. (6)

Из логической функции (6) следует, что в базисе И-ИЛИ-НЕ мультиплексор будет иметь инверсный выход, поэтому для получения прямого выхода к его выходу следует подключить инвертор.

Логическая схема мультиплексора в базисе И-ИЛИ-НЕ, построенная по логической функции (6), представлена на рисунке 9.

Для проверки правильности функционирования логической схемы мультиплексора проставим значения сигналов для адресного кода 11. Поскольку на выход схемы Q передается сигнал со входа D3, то мультиплексор функционирует в соответствии с таблицей истинности.

Синтез мультиплексора, заданного в вариантах 2 и 8, следует выполнять по вышеприведенной методике.

В вариантах 3, 5 и 9 задачи 3 требуется синтезировать схему дешифратора в базисе И-НЕ со стробированием, т.е. с разрешающим

входом E .

80 |

29 |

A1 |

|

A0 |

|

|

|

|

A1 |

|

A0 |

& |

1 |

|

|

|

D0 |

||

|

|

|

|

0 |

|

|

|

|

|

0 |

|

|

|

|

|

1 |

|

|

|

|

D1 |

& |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

1 |

|

|

|

|

D2 |

& |

|

|

|

|

|

0 |

|

|

|

|

|

1 |

|

|

|

|

|

1 |

|

|

|

|

D3 |

& |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

1 |

|

1 |

0 |

1 |

0 |

|

|

E |

|

1 |

|

|

|

0 |

|

1 |

|

|

|

|

|

|

|

||

1 Q

D3

Q

D3

Рисунок 9 – Логическая схема мультиплексора в базисе И-ИЛИ-НЕ

Условное графическое обозначение дешифратора с инверсными выходами представлено на рисунке 10.

Продолжение таблицы А.1

|

1 |

2 |

3 |

|

– двоично-десятичный |

BCD |

Binary Coded Decimal |

|

– восьмеричный |

OCT |

Octal |

|

– шестнадцатеричный |

HEX |

Hexadecimal |

|

– код Грея |

GRAY |

|

|

– семисегментный |

7SEG |

|

11 |

Приемопередатчик шинный |

RTX |

Receiver Transmitter |

12 |

Регистр |

RG |

Register |

|

сдвиговый регистр |

SRG |

Shift Register |

|

n-разрядный |

|

|

13 |

Сумматор |

SM |

Summator |

14 |

Счетчик |

CTR |

Counter |

|

счетчик n-разрядный |

CTRn |

|

|

счетчик по модулю n |

CTRDIVn |

|

15 |

Триггер |

T |

Toggle flip-flop |

|

двухступенчатый триггер |

TT |

|

16 |

Умножитель |

MPL |

Multiplier |

17 |

Усилитель |

|

|

18 |

Устройство арифметико- |

ALU |

Arithmetic-Logic Unit |

|

логическое |

|

|

19 |

Шина |

BUS |

Bus |

20 |

Шифратор |

CD |

Coder |

21 |

Элемент задержки |

DEL |

Delay |

22 |

Элемент логический: |

=1 |

|

|

– «исключающее ИЛИ» |

|

|

|

– «логическое ИЛИ» |

≥1 или 1 |

|

|

– «логическое И» |

& |

|

23 |

Элемент монтажной логики: |

1◊ |

|

|

– «монтажное ИЛИ» |

|

|

|

– «монтажное И» |

&◊ |

|

24 |

Элемент нелогический: |

* |

|

|

– стабилизатор напряжения |

*STU |

|

|

– стабилизатор тока |

&STI |

|

25 |

Наборы нелогических эле- |

|

|

|

ментов: |

*R |

|

|

– резисторов |

|

|

|

– конденсаторов |

*C |

|

30 |

79 |