Электроника Коллектив кафедры Электроника, БГУИР 2014 (Мет пособие)

.pdf

2 |

Вычислительное устройство |

CPU |

Central Processor Unit |

3 |

Вычитатель |

SUB |

Subtractor |

4 |

Делитель |

DIV |

Divisor |

5 |

Демультиплексор |

DX |

Demultiplexer |

6 |

Дешифратор |

DC |

Decoder |

7 |

Микропроцессор |

MPU |

Microprocessor Unit |

8 |

Мультиплексор |

MUX |

Multiplexer |

9 |

Программируемая логическая |

PLM |

|

|

матрица |

X/Y |

|

10 Преобразователь |

|

||

|

Примечание – Буквы X и Y |

|

|

|

могут быть заменены обо- |

|

|

|

значениями представляемой |

|

|

|

информации на входах и |

|

|

|

выходах преобразователя, |

|

|

|

например: |

или A |

|

|

– аналоговый |

|

|

|

– цифровой |

# или D |

Binary |

|

– двоичный |

BIN |

|

|

– десятичный |

DEC |

Decimal |

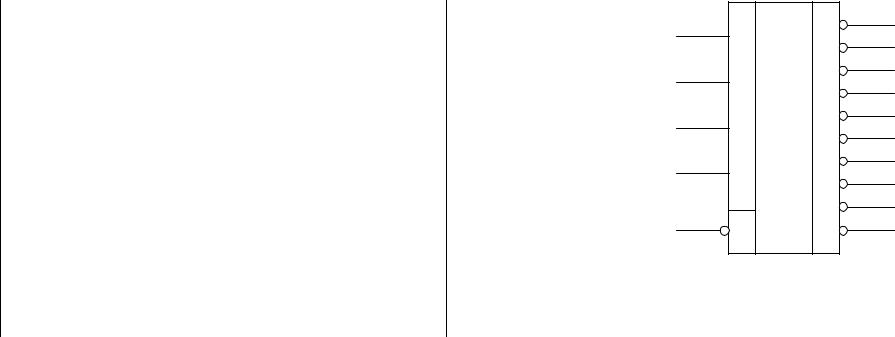

X1 |

1 |

0 |

Y0 |

|

1 |

Y1 |

|||

|

|

|||

X2 |

2 |

2 |

Y2 |

|

3 |

Y3 |

|||

|

|

|||

X4 |

4 |

4 |

Y4 |

|

5 |

Y5 |

|||

|

|

|||

X8 |

8 |

6 |

Y6 |

|

7 |

Y7 |

|||

|

|

|||

|

|

8 |

Y8 |

|

|

E |

9 |

Y9 |

Рисунок 10 – Условное графическое обозначение дешифратора кода 8421 на десять выходов в базисе И-НЕ со стробированием

В дешифраторах с инверсными выходами активным уровнем сигнала на выходах является уровень логического нуля.

Таблица истинности дешифратора представлена в таблице 10.

Таблица 10 – Таблица истинности дешифратора кода 8421 на десять выходов со стробированием

Входной код |

Строб (раз- |

|

|

|

Выходные сигналы |

|

|

|

||||||||||

|

8421 |

|

решение) |

|

|

|

|

|

|

|

|

|

|

|

|

|||

X8 |

X4 |

X2 |

X1 |

|

|

|

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

|

Y7 |

Y8 |

Y9 |

|

|

E |

|||||||||||||||||

X |

X |

X |

X |

1 |

|

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

|

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

|

1 |

1 |

1 |

0 |

|

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

|

1 |

1 |

0 |

|

78 |

31 |

Из таблицы истинности следует, что дешифратор преобразует входной код в сигнал активного уровня на одном из выходов, если на

стробирующем входе активный уровень сигнала ( E = 0). В противном случае на всех выходах дешифратора устанавливаются пассивные уровни сигнала (единичные).

По данным таблицы 10 запишем логические функции для выходов дешифратора в СКНФ:

Y0 X8 X4 |

X2 X1 |

E; |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Y1 X8 X4 |

X2 X1 |

|

||||||||||

E; |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

(7) |

|

Y2 X8 X4 |

X 2 X1 |

|||||||||||

E; |

||||||||||||

... |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Y9 X 8 X4 X2 X1 E. |

|

|||||||||||

Преобразуем логические функции (7) в базис И-НЕ, используя закон двойного отрицания и правило де Моргана:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

X |

8 |

X |

4 |

X |

2 |

X E |

|

X |

8 |

X |

4 |

X |

2 |

X |

1 |

E |

|

|

|||||||||||||||||||||||||||||||||||

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

8 | |

|

|

|

4 | |

|

|

|

2 | |

|

1 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

X |

X |

X |

X |

E; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

... |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(8) |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y9 |

X |

8 X4 X2 |

X |

1 E X 8 |

X |

4 |

X |

2 X1 |

E |

|

|

|

|||||||||||||||||||||||||||||||||||||||||

|

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

| X |

|

| X |

|

| X | E. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

8 |

4 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

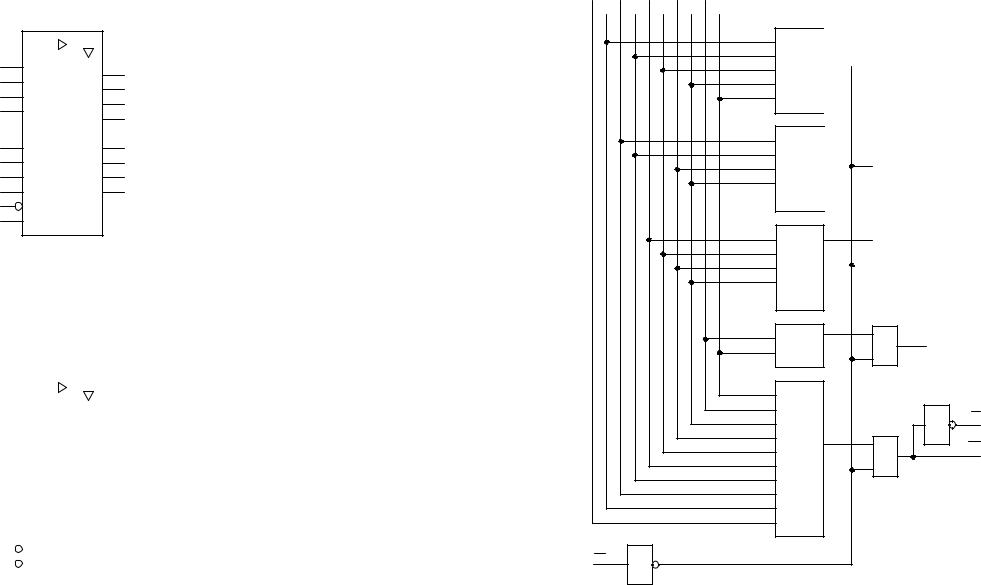

Логическая схема дешифратора в базисе И-НЕ, построенная по логическим функциям (8), представлена на рисунке 11.

Следует помнить, что в дешифраторах с прямыми выходами активным уровнем сигнала на выходах является уровень логической единицы и логические функции следует записывать в СДНФ.

Поскольку на рисунке 11 представлена упрощенная логическая схема дешифратора, то проверку правильности ее функционирования выполним не для четвертой, а для десятой строки таблицы истинности. Так как активный уровень сигнала устанавливается на выходе Y9 ,

то схема дешифратора функционирует в соответствии с таблицей истинности.

www.reshuzadachi.ru

Рисунок В.35 – Восьмиканальный двунаправленный приемопередатчик с тремя состояниями на выходе

ЛИТЕРАТУРА

1 Калабеков, Б. А. Цифровые устройства и микропроцессорные системы : учеб. для техникумов связи / Б. А. Калабеков. – М. : Горячая линия – Телеком, 2002. – 336 с.

2Калабеков, Б. А. Цифровые устройства и микропроцессорные системы : учеб. для техникумов связи / Б. А. Калабеков, И. А. Мамзелев. – М. : Радио и связь, 1987. – 400 с.

3Лысиков, Б. Г. Цифровая и вычислительная техника : учеб. для техникумов связи / Б. Г. Лысиков. – Мн. : УП Экоперспектива, 2002. – 264 с.

4Угрюмов, Е. П. Цифровая схемотехника : учеб. пособие для вузов / Е. П. Угрюмов. – Спб. : БХВ-Петербург, 2002. – 582 с.

5Цифровые интегральные микросхемы : справочник, 2-е изд., перераб. и доп. / М. И. Богданович [и др.]. – Мн. : Беларусь,

Полымя, 1996. – 605 с.

ПРИЛОЖЕНИЕ А (справочное)

Обозначение функций цифровых элементов и назначения выводов по ГОСТ 2.743-91

Обозначение функций, выполняемых цифровым элементом, образуют из прописных букв латинского алфавита, арабских цифр и специальных знаков, записанных без пробелов в верхней части основного поля УГО. Обозначения основных функций цифровых элементов приведены в таблице А.1.

Таблица А.1 – Обозначение основных функций цифровых элементов по ГОСТ 2.743-91

Наименование |

Обозначение |

Исходное название |

1 |

2 |

3 |

1 Буфер |

BUF |

|

32

IN74AC620/IN74ACT620/IN74HC620A/IN74HCT620A (1554АП25/1594АП25/1564АП25/5564АП25)

|

8 RTX |

B |

|

Таблица истинности |

|

|||||

|

A |

|

|

|

|

|

|

|

||

2 |

< > |

< > |

18 |

|

Входы управления |

Операция |

||||

|

0 |

0 |

|

|

EN |

A/B |

|

|||

3 |

17 |

|

|

|||||||

1 |

1 |

|

|

|||||||

|

|

|

|

|

|

|

Данные передаются |

|||

4 |

16 |

|

|

|

|

|

||||

2 |

2 |

|

|

|

|

|

||||

5 |

15 |

|

0 |

|

0 |

с шины B на шину A |

||||

3 |

3 |

|

|

|||||||

6 |

14 |

|

|

|

|

|

(инвертированные) |

|||

4 |

4 |

|

|

|

|

|

||||

7 |

13 |

|

|

|

|

|

|

|||

|

|

|

|

|

Данные передаются |

|||||

5 |

5 |

|

|

|

|

|

||||

8 |

12 |

|

|

|

|

|

||||

6 |

6 |

|

1 |

|

1 |

с шины A на шину B |

||||

9 |

11 |

|||||||||

7 |

7 |

|

|

|

|

|

(инвертированные) |

|||

|

|

|

|

|

|

|

||||

1 |

A/B |

|

|

|

1 |

|

0 |

Шины изолированы |

||

|

|

|

||||||||

19 |

EN |

|

|

|

0 |

|

1 |

(третье состояние) |

||

|

|

|

|

|

|

|

|

|

|

|

20 – питание; 10 – общий.

Рисунок В.34 – Восьмиканальный двунаправленный приемопередатчик с тремя состояниями и инверсией на выходе

IN74AC623/IN74ACT623/IN74HC623A/IN74HCT623A (1554АП26/1594АП26/1564АП26/5564АП26)

|

|

A |

8 RTX |

|

|

Таблица истинности |

|

|||

|

|

B |

|

|

|

|

|

|

|

|

|

2 |

< > |

< B > |

18 |

|

Входы управления |

Операция |

|||

|

|

0 |

0 |

|

|

|

|

|

|

|

|

3 |

17 |

|

EN |

A/B |

|||||

|

1 |

1 |

|

|

||||||

4 |

16 |

|

||||||||

|

2 |

2 |

|

0 |

|

0 |

Данные передаются |

|||

|

5 |

15 |

|

|

||||||

3 |

3 |

|

|

с шины B на шину A |

||||||

|

6 |

14 |

|

|

|

|

|

|||

4 |

4 |

|

|

|

|

|

|

|||

|

|

|

|

|

Данные передаются |

|||||

7 |

13 |

|

1 |

|

1 |

|||||

5 |

5 |

|

|

|||||||

|

8 |

12 |

|

|

с шины A на шину B |

|||||

|

6 |

6 |

|

|

|

|

|

|||

9 |

11 |

|

|

|

|

|

||||

|

7 |

7 |

|

1 |

|

0 |

Шины изолированы |

|||

|

|

|

||||||||

|

1 |

A/B |

|

|

|

0 |

|

1 |

(третье состояние) |

|

19 |

|

|

|

|||||||

EN |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 – питание; 10 – общий. |

|

|

|

|

|

|||||

76 |

|

|

|

|

|

|

|

|

|

|

X8 X4 X2 X1

X8 X4 X2 X1

0 &

1

1

0

1

1 &

1

1

0

1

...

1 &

1

1

1

1

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

E

1 E

0 1

Y0

1

Y1

1

...

Y9

0

Рисунок 11 – Логическая схема дешифратора кода 8421 на десять выходов в базисе И-НЕ со стробированием

33

Синтез логической схемы дешифратора, заданного в вариантах 3, 5 и 9, следует выполнять по вышеприведенной методике. При составлении таблицы истинности заданного дешифратора используются данные таблицы 8. Логические функции записываются для всех

выходов дешифратора, и строится полная логическая схема.

В вариантах 4 и 7 задачи 3 требуется синтезировать схему шифратора. В учебниках [1, С. 110-112] и [2, С. 181-184] показан пример синтеза двоичного шифратора десятичных цифр от 0 до 9 в код 8421 без стробирования. Рассмотрим пример синтеза шифратора десятичных цифр от 0 до 9 в код 8421 со стробированием.

Условное графическое обозначение шифратора для преобразования десятичных цифр от 0 до 9 в код 8421 с разрешающим (стробирующим) входом представлено на рисунке 12.

Y |

|

|

0 |

|

G |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|||

Y10 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Y2 |

|

|

2 |

|

1 |

|

|

X1 |

|

|

|

|

|

|

|||||

Y3 |

|

|

3 |

|

|

|

|||

|

|

||||||||

Y |

|

|

4 |

|

|

|

|

X2 |

|

|

|

|

|

|

|

||||

Y4 |

|

|

5 |

|

2 |

|

|

||

|

|

|

|

|

|||||

|

|

||||||||

Y5 |

|

|

6 |

|

|

|

|

X3 |

|

|

|

|

|

|

|

||||

Y76 |

|

|

7 |

|

4 |

|

|

||

|

|

|

|

|

|||||

|

|

||||||||

Y8 |

|

|

8 |

|

8 |

|

|

X4 |

|

|

|

|

|

|

|||||

Y9 |

|

|

9 |

|

|

|

|||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EI |

|

E0 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Рисунок 12 – Условное графическое обозначение шифратора для преобразования десятичных цифр от 0 до 9 в код 8421

Сигналы, соответствующие десятичным цифрам, подаются на входы Y0 , Y1 ,…, Y9.

Нулевое значение сигнала на разрешающем (стробирующем) вхо-

де EI разрешает работу данного шифратора. Нулевое значение сигна-

IN74AC258/IN74ACT258/IN74HC258A (1554КП14/1594КП14/1564КП14)

Таблица истинности

Входы |

|

|

Выходы |

||||

SEL |

|

EN |

|

Y0 – Y3 |

|||

X |

|

1 |

|

|

Z |

||

0 |

|

0 |

|

|

|

|

|

|

|

|

A0 - A3 |

|

|

||

1 |

|

0 |

|

|

|

|

|

|

|

|

B0 - B3 |

|

|||

16 – питание; 8 – общий.

Рисунок В.32 – Четыре селектора-мультиплексора 2-1 с тремя состояниями и инверсией на выходе

IN74HC283A/IN74HCT283A (1564ИМ6/5564ИМ6)

|

|

|

|

Таблица истинности |

|

|

|||||

5 |

A |

SM |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|||

0 |

|

|

|

|

|

|

|

|

|

||

3 |

|

|

|

|

Входы |

|

|

Выходы |

|||

1 |

|

|

|

|

|

|

|||||

14 |

|

|

|

|

|

|

|||||

2 |

S |

|

|

An |

Bn |

CI |

|

Sn |

C0 |

||

12 |

4 |

||||||||||

3 |

0 |

|

0 |

0 |

0 |

|

0 |

0 |

|||

|

1 |

||||||||||

|

B |

1 |

|

0 |

0 |

1 |

|

1 |

0 |

||

|

13 |

|

|

||||||||

6 |

2 |

|

|

|

|

|

|

|

|||

|

0 |

1 |

0 |

|

1 |

0 |

|||||

0 |

10 |

|

|

||||||||

2 |

3 |

|

|

||||||||

|

0 |

1 |

1 |

|

0 |

1 |

|||||

1 |

|

|

|

||||||||

15 |

|

|

|||||||||

2 |

|

|

|

1 |

0 |

0 |

|

1 |

0 |

||

11 |

|

|

|

|

|||||||

3 |

|

9 |

|

1 |

0 |

1 |

|

0 |

1 |

||

7 |

|

|

|

||||||||

CI |

C0 |

|

1 |

1 |

0 |

|

0 |

1 |

|||

|

|

||||||||||

|

|

|

|

|

1 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

||||||||

16 – питание; 8 – общий.

Рисунок В.33 – Четырехразрядный двоичный сумматор с ускоренным переносом

75

34

IN74AC253/IN74ACT253/IN74HC253A (1554КП12/1594КП12/1564КП12)

Таблица истинности

|

|

|

Входы |

|

Выходы |

|

|

|

A1 |

A0 |

Y |

EN |

|||||

1 |

|

X |

X |

Z |

|

0 |

|

0 |

0 |

D0 |

|

0 |

|

0 |

1 |

D1 |

|

0 |

|

1 |

0 |

D2 |

|

0 |

|

1 |

1 |

D3 |

|

16 – питание; 8 – общий.

Рисунок В.30 – Два селектора-мультиплексора 4-1 с тремя состояниями на выходе

IN74AC257/IN74ACT257/IN74HC257A (1554КП11/1594КП11/1564КП11)

Таблица истинности

Входы |

|

|

Выходы |

|

SEL |

|

|

|

Y0 – Y3 |

EN |

||||

X |

|

1 |

|

Z |

0 |

|

0 |

|

A0 – A3 |

1 |

|

0 |

|

B0 – B3 |

16 – питание; 8 – общий.

Рисунок В.31 – Четыре селектора-мультиплексора 2-1 с тремя состояниями на выходе

74

ла на выходе G отмечает наличие возбужденного входа у данного шифратора.

Чтобы выделить ситуацию, когда отсутствуют возбужденные вхо-

ды, в данном шифраторе имеется дополнительный выход E0 (разре-

шение по выходу). Нулевое значение сигнала на выходе E0 вырабатывается при отсутствии возбужденных входов у данного шифратора для разрешения работы следующего (младшего) шифратора при наращивании числа входов и выходов.

На выходах X4 – X1 формируется выходное кодовое слово.

Таблица истинности, описывающая функционирование данного шифратора, представлена в таблице 11.

Таблица 11 – Таблица истинности шифратора для преобразования десятичных цифр от 0 до 9 в код 8421

Входные сигналы |

|

|

|

|

|

|

|

|

|

Выходные сигналы |

|

|

|

|

|||||||||

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

Y8 |

Y9 |

|

|

|

X4 |

X3 |

X2 |

X1 |

|

|

|

|

|

|

|

EI |

|

G |

E0 |

||||||||||||||||||||

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

|

||||||

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

|

1 |

|

0 |

|

|

1 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

|

0 |

|

1 |

|

|

0 |

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

1 |

|

0 |

|

1 |

|

|

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

1 |

0 |

|

0 |

|

1 |

|

|

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

1 |

1 |

|

0 |

|

1 |

|

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

0 |

|

0 |

|

1 |

|

|

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

|

0 |

|

1 |

|

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

1 |

0 |

|

0 |

|

1 |

|

|

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

|

0 |

1 |

1 |

1 |

|

0 |

|

1 |

|

|

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

|

1 |

0 |

0 |

0 |

|

0 |

|

1 |

|

|

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

|

1 |

0 |

0 |

1 |

|

0 |

|

1 |

|

|

Как видно из таблицы истинности, все вышеперечисленные сигналы на выходах шифратора формируются при наличии активного

уровня сигнала на входе разрешения ( EI = 0). При пассивном уровне

сигнала на входе разрешения ( EI = 1) независимо от состояния информационных входов шифратора на информационных выходах формируется кодовое слово 0000 и пассивные уровни сигналов на выходах

G и E0 .

35

При отсутствии возбужденных входов (вторая строка в таблице

истинности) на выходе E0 формируется активный уровень сигнала

( E0 = 0).

По данным таблицы 11 запишем логические функции для информационных выходов шифратора. Каждая из них представляет дизъ-

юнкцию входных аргументов Y |

(i = 0, 1, … , 9), для которых значение |

|||||||||||||||||||

функции равно 1. |

|

i |

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||

X1 |

|

|

|

|

|

(Y1 Y3 Y5 Y7 Y9 ); |

|

|

|

|

|

|

||||||||

EI |

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X2 EI (Y2 Y3 Y6 Y7 ); |

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X3 EI (Y4 Y5 Y6 Y7 ); |

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

(9) |

|||||||||||||

X4 |

|

|

|

(Y8 Y9 ); |

|

|

|

|

|

|

|

|

||||||||

EI |

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

(Y |

Y |

Y |

Y Y |

Y |

Y |

Y |

Y |

Y ); |

|

||||||

E0 |

EI |

|

||||||||||||||||||

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G E0. |

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

Из таблицы истинности очевидно, что логическая функция для

выхода G является инверсией логической функции для выхода E0 . Логическая схема шифратора в базисе И, ИЛИ НЕ, построенная по

логическим функциям (9), представлена на рисунке 13.

Для проверки правильности функционирования логической схемы шифратора подадим на ее входы сигналы, соответствующие четвертой строке таблицы истинности ( Y3 = 1). Так как на выходах устанавлива-

ется кодовое слово 0011, а так же G = 0, E0 = 1, то логическая схема шифратора функционирует в соответствии с таблицей истинности.

Синтез логической схемы шифратора, заданного в вариантах 4 и 7, следует выполнять по вышеприведенной методике. При составлении таблицы истинности в качестве выходного кода X4 , X3 , X2 , X1 ис-

пользовать данные таблицы 8.

IN74AC245/IN74ACT245/IN74HC245A/IN74HCT245A (1554АП6/1594АП6/1564АП6/5564АП6)

Таблица истинности

Входы управления |

Операция |

||||

EN |

A/B |

||||

|

|||||

1 |

|

X |

Шины изолированы |

||

|

(третье состояние) |

||||

|

|

|

|

||

0 |

|

0 |

Данные передаются с |

||

|

шины B на шину A |

||||

|

|

|

|

||

0 |

|

1 |

Данные передаются с |

||

|

шины A на шину B |

||||

|

|

|

|

||

20 – питание; 10 – общий.

Рисунок В.28 – Восьмиканальный двунаправленный шинный формирователь (приемо-передатчик шинный)

IN74AC251/IN74ACT251/IN74HC251A/IN74HCT251A (1554КП15/1594КП15/1564КП15/5564КП15)

|

|

|

|

|

|

|

|

|

Таблица истинности |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

Выходы |

|||||||||||

|

|

|

|

|

|

|

|

|

EN |

A2 |

A1 |

A0 |

Y |

|

|

Y |

|||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

1 |

|

X |

X |

X |

Z |

|

|

|

Z |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

0 |

0 |

D0 |

|

|

D0 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

0 |

|

0 |

0 |

1 |

D1 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

Y |

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

0 |

|

0 |

1 |

0 |

D2 |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

D2 |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

1 |

1 |

D3 |

|

D3 |

|

||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

0 |

|

1 |

0 |

0 |

D4 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

D4 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

0 |

|

1 |

0 |

1 |

D5 |

|

|

D5 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

1 |

0 |

D6 |

|

|

D6 |

|

|

||||||

16 – питание; 8 – общий. |

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

0 |

|

1 |

1 |

1 |

D7 |

|

D7 |

||||||||||||||||||

Рисунок В.29 – Селектор-мультиплексор 8-1 с тремя состояниями на выходе

73

36

IN74AC241/IN74ACT241/IN74HC241A/IN74HCT241A (1554АП4/1594АП4/1564АП4/5564АП4)

Таблица истинности

|

Входы |

Выходы |

Входы |

Выходы |

|||

|

|

|

An |

Ya |

ENb |

Bn |

Yb |

ENa |

|||||||

1 |

|

X |

Z |

0 |

X |

Z |

|

0 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

|

1 |

1 |

1 |

1 |

1 |

|

20 – питание; 10 – общий.

Рисунок В.26 – Два четырехканальных шинных формирователя с тремя состояниями на выходе

IN74AC244/IN74ACT244/IN74HC244A/IN74HCT244A (1554АП5/1594АП5/1564АП5/5564АП5)

|

|

|

|

|

Таблица истинности |

|

||||||

2 |

|

A |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

0 |

|

18 |

|

|

|

|

|

|

|

|

|

4 |

|

Y0a |

|

|

|

|

Входы |

Выходы |

||||

|

1 |

16 |

|

|

|

|

||||||

6 |

|

2 |

Y1a |

14 |

|

ENa, |

ENb |

An, Bn |

Yn |

|||

8 |

|

Y2a |

|

|||||||||

|

3 |

12 |

|

1 |

|

|

X |

Z |

||||

|

|

Y3a |

|

|

|

|||||||

|

|

|

|

|||||||||

11 |

|

B |

9 |

|

0 |

|

|

0 |

0 |

|||

|

|

|

|

|||||||||

|

0 |

Y0b |

|

0 |

|

1 |

1 |

|||||

13 |

|

7 |

||||||||||

|

1 |

Y1b |

|

|

|

|

|

|

|

|

||

15 |

|

5 |

|

|

|

|

|

|

|

|

||

|

2 |

Y2b |

|

|

|

|

|

|

|

|

||

17 |

|

3 |

|

|

|

|

|

|

|

|

||

|

3 |

Y3b |

|

|

|

|

|

|

|

|

||

1 |

|

|

|

|

|

|

|

|

|

|

||

|

ENa |

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

ENb |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 – питание; 10 – общий.

Рисунок В.27 – Два четырехканальных шинных формирователя с тремя состояниями на выходе

72

Y0 Y1 Y2 Y3Y4 Y5 Y6 Y7 Y8 Y9

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0

1

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

EI 1 1 0

1

1

1

1

1

1 |

|

|

|

|

|

& |

1 |

X1 |

|||

1 |

|||||

|

|||||

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

& |

1 |

X2 |

||

1 |

||||

|

||||

|

|

|||

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

& |

0 |

X3 |

|||

1 |

|||||

|

|||||

|

|

||||

|

|

|

|

|

|

0 |

& |

0 |

X4 |

|

|

|

|||

|

1 |

|

||

|

|

|

||

|

|

|

1 |

G |

|

|

|

|

|

1 |

& |

|

|

0 E0 |

|

1 |

|

1 |

|

|

|

|

|

Рисунок 13 – Логическая схема шифратора для преобразования десятичных цифр от 0 до 9 в код 8421 в базисе И, ИЛИ, НЕ со стробированием

37

Контрольная задача 4

Синтезировать цифровой автомат с двумя состояниями, выбрав свой вариант из таблицы 2.3.

Таблица 2.3 Варианты цифровых автоматов для синтеза

Вари- |

Синтезируемый |

Структурный базис для синте- |

|

цифровой авто- |

|||

ант |

мат |

за |

|

|

|

||

0 |

RS-триггер |

D-триггер и логические эле- |

|

менты НЕ, И, ИЛИ. |

|||

|

|

||

1 |

D-триггер |

RS-триггер и логические |

|

элементы НЕ, И, ИЛИ |

|||

|

|

||

2 |

T-триггер |

D-триггер и логические эле- |

|

менты НЕ, И, ИЛИ |

|||

|

|

||

3 |

JK-триггер |

D-триггер и логические эле- |

|

менты НЕ, И, ИЛИ |

|||

|

|

||

4 |

JK-триггер |

RS-триггер и логические |

|

элементы НЕ, И, ИЛИ |

|||

|

|

||

5 |

Т-триггер |

RS-триггер и логические |

|

элементы НЕ, И, ИЛИ |

|||

|

|

||

6 |

D-триггер |

JK-триггер и логические |

|

элементы НЕ, И, ИЛИ |

|||

|

|

||

7 |

T-триггер |

D-триггер и логические эле- |

|

менты НЕ, И, ИЛИ |

|||

|

|

||

8 |

RS-триггер |

T-триггер и логические эле- |

|

менты НЕ, И, ИЛИ |

|||

|

|

||

9 |

D-триггер |

T-триггер и логические эле- |

|

менты НЕ, И, ИЛИ |

|||

|

|

IN74AC158/IN74ACT158/IN74HC158A (1554КП18/1594КП18/1564КП18)

2 |

|

|

|

|

Таблица истинности |

|

|

|

|||||

A0 MUX |

|

|

|

|

|

|

|||||||

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

A1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

|

|

|

|

|

Входы |

Выходы |

||||||

A2 |

|

|

|

|

|

||||||||

14 |

A3 |

Y0 |

|

4 |

|

SEL |

|

EN |

Y0 – Y3 |

||||

|

|

|

|||||||||||

3 |

|

|

7 |

|

X |

|

1 |

|

1 |

|

|||

B0 |

Y1 |

|

|

|

|

||||||||

6 |

|

9 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|||||

B1 |

Y2 |

|

0 |

|

0 |

|

A0 - A3 |

||||||

10 |

12 |

|

|

|

|||||||||

B2 |

Y3 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

1 |

|

0 |

|

|

B0 - B3 |

||||

13 |

|

|

|

|

|

|

|||||||

B3 |

|

|

|

|

|

|

|

||||||

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

SEL |

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 – питание; 8 – общий.

Рисунок В.24 – Четыре селектора-мультиплексора 2-1 со стробированием и инверсией на выходе

IN74AC240/IN74ACT240/IN74HC240A/IN74HCT240A (1554АП3/1594АП3/1564АП3/5564АП3)

Таблица истинности

|

|

|

Входы |

Выходы |

||

|

ENa, ENb |

An, Bn |

Yn |

|||

1 |

|

|

X |

Z |

||

0 |

|

|

0 |

1 |

||

0 |

|

|

1 |

0 |

||

20 – питание; 10 – общий.

Рисунок В.25 – Два четырехканальных шинных формирователя с тремя состояниями и инверсией на выходе

71

38

IN74HC155A/IN74HCT155A (1564ИД4/5564ИД4)

Таблица истинности

Адрес |

Разреш. |

|

Выходы |

|

Разреш. |

|

Выходы |

|

|||||||||||||||

|

|

«a» |

|

|

«a» |

|

|

|

«b» |

|

|

«b» |

|

||||||||||

A1 |

A0 |

Ea |

|

Ea |

Y0 |

Y1 |

Y2 |

Y3 |

|

Eb |

|

Eb |

Y0 |

Y1 |

Y2 |

Y3 |

|||||||

X |

X |

0 |

X |

1 |

|

1 |

1 |

|

1 |

1 |

|

X |

1 |

|

1 |

1 |

|

1 |

|||||

X |

X |

X |

|

1 |

1 |

1 |

1 |

1 |

|

X |

1 |

1 |

1 |

1 |

1 |

||||||||

0 |

0 |

1 |

|

0 |

0 |

|

1 |

1 |

|

1 |

0 |

0 |

0 |

|

1 |

1 |

|

1 |

|||||

0 |

1 |

1 |

|

0 |

1 |

|

0 |

1 |

|

1 |

0 |

0 |

1 |

|

0 |

1 |

|

1 |

|||||

1 |

0 |

1 |

|

0 |

1 |

|

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

|

1 |

|||||

1 |

1 |

1 |

|

0 |

1 |

|

1 |

1 |

|

0 |

0 |

0 |

1 |

|

1 |

1 |

|

0 |

|||||

16 – питание; 8 – GND.

Рисунок В.22 – Два дешифратора-демультиплексора 2-4 с инверсией на выходе

IN74AC157/IN74ACT157/IN74HC157A/IN74HCT157A (1554КП16/1594КП16/1564КП16/5564КП16)

Таблица истинности

Входы |

|

|

Выходы |

|

SEL |

|

|

|

Y0 – Y3 |

EN |

||||

X |

|

1 |

|

0 |

0 |

|

0 |

|

A0 - A3 |

1 |

|

0 |

|

B0 - B3 |

16 – питание; 8 – общий.

Рисунок В.23 – Четыре селектора-мультиплексора 2-1 со стробированием

70

Методические указания к решению задачи 4

Для решения задачи 4 требуется знание раздела 9 программы. Пусть требуется синтезировать цифровой автомат Мура в структурном базисе, состоящем из элемента памяти – линии задержки (ЛЗ), и функционально полного логического элемента ИЛИ–НЕ. ЛЗ задается ее таблицей переходов (см. таблицу 3.3).

Таблица 3.3 Таблица переходов элемента памяти (ЛЗ)

D |

Q0 |

Q1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

Где Q0 состояние ЛЗ в нулевом такте t0; Q1 состояние ЛЗ в следующем, первом, такте t1; D данные на входе ЛЗ.

Кроме того, заданы параметры абстрактного автомата:

число входных сигналов K = 4;

число внутренних состояний N = 2;

число выходных сигналов M = 2.

Элемент ИЛИ-НЕ задается своей таблицей истинности. Решение. 1-й шаг – находим параметры структурного цифрового

автомата

число входов у автомата k = log K = log 4 = 2;

2 2

число элементов памяти n = log2N = log 2 = 1;

2

число входов у автомата m = log M = log 2 = 1.

2 2

Один из входов будет использоваться для установки автомата в первое, единичное, состояние (обозначается буквой S), а другой – для установки его во второе, нулевое, состояние (обозначается буквой R).

39

40

Таблица истинности

-табислужитьодновременноможет4.3 таблица ,Следовательно .) .ПА возбуждения лицей |

неа(D,переменнойвыходнойобозначениядо точностью с реходов |

R,S,входыиDвыходимееткоторая,КС истинности таблицу есть то( -используетавтоматевпамятиэлементакачестве в поскольку ,Но .) -петаблицейегоссовпадаетпамятиего возбуждения таблица ,ЛЗ ся |

егостроимавтоматасхемыдвухкомпонентнойоснове на – шаг й-2 .4).3 таблицу .см( переходов таблицу автоматапамятивозбуждениятаблицустроить нужно – шаг й-3 |

автоматсинтезируемыйСтруктурный 4.3 Рисунок )автоматапамятьПА,схемакомбинационная КС( |

ПА |

0 |

|

|

R |

КС |

|

автоматасинтезируемогосхемудвухкомпонентнуюстроим Далее .4).3 рисунок .см( |

|

Q |

|

Q |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

69

|

|

Входы |

|

|

|

|

|

|

|

|

|

Выходы |

|

|

|

|

|

|

|

|||

|

|

|

A3 |

A2 |

A1 |

A0 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

Y8 |

Y9 |

Y10 |

Y11 |

Y12 |

Y13 |

Y14 |

Y15 |

0 |

1 |

|

X |

X |

X |

X |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

X |

X |

X |

X |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

X |

X |

X |

X |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Окончание рисунка В.21